目录

1.算法描述

2.仿真效果预览

3.verilog核心程序

4.完整FPGA

1.算法描述

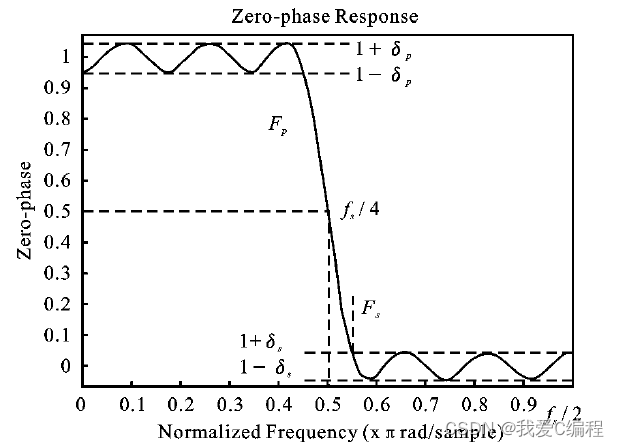

HBF模块由半带滤波器(HBF)和抽取模块组成。该模块的任务是实现2倍抽取进一步降低信号采样速率。由于HBF的冲激响应h(k)除零点外其余偶数点均为零,所以用HBF实现2倍抽取可以节省一半的运算量,对增强软件无线电的实时性非常重要,HBF还具有参数约束少,设计容易、方便的特点。半带滤波器的主要作用是滤除信号高频部分,防止抽取过程后信号发生频谱混叠。

在实际中,需要将输入信号进行多次滤波和抽取,并逐次降低采样率,同时也降低对每一级抗混叠滤波器的要求,所以需要使用半带滤波器进行设计与实现。

阻带衰减: ≥50dB

通带不平坦度:≤2dB

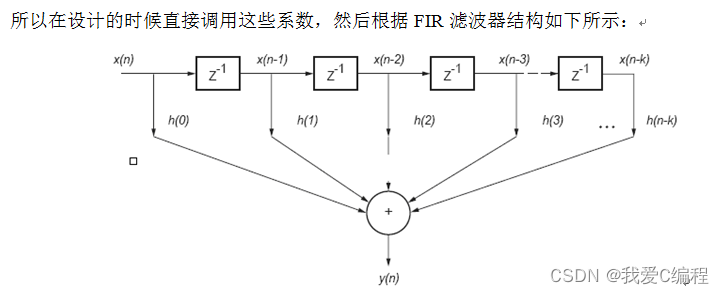

通常情况下,半带滤波器的有三种基本的结构,一般结构,转置结构以及复用结构,下面我们将针对这三种结构的滤波效果以及硬件占用情况进行分析,从而选用最佳的设计方案。

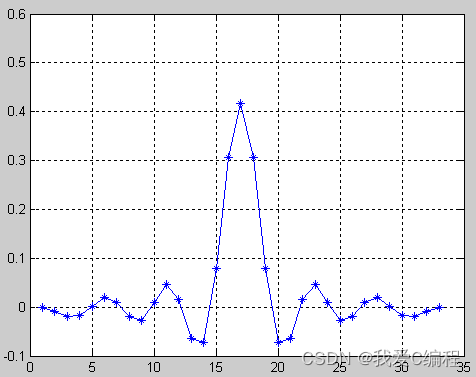

频谱对称性的特点使得半带滤波器的时域冲击响应除极值点以外,在其余所有偶数点都为零,利用该性质,可以将运算量降低一半。

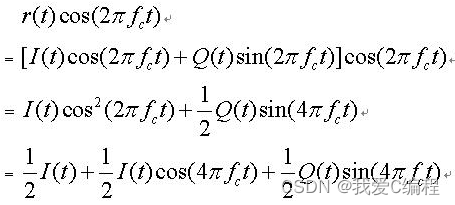

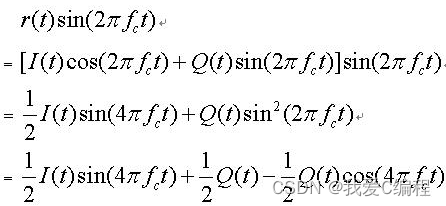

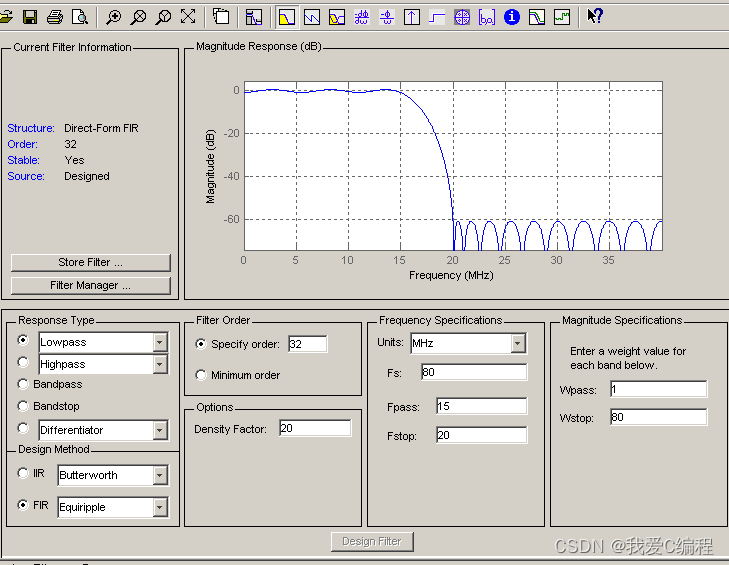

本系统,我们将设计的滤波器,首先,我们可以使用和FIR滤波器设计方法相同的方法进行设计。 根据的设计要求,输入的信号带宽为20M,前面设计的NCO,其载波频率为20M,所以,在进行下变频的时候,会产生两倍的频率分量,具体如下所示:

= = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = =

所以,需要设计一个滤波器,其截止频率可以设定为20M,即大于20M的全部滤除,所以,通过上式,可以将其中的高频分量滤除掉。

此外,由于你的要求中提高通带通带不平坦度≤2dB,那么通常情况下,滤波器的阶数需要设计为中高阶,这里,我们选用65阶的滤波器。

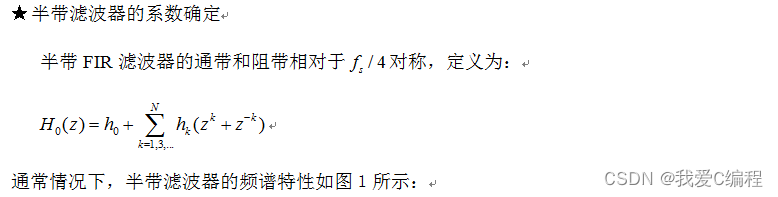

★半带滤波器的一般结构

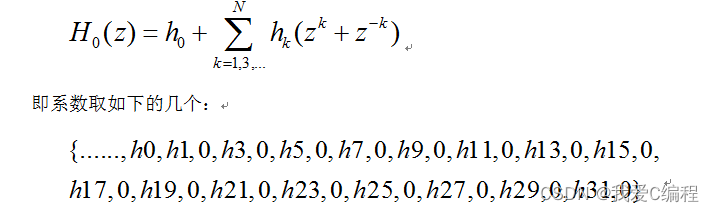

普通滤波器的结构,就是一般的FIR滤波器的结构,只是系数取一般,进行半带滤波,根据半带滤波的表达式,

这个结构式最传统的FIR滤波器的结构,我们首先来进行最简单的结构设计。

然后根据半带滤波器的性质,这里我们只需要做如下的运行进行就可以了。

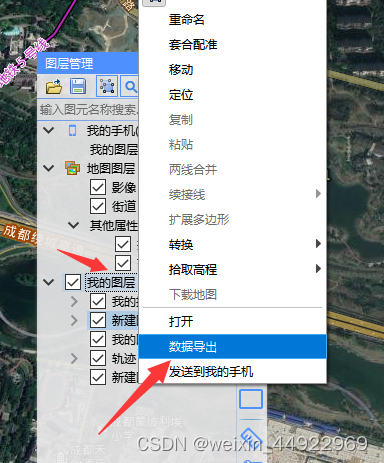

★半带滤波器的复用结构

复用结构比较简单,其主要就是通过计数器来选择不同时刻的h0值,然后

其相关理论知识比较简单,下面我们将在FPGA中实现该算法。

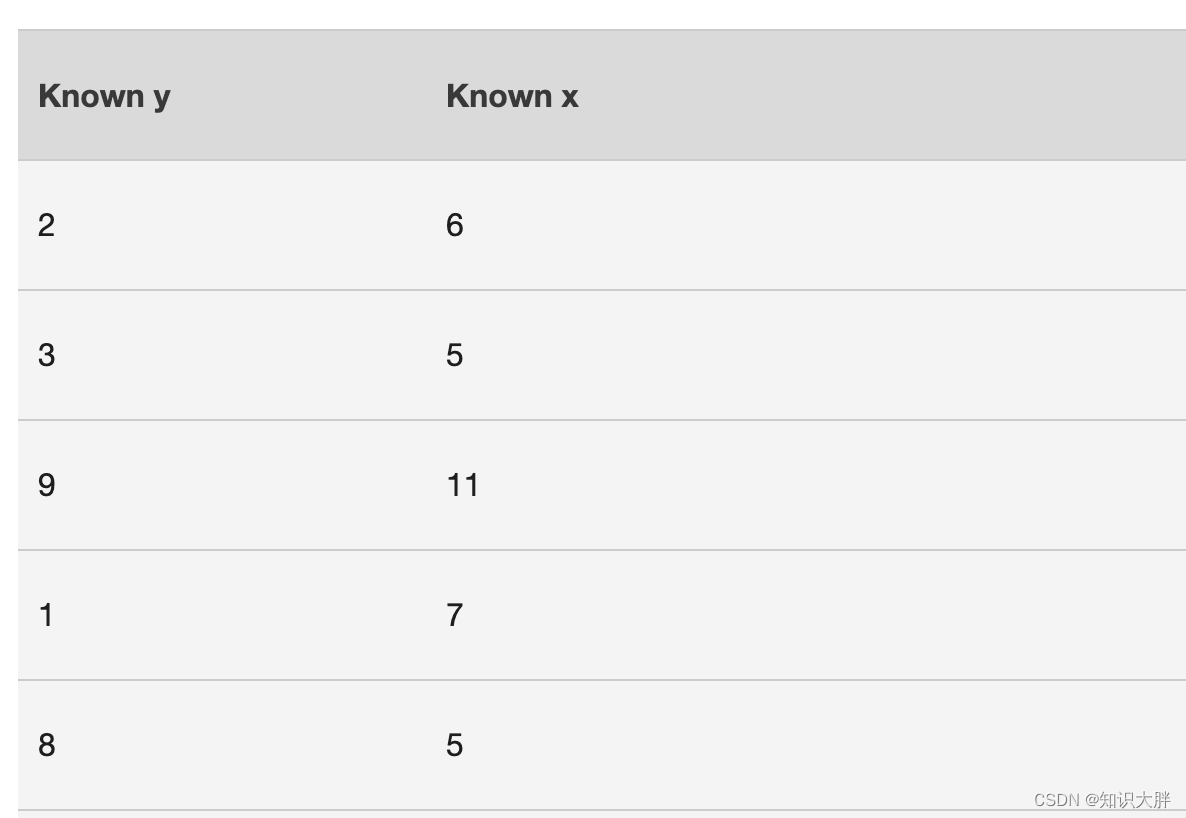

那么这里,我们的滤波器系数为:

(0),(h15 = -624),(0),(h13 = -1175),(0),(h11 = 1238),(0),(h9 = -1238),

(0),(h7 = 667),(0),(h5 = 965),(0),(h3 = -4745),(0),(h1 = 20073),(h0 = 27316),

(h1 = 20073),(0),(h3 = -4745),(0),(h5 = 965),(0),(h7 = 667),

(0),(h9 = -1238),(0),(h11 = 1238),(0),(h13 = -1175),(0),(h15 = -624),(0)

通过一个计数器,来作为按键选择不同时间的不同系数的选择,这里,由于滤波器的系数由33个。即,计数器的值从0到32。而系数为非0的计数器值为

1,3,5,7,9,11,13,15,16,17,19,21,23,25,27,29,31

因此,在FPGA中,我们可以通过设计一个计数器进行乘法器的复用。

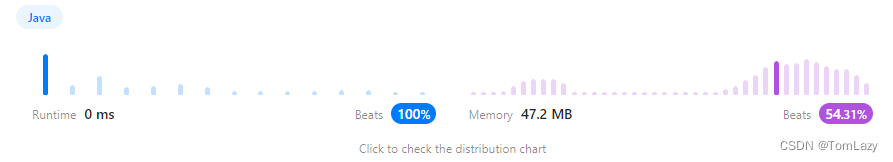

2.仿真效果预览

版本vivado2019.2

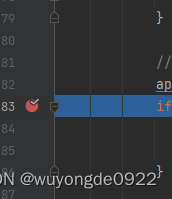

3.verilog核心程序

...........................

//delay 33 units

integer i;

reg signed[15:0]men_delay[33:1];

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

for(i=1;i<=33;i=i+1)

begin

men_delay[i] <= 16'd0;

end

end

else begin

men_delay[1] <= i_din;

for(i=2;i<=33;i=i+1)

begin

men_delay[i] <= men_delay[i-1];

end

end

end

//level 1

reg signed[31:0]reg_adder01[33:1];

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

for(i=1;i<=33;i=i+1)

begin

reg_adder01[i] <= 32'd0;

end

end

else begin

reg_adder01[1] <= 32'd0;

reg_adder01[2] <= h15 * men_delay[2];

reg_adder01[3] <= 32'd0;

reg_adder01[4] <= h13 * men_delay[4];

reg_adder01[5] <= 32'd0;

reg_adder01[6] <= h11 * men_delay[6];

reg_adder01[7] <= 32'd0;

reg_adder01[8] <= h9 * men_delay[8];

reg_adder01[9] <= 32'd0;

reg_adder01[10]<= h7 * men_delay[10];

reg_adder01[11]<= 32'd0;

reg_adder01[12]<= h5 * men_delay[12];

reg_adder01[13]<= 32'd0;

reg_adder01[14]<= h3 * men_delay[14];

reg_adder01[15]<= 32'd0;

reg_adder01[16]<= h1 * men_delay[16];

//============================================================

reg_adder01[17]<= h0 * men_delay[17];

//============================================================

reg_adder01[18]<= h1 * men_delay[18];

reg_adder01[19]<= 32'd0;

reg_adder01[20]<= h3 * men_delay[20];

reg_adder01[21]<= 32'd0;

reg_adder01[22]<= h5 * men_delay[22];

reg_adder01[23]<= 32'd0;

reg_adder01[24]<= h7 * men_delay[24];

reg_adder01[25]<= 32'd0;

reg_adder01[26]<= h9 * men_delay[26];

reg_adder01[27]<= 32'd0;

reg_adder01[28]<= h11 * men_delay[28];

reg_adder01[29]<= 32'd0;

reg_adder01[30]<= h13 * men_delay[30];

reg_adder01[31]<= 32'd0;

reg_adder01[32]<= h15 * men_delay[32];

reg_adder01[33]<= 32'd0;

end

end

//level 2

reg signed[31:0]reg_adder02[9:1];

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

for(i=1;i<=9;i=i+1)

begin

reg_adder02[i] <= 32'd0;

end

end

else begin

reg_adder02[1] <= reg_adder01[2] + reg_adder01[32];

reg_adder02[2] <= reg_adder01[4] + reg_adder01[30];

reg_adder02[3] <= reg_adder01[6] + reg_adder01[28];

reg_adder02[4] <= reg_adder01[8] + reg_adder01[26];

reg_adder02[5] <= reg_adder01[17];

reg_adder02[6] <= reg_adder01[10]+ reg_adder01[24];

reg_adder02[7] <= reg_adder01[12]+ reg_adder01[22];

reg_adder02[8] <= reg_adder01[14]+ reg_adder01[20];

reg_adder02[9] <= reg_adder01[16]+ reg_adder01[18];

end

end

//level 3

reg signed[31:0]reg_adder03[5:1];

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

for(i=1;i<=5;i=i+1)

begin

reg_adder03[i] <= 32'd0;

end

end

else begin

reg_adder03[1] <= reg_adder02[1] + reg_adder02[9];

reg_adder03[2] <= reg_adder02[2] + reg_adder02[8];

reg_adder03[3] <= reg_adder02[3] + reg_adder02[7];

reg_adder03[4] <= reg_adder02[4] + reg_adder02[6];

reg_adder03[5] <= reg_adder02[5];

end

end

//level 4

reg signed[31:0]reg_adder04[3:1];

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

for(i=1;i<=3;i=i+1)

begin

reg_adder04[i] <= 32'd0;

end

end

else begin

reg_adder04[1] <= reg_adder03[1] + reg_adder03[5];

reg_adder04[2] <= reg_adder03[2] + reg_adder03[3];

reg_adder04[3] <= reg_adder03[4];

end

end

//level 5

reg signed[31:0]r_dout = 32'd0;

reg signed[31:0]o_dout = 32'd0;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

r_dout <= 32'd0;

end

else begin

r_dout <= reg_adder04[1] + reg_adder04[2] + reg_adder04[3];

end

end

01_115m 4.完整FPGA

V

![[附源码]计算机毕业设计框架的资产管理系统设计与实现Springboot程序](https://img-blog.csdnimg.cn/22384c510da94237905b6e2baac494d4.png)