2021年4月21日,在芯片界的顶级会议Hot Chips大会上,Cerebras Systems公司发布了一款晶圆级引擎芯片——Wafer Scale Engine 2。

这款芯片采用台积电7纳米工艺制程,拥有85万个AI核心,包含2.6万亿个晶体管,面积为46225平方毫米,基于一整张12英寸的晶圆制造,这是迄今为止包含晶体管数量最多的芯片。

除了这款“巨无霸”,市面上主流的用在智能手机或者个人电脑中的芯片,其晶体管规模都在百亿级。那么数量如天文数字般的晶体管,是如何被设计出来的呢?

“上百亿个晶体管,总不能用手来画吧?”相信很多非业内人士会有类似的困惑。

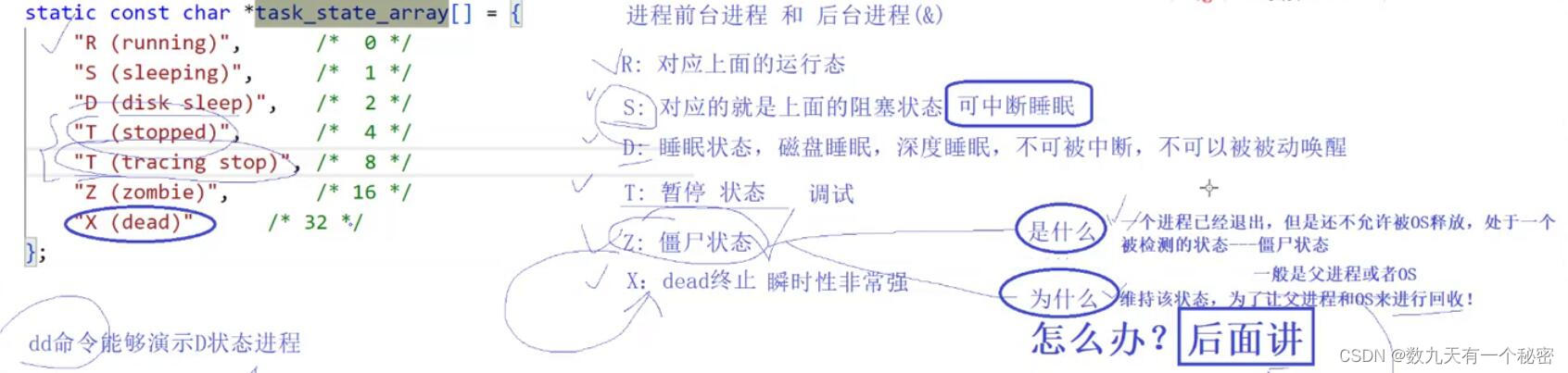

其实在集成电路发展早期,内部的晶体管都是通过手画设计的,彼时芯片的规模较小,只有几十个或者几百个晶体管。但随着芯片的发展和演进,其逻辑功能变得越来越复杂且全面,晶体管的数目也呈指数级增长,此时再徒手画电路,显然是不现实的。随后,计算机辅助设计开始应用于芯片领域。在直接促成百亿级规模的芯片设计这一方面,有三种秘密武器必不可少。

秘密武器之一——使用编程语言来设计芯片的思想

这个思想来自卡沃·米德和林恩·康威的著作《超大规模集成电路系统导论》,它的提出是芯片设计历史上一个非常重要的里程碑。

假设我们要设计一个数据比较器,当输入值a和b相等时,equal的返回值为1;当a和b不相等时,返回值为0。使用Verilog语言,一行代码即可实现。

assign equal = (a==b)? 1 : 0;

但如果徒手画晶体管电路,通过分析以上数据比较器的功能可知,逻辑功能和同或门一致,因此可以用异或门后接一个反相器实现该数据比较器的功能。搭建一个异或门最少需要6个晶体管,一个反相器需要2个晶体管,所以我们用一行代码就完成了8个晶体管的设计,这大幅提高了工程师设计芯片的效率!

这是数字芯片设计中最简单的一个例子,在实际工作中,工程师可以在比较抽象的层次上描述设计电路的结构和逻辑功能,用简洁明确的源代码描述复杂的逻辑功能,并且支持模块化设计和层次化设计。往往由简单的几十行代码设计出来的电路,即可包含成千上万个晶体管。因此,通过编程可以让设计具有百亿级数量晶体管的芯片成为可能。

秘密武器之二——EDA

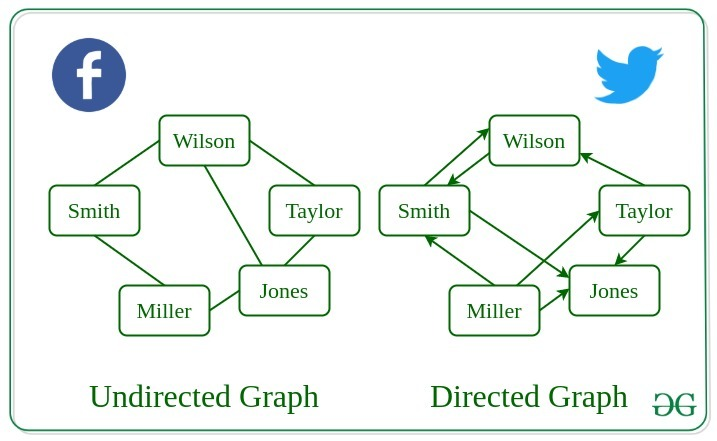

在 RTL 设计完成后,即可采用逻辑综合工具把RTL 转换成门级网表,也就是与、或、非等逻辑门及其之间的连接关系。

将RTL 转换成门级网表的过程主要有三个步骤:翻译、优化和映射。就像自动化流水线一样,只要把原材料放进去,就可以得到成品。

这些纷繁复杂的工作都交给EDA来做,可以明显缩短设计的时间,加快将芯片推向市场的速度。

秘密武器之三——重复调用已有的成熟设计模块

在芯片中,很多单元或模块的数目不止用到一次,比如算术逻辑单元,我们只需设计一次,即可重复调用。

这好比建筑师在设计住宅楼时,只需设计几种标准户型,并不要求每间房屋的户型都是独一无二的设计。

或者从更高层次的角度看,目前的中央处理器都是8核、16核等,这些核心在设计上也几乎是一致的。

尽管芯片设计工程师被认为是硬件工程师,但编程是芯片设计工程师必不可少的技能之一,也正是编程思想赋予了芯片设计无限的可能。

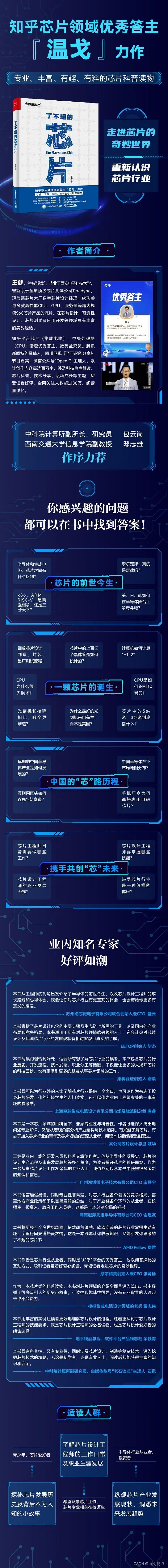

本文节选自《了不起的芯片》一书,欢迎阅读此书了解更多相关内容。

限时五折优惠,扫码了解本书详情!