前 言

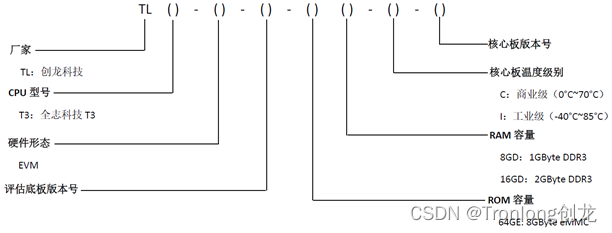

本文主要介绍创龙科技TLIMX8MP-EVM评估板硬件接口资源以及设计注意事项等内容。

创龙科技TLIMX8MP-EVM是一款基于NXP i.MX 8M Plus的四核ARM Cortex-A53 + 单核ARM Cortex-M7异构多核处理器设计的高性能工业评估板,由核心板和评估底板组成。ARM Cortex-A53(64-bit)主处理单元主频高达1.6GHz,ARM Cortex-M7实时处理单元主频高达800MHz。处理器采用14nm最新工艺,内置2.3TOPS算力NPU神经网络处理单元、双路独立ISP图像处理单元、双核心GPU图形加速器,并支持1080P60 H.264/H.265视频硬件编解码、三屏异显功能。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。

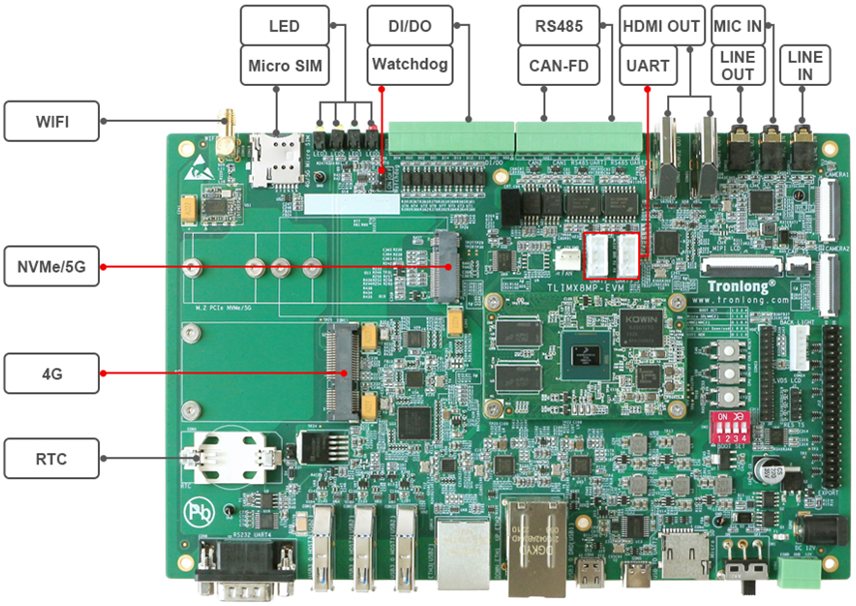

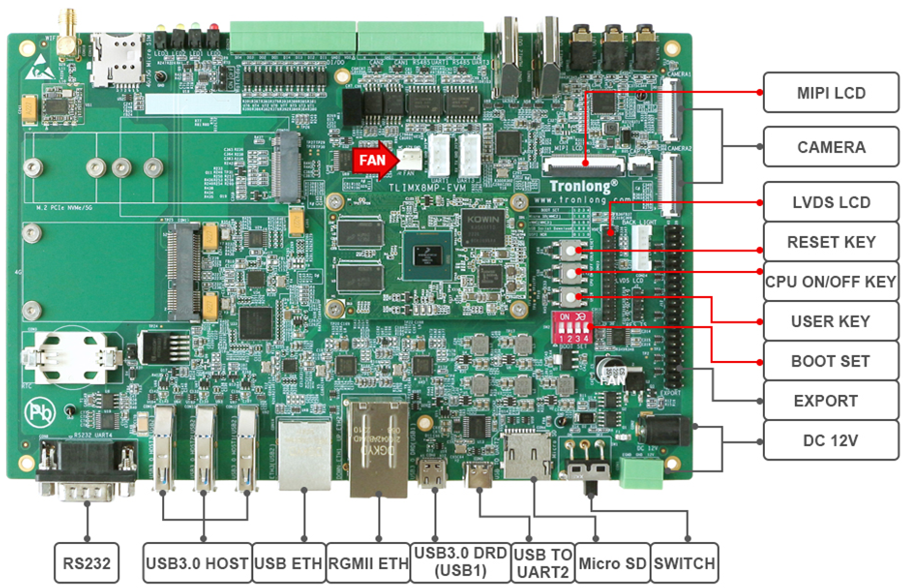

评估板接口资源丰富,引出3x USB3.0 HOST、RS232、2x CAN-FD、2x RS485、双路千兆网口(一路支持TSN)、百兆网口等通信接口,板载WIFI模块,支持4G、5G模块,支持NVMe固态硬盘,同时引出MIPI LCD、LVDS LCD、HDMI OUT、CAMERA、LINE IN、LINE OUT、MIC IN等音视频多媒体接口,方便用户快速进行产品方案评估与技术预研。

TLIMX8MP-EVM评估板采用NXP i.MX 8M Plus处理器,IO电平标准一般为1.8V和3.3V,上拉电源一般不超过3.3V。当外接信号电平与IO电平不匹配时,中间需增加电平转换芯片或信号隔离芯片。按键或接口需考虑ESD设计,ESD器件选型时需注意结电容是否偏大,否则可能会影响到信号通信。

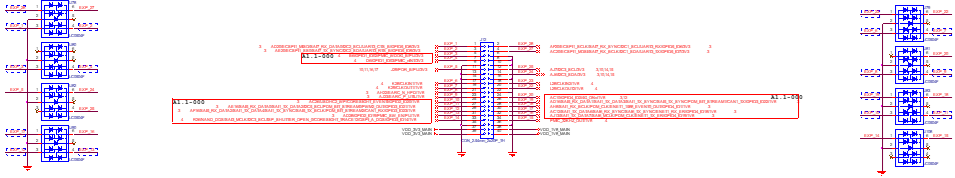

图 1 TLIMX8MP-EVM硬件资源图解1

图 2 TLIMX8MP-EVM硬件资源图解2

硬件参考资料目录如下:

(1) 《SOM-TLIMX8MP工业核心板硬件说明书》:“\5-硬件资料\核心板资料\《SOM-TLIMX8MP工业核心板硬件说明书》”;

(2) TLIMX8MP-EVM评估底板原理图:“\5-硬件资料\评估底板原理图\TLIMX8MP-EVM评估底板原理图\”;

(3) 《TLIMX8MP-EVM评估底板BOM》:“\5-硬件资料\评估底板原理图\TLIMX8MP-EVM评估底板原理图\《TLIMX8MP-EVM评估底板BOM》”;

(4) TLIMX8MP-EVM评估底板PCB:“\5-硬件资料\评估底板PCB\TLIMX8MP-EVM评估底板PCB\”;

(5) 评估底板B2B连接器封装:“\5-硬件资料\评估底板PCB\TLIMX8MP-EVM评估底板B2B连接器封装\”;

(6) SOM-TLIMX8MP核心板STP文件:“\5-硬件资料\核心板资料\SOM-TLIMX8MP核心板STP文件\”;

(7) SOM-TLIMX8MP核心板DXF文件:“\5-硬件资料\核心板资料\SOM-TLIMX8MP核心板DXF文件\”;

(8) 评估板元器件数据手册:“\6-开发参考资料\数据手册\”。

1 SOM-TLIMX8MP核心板

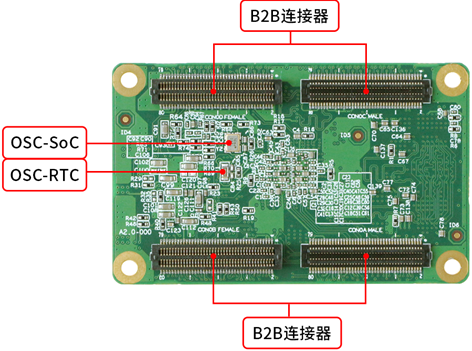

SOM-TLIMX8MP核心板板载CPU、ROM、RAM、晶振、电源、LED等硬件资源,并通过工业级B2B连接器引出IO。核心板硬件资源、引脚说明、电气特性、机械尺寸、底板设计注意事项等详细内容,请查阅《SOM-TLIMX8MP工业核心板硬件说明书》。

图 3 核心板硬件框图

图 4 核心板正面实物图

图 5 核心板背面实物图

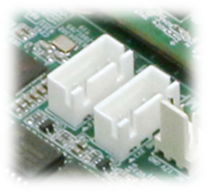

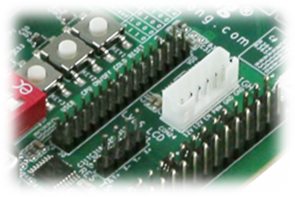

2 B2B连接器

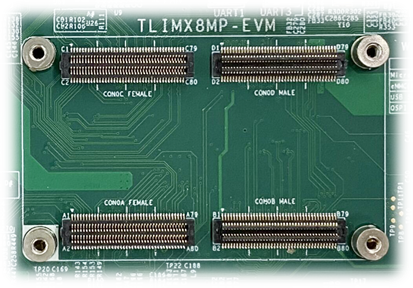

评估底板采用4个连科(Linkwork)公司的工业级B2B连接器,共320pin,间距为0.5mm,合高为4.0mm。其中2个80pin公座B2B连接器(CON0B、CON0D),型号NLWBP05-80C-1.0H,高度1.0mm;2个80pin母座B2B连接器(CON0A、CON0C),型号NLWBS05-80C-3.0H,高度3.0mm。

图 6 评估底板B2B连接器实物图

3 电源接口

评估底板由12V直流电源供电,CON1和CON2为电源输入连接器。

CON1为3pin规格绿色端子,间距3.81mm。CON2为DC-005电源接口,可适配外径5.5mm、内径2.1mm的电源插头。电源输入端具备过流保护、过压保护、防反插及快速掉电等电路保护功能。SW1为电源拨动开关,使用时请根据附近的ON/OFF丝印进行选择。

图 7 电源接口实物图

图 8 输入级电源保护电路

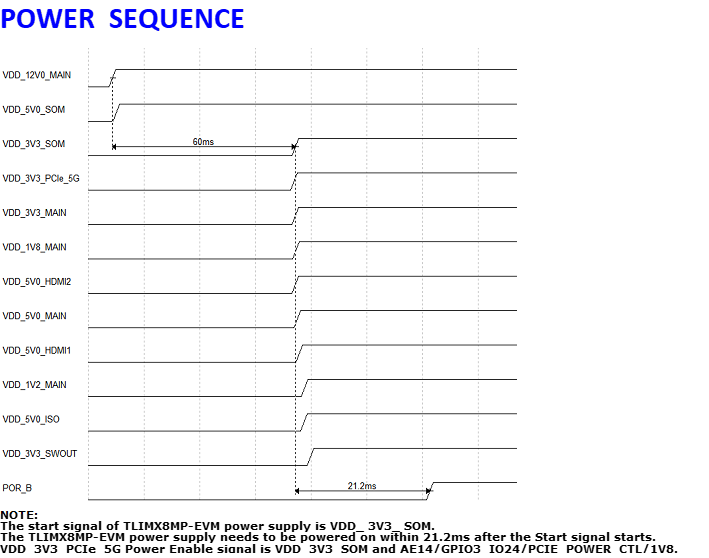

VDD_12V0_MAIN通过多路电源芯片转换为核心板及评估底板外设供电。评估底板推荐的上电时序:12V DC供电(VDD_12V0_MAIN) -> 核心板供电(VDD_5V0_SOM) -> 核心板配置底板辅助电源(VDD_3V3_SOM) -> 底板外设供电 -> 系统复位(J29/POR_B/PU/1V8),推荐上电时序设计如下图所示。

图 9 评估底板推荐上电时序

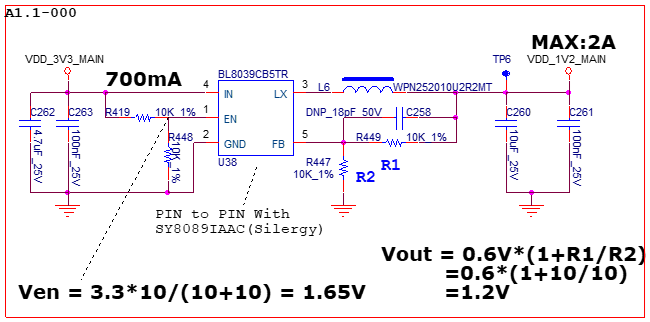

3.1 核心板电源

VDD_12V0_MAIN通过芯强微电子(Ecranic)公司的EC2232E(DC-DC电源降压芯片)输出VDD_5V0_SOM供核心板使用,最大电流供给能力为3A。

该电源使能由输入电压分压提供,实现上电即使能的时序控制。为保护核心板及方便测量电压电流,电源路径已串接磁珠FB1,实际电路默认最大电流为2A。

图 10 核心板供电电源设计

核心板提供VDD_3V3_SOM电源输出,用于控制评估底板各路电源上电时序。

3.2 评估底板外设电源

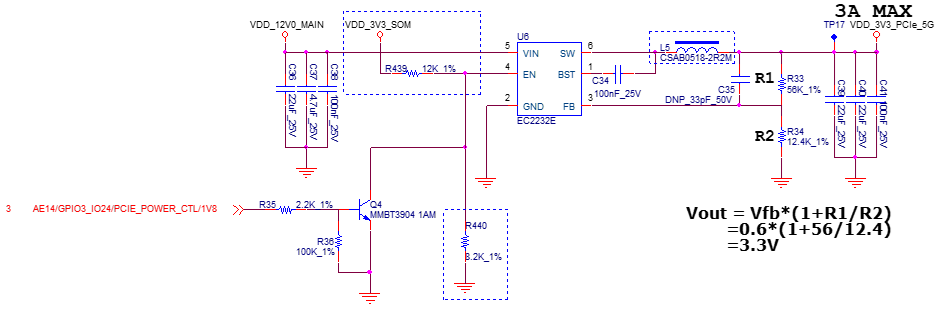

VDD_12V0_MAIN通过4路芯强微电子(Ecranic)公司的EC2232E(DC-DC电源降压芯片)分别输出VDD_5V0_MAIN、VDD_3V3_MAIN、VDD_3V3_PCIe_5G、VDD_1V8_MAIN供评估底板外设使用,最大电流供给能力为3A。4路电源使能都由VDD_3V3_SOM提供,实现评估底板外设电路在核心板之后上电的时序控制。

备注:VDD_3V3_PCIe_5G电源使能同时受AE14/GPIO3_IO24/PCIE_POWER_CTL/1V8信号控制。

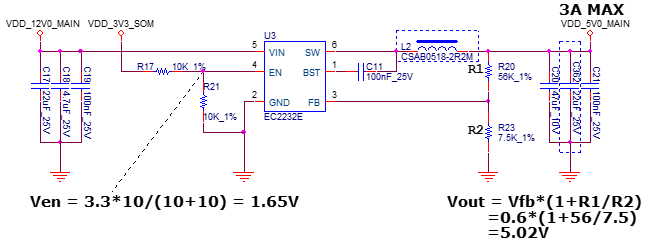

图 11 VDD_5V0_MAIN电源设计

图 12 VDD_3V3_MAIN电源设计

图 13 VDD_3V3_PCIe_5G电源设计

图 14 VDD_1V8_MAIN电源设计

3.3 隔离电源

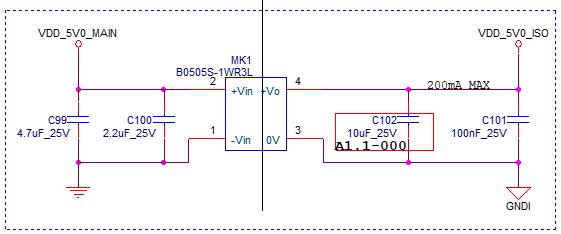

VDD_5V0_MAIN通过金升阳科技(MORNSUN)公司的B0505S-1WR3L隔离电源模块输出1路5V DC隔离电源VDD_5V0_ISO,用于评估底板隔离电路的供电,最大电流供给能力为200mA,可提供3000V DC的直流隔离能力。

图 15 VDD_5V0_ISO电源设计

设计注意事项:

(1) 底板设计时,若无需电源输入级保护电路的部分或全部功能,可适当裁剪。

(2) 底板电源设计可根据实际电路设计进行增减,建议参考我司上电时序进行底板电源的使能控制。

(3) VDD_5V0_SOM在核心板内部未预留总电源输入的储能大电容。底板设计时,请在靠近B2B连接器焊盘位置放置总容值为50uF左右的储能电容。

(4) 为使VDD_5V0_MAIN、VDD_3V3_MAIN、VDD_3V3_PCIe_5G和VDD_1V8_MAIN满足系统上电、掉电时序要求,需使用核心板输出VDD_3V3_SOM来控制VDD_5V0_MAIN、VDD_3V3_MAIN、VDD_3V3_PCIe_5G和VDD_1V8_MAIN的电源使能,使评估底板VDD_5V0_MAIN、VDD_3V3_MAIN、VDD_3V3_PCIe_5G和VDD_1V8_MAIN电源在VDD_3V3_SOM之后、在J29/POR_B/PU/1V8复位信号之前上电,详情见评估底板推荐上电时序。

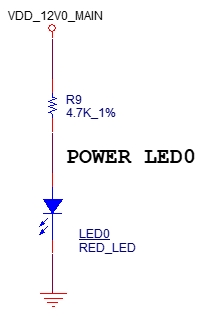

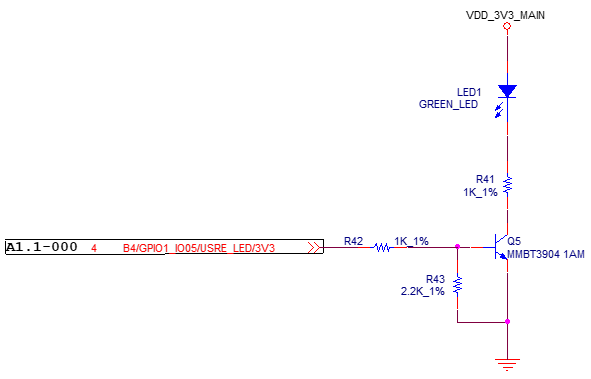

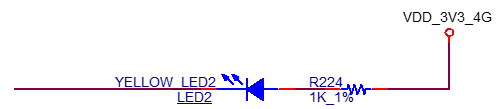

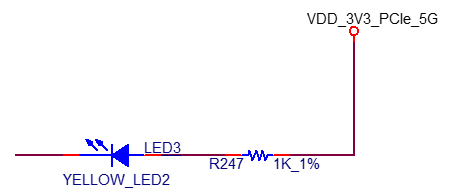

4 LED

评估底板板载4个LED。LED0为电源指示灯,颜色为红色,上电默认点亮;LED1为用户可编程指示灯,通过GPIO控制,颜色为绿色,默认高电平点亮;LED2为4G模块状态指示灯,颜色为黄色;LED3为NVMe固态硬盘/5G模块状态指示灯,颜色为黄色。

图 16 LED0~LED3实物图

图 17 评估板电源指示灯

图 18 用户可编程指示灯

图 19 4G模块状态指示灯

图 20 NVMe固态硬盘/5G模块状态指示灯

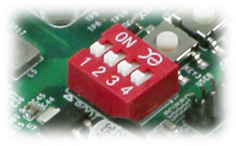

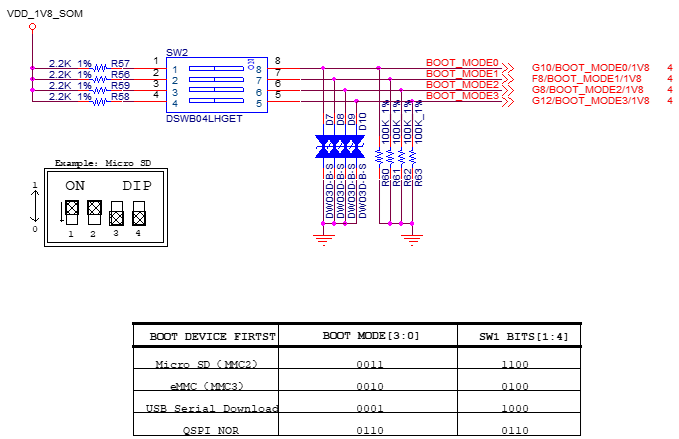

5 BOOT SET启动方式选择拨码开关

SW2为4bit启动方式选择拨码开关。常用启动模式如下所示,请根据评估底板丝印确认启动方式选择拨码挡位。

(1) Micro SD模式:1100(1~4)。

(2) eMMC模式:0100(1~4)。

(3) USB Serial Download模式:1000(1~4)。

备注:选择配置为USB Serial Download模式时,评估板支持从USB3.0 DRD(USB1)固化系统。

图 21 启动方式选择拨码开关实物图

图 22 BOOT SET配置电路选择

设计注意事项:

(1) BOOT_MODE[0:3]引脚在评估底板通过BOOT SET启动选择拨码开关或上下拉电阻进行启动模式选择。请参考评估底板BOOT SET电路进行启动配置电路设计,特别是上下拉电阻的阻值必须参考评估底板所使用的电阻参数进行选型。

(2) BOOT_MODE[0:3]引脚请使用核心板输出的VDD_1V8_SOM电源。VDD_1V8_SOM为专用于BOOT SET配置和QSPI NOR FLASH的电源,电流供给能力为100mA,请勿用于其他负载供电。

(3) 在POR_B信号置高之前,请确保BOOT_MODE[0:3]信号的电平状态不被改变。

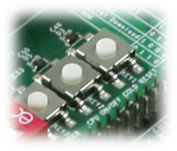

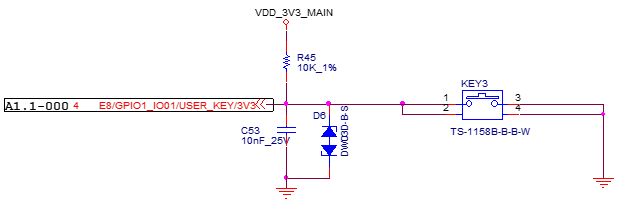

6 KEY

评估底板包含1个系统冷复位按键COLD RESET(KEY1),1个CPU开关机按键CPU ON/OFF(KEY2),1个用户输入按键USER(KEY3)。

图 23 KEY实物图

图 24 系统复位、CPU开关机按键

图 25 用户输入按键

设计注意事项:

(1) PMIC_KEY_RSTn为PMIC的上电复位输入引脚,在PMIC内部已上拉至1.8V,无需使用时,请悬空处理。

(2) G22/ONOFF为CPU的开关机控制引脚,长按5s以上CPU将会关机,再按1s左右CPU将切换为开机。核心板内部已设计100K上拉电阻,无需使用时,请悬空处理。

7 串口

评估底板板载UART、RS232和RS485串口,CON5为USB TO UART2调试串口,CON7为UART1串口,CON9为UART3串口,CON8为RS232 UART4串口,CON28含有RS485 UART1和RS485 UART3串口。

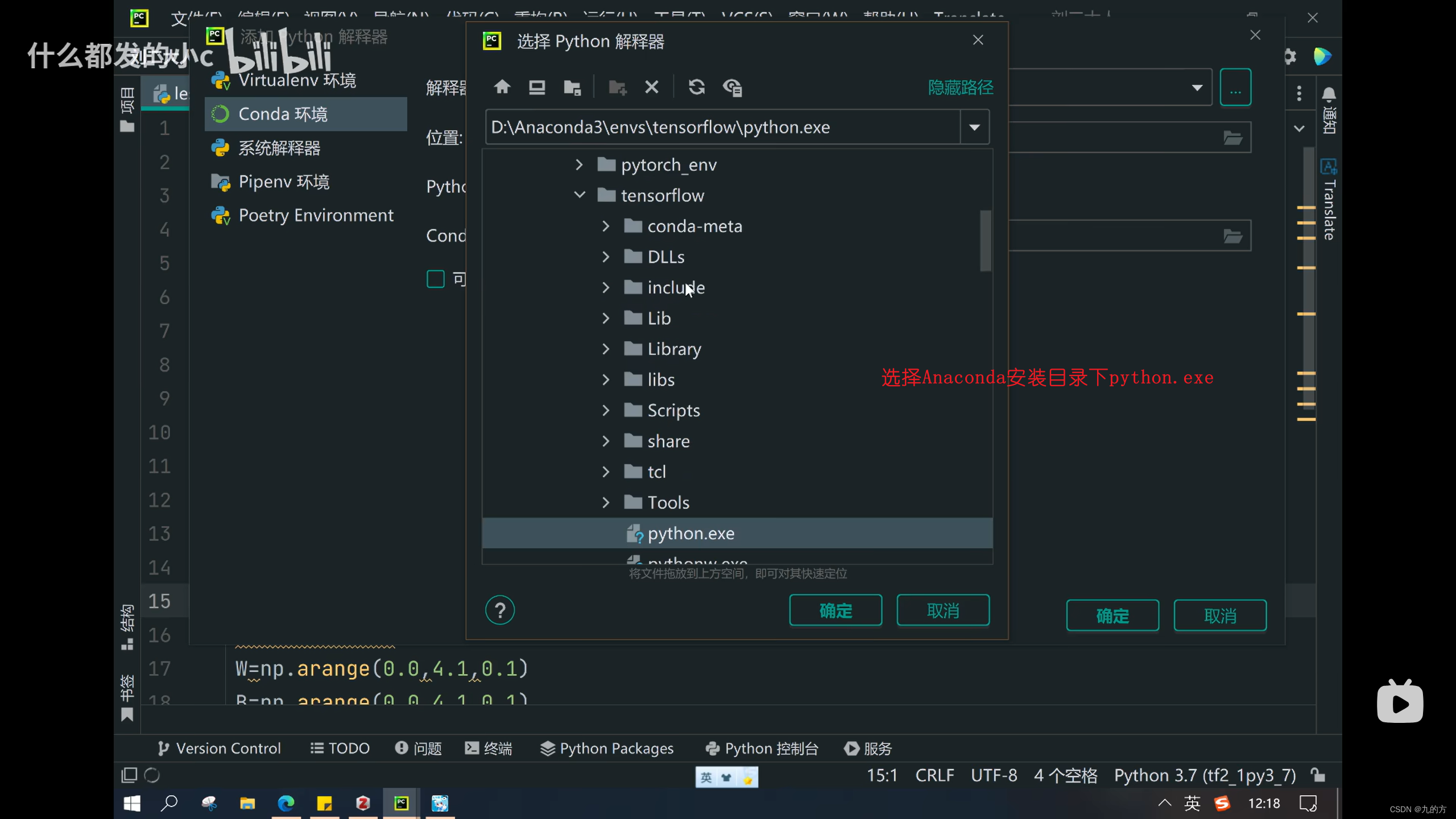

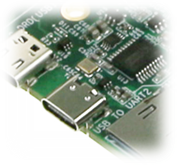

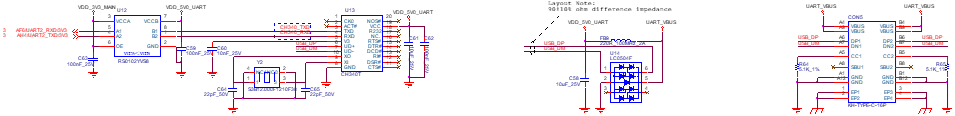

7.1 USB TO UART2串口

评估底板通过沁恒微电子(WCH)公司的CH340T芯片将UART2转换为Type-C连接器(CON5)引出,作为系统调试串口使用。CH340T使用来自Type-C线的5V电源UART_VBUS外部供电。

图 26 USB TO UART2串口实物图

图 27 USB TO UART2串口电路设计

设计注意事项:

(1) 底板设计时,建议采用RS0102YVS8(U12)电平转换隔离方案,以免调试串口RX端在底板上电前提前带电,向核心板引脚灌输电流,导致系统无法启动。

(2) CPU引脚UART2_TXD、UART2_RXD电平均为3.3V,请勿使用5V电平接口的调试工具直接连接,否则将可能导致CPU损坏。

(3) 注意USB信号需做90ohm差分阻抗匹配。

(4) ESD器件需靠近连接器Type-C接口布局,走线经过ESD后连接至CH340T。

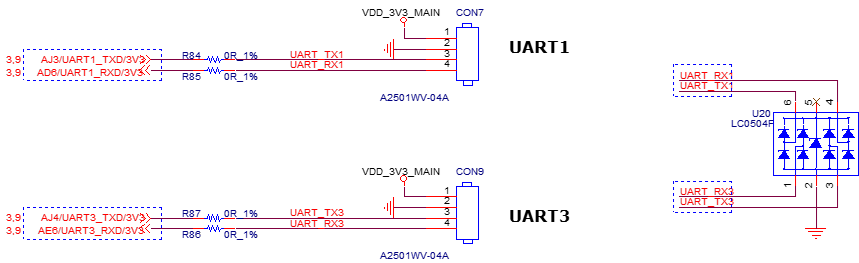

7.2 UART1/UART3串口

评估板采用4pin规格、间距2.54mm白色端子(CON7、CON9),直接引出UART1、UART3串口。

图 28 UART1、UART3串口实物图

图 29 UART1、UART3串口电路设计

设计注意事项:

(1) UART1接口和RS485 UART1接口共用同一组UART1总线,UART3接口和RS485 UART3接口共用同一组UART3总线,同一组UART总线接口请勿同时使用。

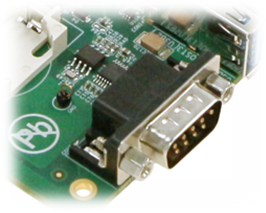

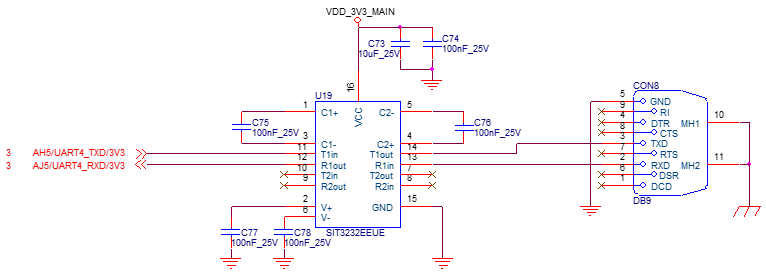

7.3 RS232 UART4串口

评估底板采用芯力特电子(SIT)公司的单电源双通道RS232收发器SIT3232EEUE方案,通过UART4引出1路RS232串口,使用DB9连接器(CON8)。

SIT3232EEUE符合TIA/EIA-232标准,最高通信速率可达到120Kbps。

图 30 RS232 UART4串口实物图

图 31 RS232 UART4串口电路设计

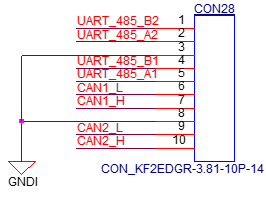

7.4 RS485 UART1/RS485 UART3串口

评估底板采用川土微电子(CHIPANALOG)公司的隔离式半双工RS485收发器CA-IS3082WX方案,将UART1、UART3转换为2路RS485串口。2路RS485串口与CAN接口共用10pin规格、3.81mm间距绿色端子(CON28)。

CA-IS3082WX符合TIA/EIA-485-A标准,支持5kVrms绝缘耐受电压,总线共模工作范围:-7V~+12V,并提供高达0.5Mbps的通信速率。

图 32 RS485 UART1/RS485 UART3串口实物图

图 33 RS485 UART1/RS485 UART3串口电路设计

图 34

设计注意事项:

(1) CA-IS3082WX为隔离RS485收发器;其中Vcc1(pin1)和GND1(pin7/8)为逻辑侧端口的供电,Vcc2(pin16)和GND2(pin9/10)为总线侧端口供电。Vcc1对Vcc2应电气隔离,GND1和GND2不共地,且器件布局及走线上注意做隔离设计,否则无法达到隔离接口的设计目的。建议参考评估底板使用隔离电源给Vcc2供电。

(2) Vcc1提供2.375V~5.5V的宽IO供电范围,总线侧电源Vcc2提供3.0V~5.5V的RS485总线供电范围。

(3) 收发器的管脚A/B(pin12/13)连接至绿色端子连接器之间的走线,需按差分信号进行走线。

(4) UART1接口和RS485 UART1接口共用同一组UART1总线,UART3接口和RS485 UART3接口共用同一组UART3总线,同一组UART总线的接口请勿同时使用。

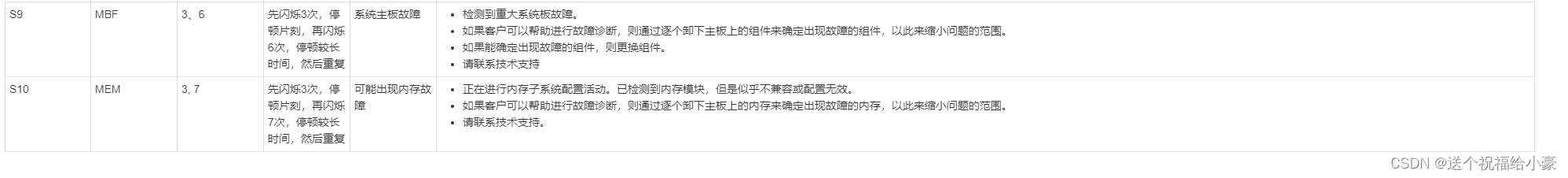

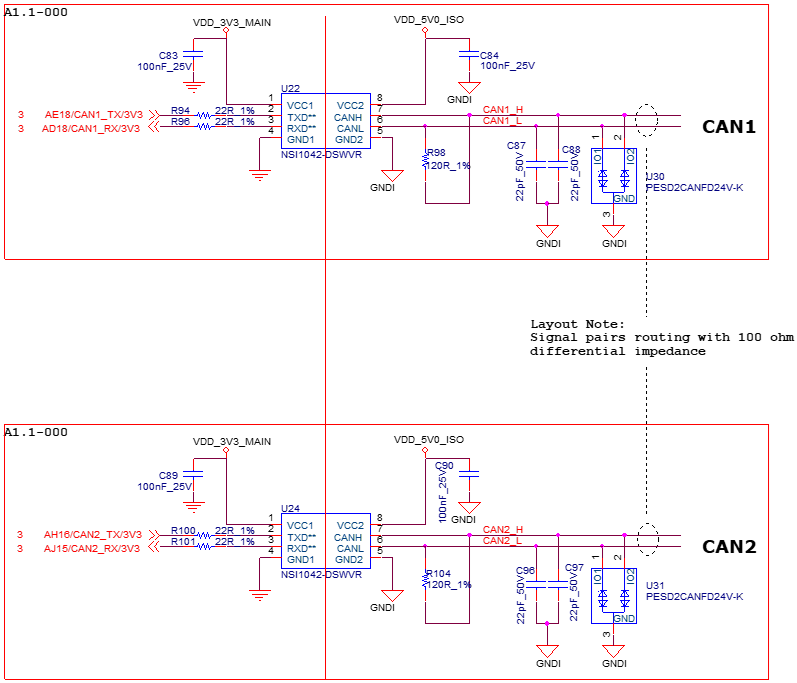

8 CAN1/CAN2接口

评估底板通过2个纳芯微电子(NOVOSENSE)公司的隔离式收发器NSI1042-DSWVR引出CAN1、CAN2接口,与RS485串口共用10pin规格、间距3.81mm绿色端子(CON28)。

NSI1042-DSWVR符合ISO11898-2标准,供电电压为3.3V(VDD_3V3_MAIN)。支持5kVrms绝缘耐受电压,总线共模工作范围:-30V~+30V,最高通信速率为5Mbps。

图 35 CAN1/CAN2接口实物图

图 36 CAN1/CAN2电路设计

图 37 CAN电路设计

设计注意事项:

(1) NSI1042-DSWVR为隔离CAN收发器。其中VCC1(pin1)和GND1(pin4)为逻辑侧端口供电,VCC2(pin8)和GND2(pin5)为总线侧端口供电。VCC1对VCC2应是电气隔离,GND1和GND2不共地,且器件布局及走线上注意做隔离设计,否则无法达到隔离接口的设计目的。建议参考我司使用隔离电源给VCC2供电。

(2) VCC1提供2.5V~5.5V的宽IO供电范围,VCC2提供4.5V~5.5V的CAN总线侧供电范围。

(3) CANH(pin7)和CANL(pin6)与绿色端子连接器之间的走线,需按差分信号进行走线。

(4) CANH(pin7)和CANL(pin6)应并联一个精度为1%的终端匹配电阻(R98、R104)。终端匹配电阻的大小由传输电缆的特性阻抗所决定,一般为120ohm。

(5) 建议参考评估底板使用的ESD器件型号PESD2CANFD24V-K,或使用其他电容值小于等于15pF的ESD器件,且共模电压值至少需要支持+/-12V。

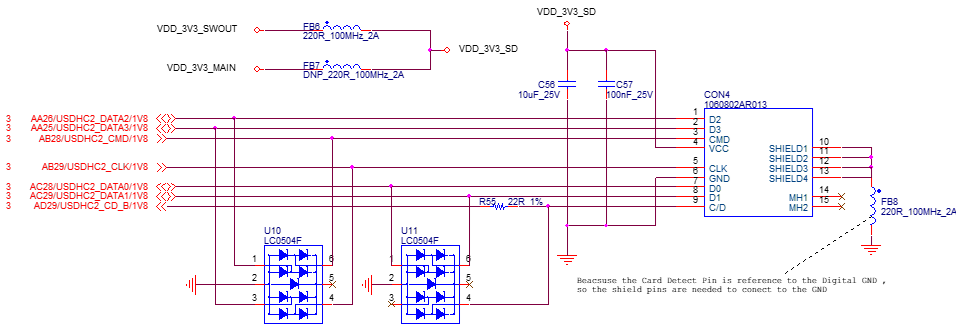

9 Micro SD接口

评估底板通过uSDHC2总线引出1路Micro SD接口,采用4bit数据线模式。使用规格为外壳带压片的外焊式Micro SD连接器(CON4)。

图 38 Micro SD接口实物图

图 39 Micro SD接口电路设计

设计注意事项:

(1) 底板设计时,需将Micro SD座子外壳的SHIELD[1:4]引脚连接至数字地。

(2) 建议使用核心板的输出电源VDD_3V3_SD为Micro SD(CON4)供电。不建议使用VDD_3V3_MAIN供电,否则可能因该电源存在供电延迟,导致系统无法正确读取Micro SD卡设备而启动失败。

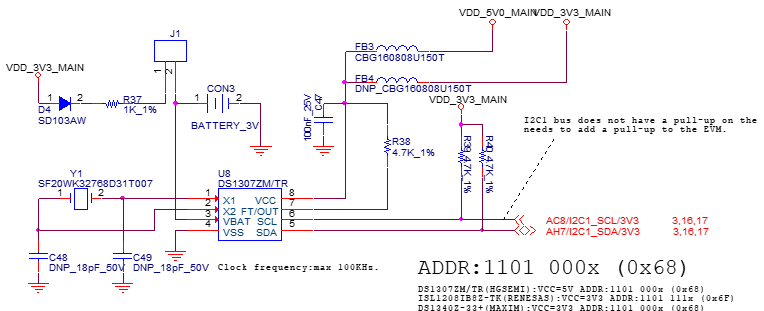

10 外部RTC座

评估底板采用华冠半导体(HGSEMi)公司的串行实时时钟芯片DS1307ZM/TR,拓展外部RTC功能,使用I2C1总线进行通信。CON3为RTC纽扣电池座,可适配纽扣电池ML2032(3V可充)、CR2032(3V不可充)。使用可充电电池时,可将跳线帽插入J1接口实现充电。使用不可充电电池时,请勿将跳线帽插入J1接口。

图 37 外部RTC电路实物图

图 40 外部RTC电路设计

设计注意事项:

(1) U8可选用DS1307ZM/TR、DS1340Z-33+和ISL1208IB8Z-TK。若选贴DS1340Z-33+和ISL1208IB8Z-TK时,需将FB4实贴,将FB3空贴,并使用VDD_3V3_MAIN供电。

(2) I2C1已连接至核心板的PMIC电源管理芯片,I2C1在核心板上未添加上拉电阻,请务必在底板上拉4.7K电阻至3.3V。

11 外部Watchdog接口

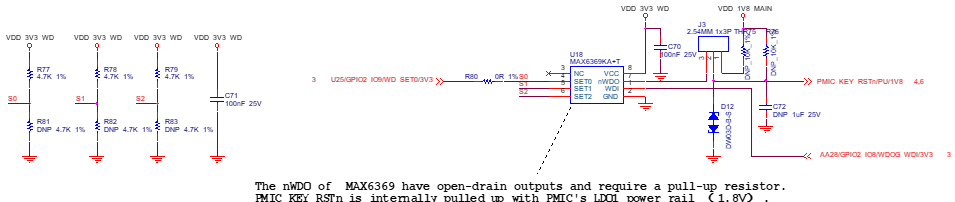

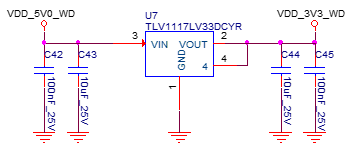

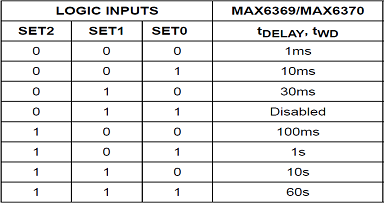

评估底板采用美国美信(Maxim Integrated)公司的外部硬件看门狗芯片MAX6369KA+T,拓展外部Watchdog功能。J3为Watchdog功能配置接口,采用2.54mm间距、3pin排针方式,可通过跳线帽配置使能Watchdog功能。软件上可通过U25/GPIO2_IO9/WD_SET0/3V3配置Watchdog超时时长。

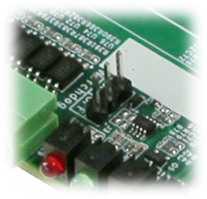

图 41 外部Watchdog电路实物图

图 42 外部Watchdog电路设计

图 43

图 44

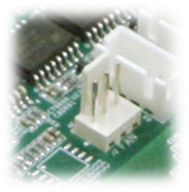

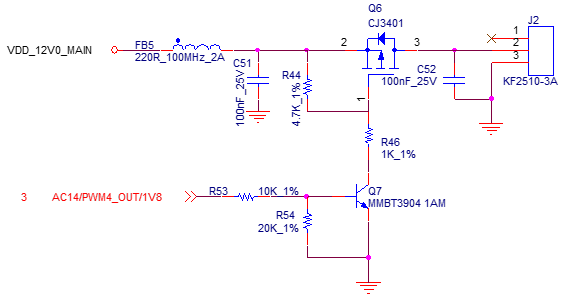

12 FAN供电接口

J2为散热器风扇电源接口(FAN),采用3pin排针端子方式,12V供电,间距2.54mm。

图 45 FAN供电接口实物图

图 46 FAN供电接口电路设计

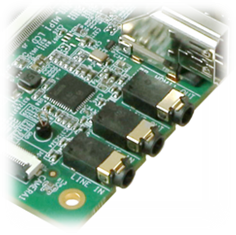

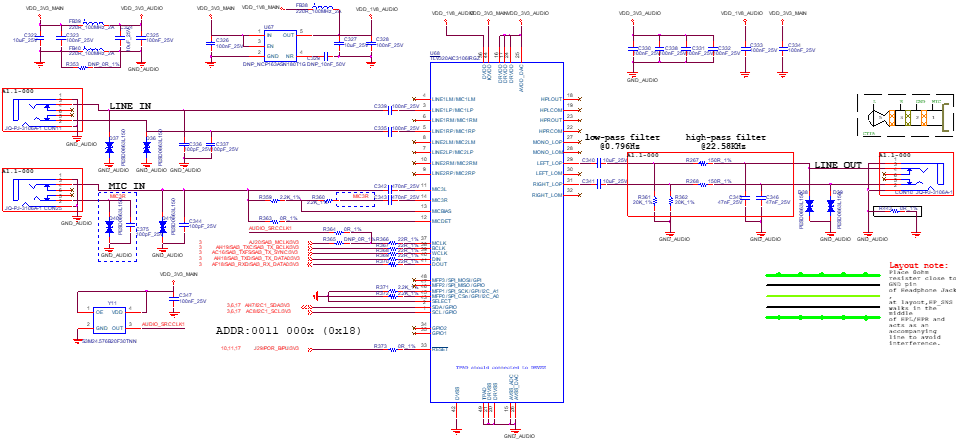

13 LINE IN/MIC IN/LINE OUT接口

评估底板采用德州仪器(TI)公司的TLV320AIC3106IRGZ音频芯片,引出LINE IN(CON11)、MIC IN(CON25)和LINE OUT(CON10)共3路音频接口,均采用3.5mm音频插座。

CPU通过SAI3总线与TLV320AIC3106IRGZ进行通信,采用I2C1进行配置,地址为0x18。

图 47 LINE IN/MIC IN/LINE OUT接口实物图

图 48 LINE IN/MIC IN/LINE OUT接口电路设计

设计注意事项:

(1) 若未使用外部时钟源,可将R364电阻空贴,R365电阻实贴。

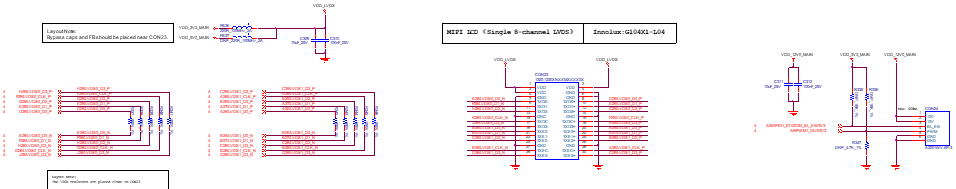

14 MIPI LCD接口

J5为MIPI LCD显示接口,采用40pin FFC连接器,间距0.5mm。

J6为MIPI LCD的电容触摸接口CAP TS,采用6pin FFC连接器,间距0.5mm。评估板使用I2C3总线与其连接实现通信。

图 49 MIPI LCD接口实物图

图 50 MIPI LCD接口电路设计

设计注意事项:

(1) 为确保CAP TS(J6)的nINT引脚功能正常,请添加100K上拉电阻。

(2) CAP TS(J6)的nINT引脚需使用支持中断功能的GPIO引脚;

(3) 由于HDMI2 OUT和MIPI LCD接口共用MIPI_DSI1总线,因此HDMI2 OUT和MIPI LCD接口不可同时使用。

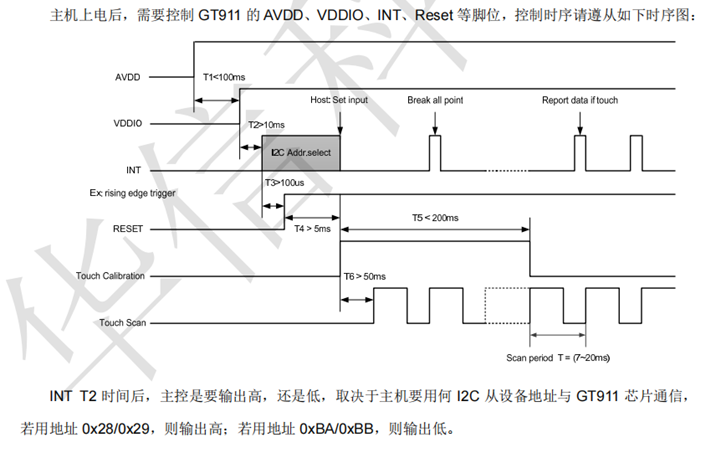

(4) 触摸屏一般存在两个可选I2C地址,当RESET(RST)完成上电时会读取INT(nINT)引脚信号的高低电平以此来选择触摸屏的I2C地址。

图 51 触摸屏上电时序和地址选择说明图

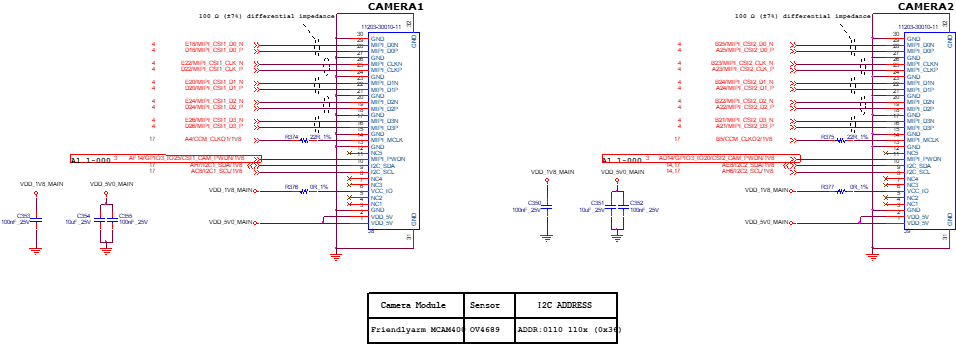

15 CAMERA1/CAMERA2接口

评估板通过MIPI_CSI1、MIPI_CSI2总线分别引出CAMERA1(J8)和CAMERA2(J9)摄像头接口,均采用30pin FFC连接器,间距0.5mm。

评估板分别使用I2C1、I2C2总线配置CAMERA1和CAMERA2。

图 52 CAMERA1/CAMERA2接口实物图

图 53 CAMERA1/CAMERA2接口电路设计

设计注意事项:

(1) 由于CAMERA1/CAMERA2摄像头接口的信号电平为1.8V,但核心板输出的I2C1、I2C2、CCM_CLKO1和CCM_CLKO2信号电平为3.3V,因此需进行电平转换为1.8V后,再连接至CAMERA1/CAMERA2接口使用。

16 HDMI OUT接口

16.1 HDMI1 OUT接口

评估底板通过HDMI总线直接引出HDMI1 OUT(CON21)视频输出接口,采用标准19pin HDMI连接器。支持HDMI 2.0标准,支持2160P超高清视频输出.

图 54 HDMI1 OUT接口实物图

图 55 HDMI1 OUT接口电路设计

设计注意事项:

(1) HDMI接口HPLG信号需通过分压电阻(R294、R297)输入3.3V信号至核心板,HPLG信号可与3.3V或者5V电平IO进行连接。当外部设备接入时,会将此信号拉高。

(2) 请勿将HDMI接口输出的VDD_5V0_HDMI1电源用于其他负载供电。

(3) AC22/HDMI_DDC_SCL/3V3和AF22/HDMI_DDC_SDA/3V3的IO电平为3.3V,需转换为5V电平再引出至HDMI接口。为防止核心板掉电时通过HDMI接口馈电,需参考评估底板电路设计添加D32和D33器件。

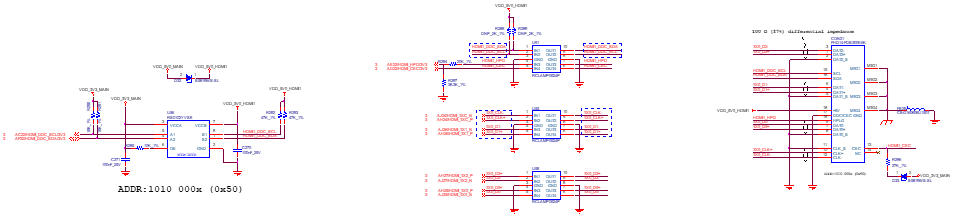

16.2 HDMI2 OUT接口

评估底板采用龙迅(Lontium)公司的LT8912B芯片方案,通过MIPI_DSI1总线拓展HDMI2 OUT接口,采用标准19pin HDMI连接器。支持HDMI1.4标准,支持1080P高清视频输出。

图 56 HDMI2 OUT接口实物图

图 57 HDMI2 OUT接口电路设计

图 58 HDMI2 OUT接口电路设计

设计注意事项:

(1) 由于HDMI2 OUT接口由MIPI_DSI1拓展引出,因此请勿同时使用HDMI2 OUT和MIPI LCD接口。

(2) 请勿将HDMI接口输出的VDD_5V0_HDMI2电源用于其他负载供电。

(3) 为防止核心板掉电时通过HDMI接口馈电,需参考评估底板电路添加D34器件。

17 LVDS LCD接口

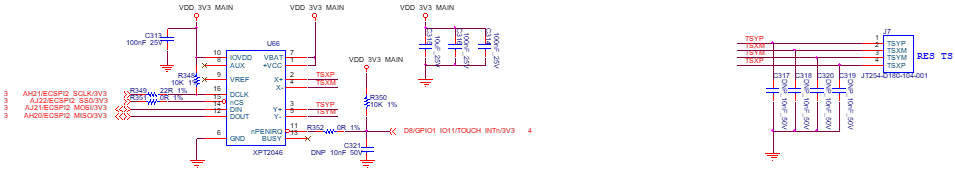

CON23为双路8bit LVDS LCD接口,采用30pin双排针,间距2.0mm,包含LVDS信号及供电电源。CON24为BACK LIGHT背光控制接口,采用6pin白色端子座,间距2.0mm。J7为RES TS电阻触摸屏接口,采用4pin排针,间距2.54mm。

图 59 LVDS LCD接口实物图

图 60 LVDS LCD接口电路设计

图 61 RES TS电阻触摸屏接口电路设计

设计注意事项:

(1) LVDS差分对的终端匹配电阻100R需靠近CON23接口放置。

18 USB接口

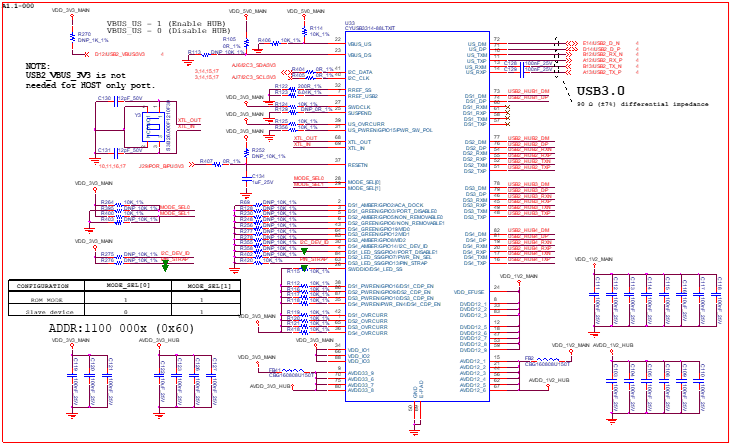

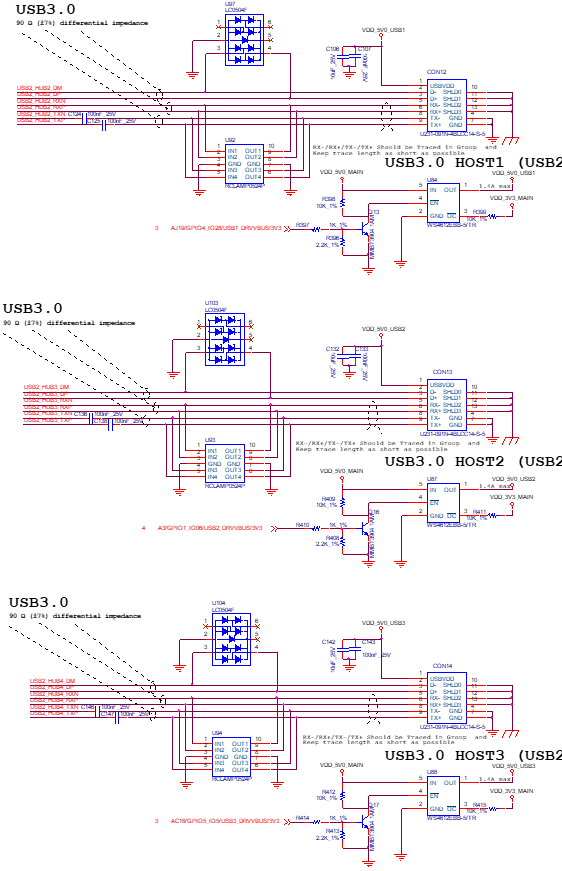

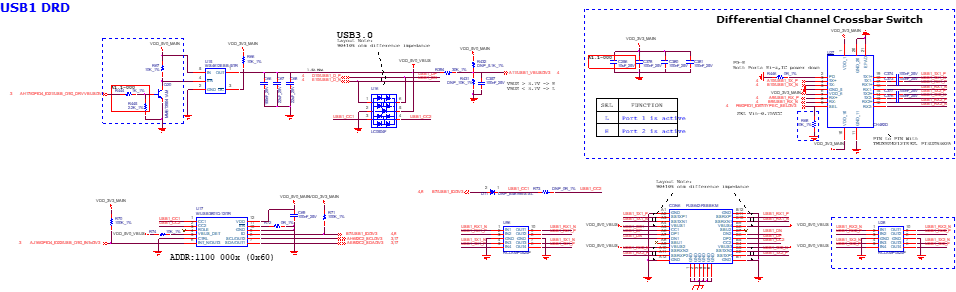

评估底板引出4路USB接口。CON12、CON13和CON14为USB3.0 HOST接口,采用侧插Type-A型连接器;CON6为USB3.0 DRD接口,采用Type-C型连接器。

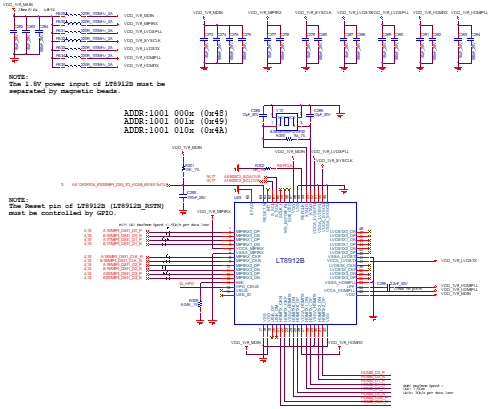

18.1 USB3.0 HOST接口

评估底板采用赛普拉斯(CYPRESS)公司的4端口USB3.0 HUB控制器CYUSB3314-88LTXIT,将USB2总线拓展为4路USB3.0 HOST,并将其中3路引出至USB3.0 HOST1、USB3.0 HOST2、USB3.0 HOST3接口,将另外1路USB3.0 HOST(USB2_HUB1)总线,通过USB2.0 HUB芯片(CH334H)拓展为4路USB2.0 HOST总线。

CYUSB3314-88LTXIT芯片符合USB3.0协议规范,支持超速(SS)、高速(HS)、全速(FS)以及低速(LS)模式。

图 62 USB3.0 HOST接口实物图

图 63 USB3.0 HOST接口电路设计

图 64 USB3.0 HOST接口电路设计

图 65 USB3.0 HOST接口电路设计

图 66 USB3.0 HOST接口电路设计

设计注意事项:

(1) CYUSB3314-88LTXIT中US_RXM、US_RXP引脚的AC耦合电容(C128、C129)需靠近芯片(U33)放置,US_TXM、US_TXP的AC耦合电容(C372、C371)需靠近核心板B2B连接器放置。

18.2 USB3.0 DRD接口

CON6为USB3.0 DRD接口,采用24pin Type-C母座,由核心板通过USB1总线引出。

评估底板采用韦尔半导体(WILLSEMI)的Type-C控制芯片WUSB3801Q-12/TR,实现通信角色的检测功能。

由于USB3.0差分对信号速率高达5Gbps,因此不能按USB2.0方式直接分叉连接至Type-C接口正面和反面。建议选用沁恒微电子(WCH)公司的USB切换开关芯片CH482D实现正反接功能,该芯片支持USB3.0 Super Speed、PCIe Gen1/2、SATA/SAS 1.5Gbps/3Gbps/6Gbps、DisplayPort等2路差分信号的二选一切换。

图 67 USB3.0 DRD接口实物图

图 68 USB3.0 DRD接口电路设计

设计注意事项:

(2) CH482D中TX1+、TX1-、TX2+、TX2-的AC耦合电容(C374、C373、C377、C376)需靠近芯片(U27)放置。

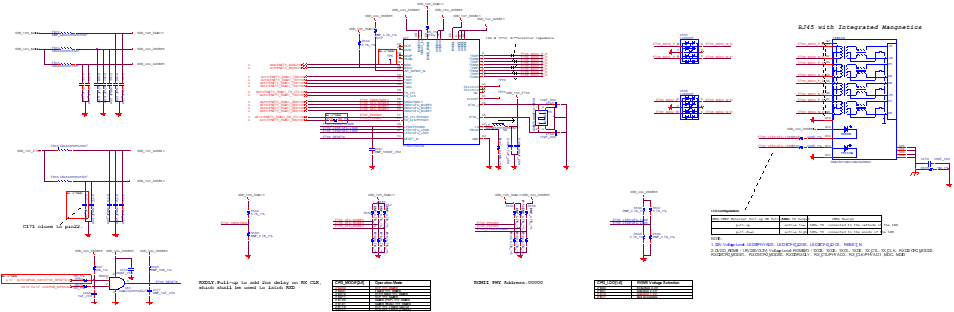

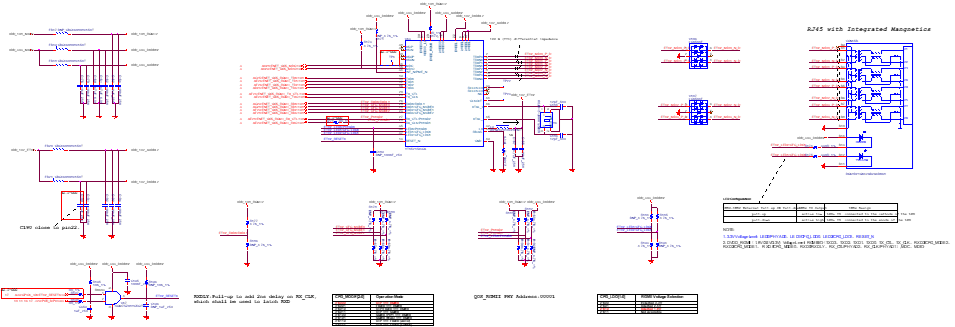

19 Ethernet接口

评估板包含2个ETH RGMII千兆网口和1个ETH USB百兆网口。

CPU内部集成2个Gigabit Ethernet控制器,支持2路原生RGMII千兆网口,其中一路ENET_QOS支持TSN工业协议。

19.1 ETH1/ETH2千兆网口

评估底板通过裕太微电子(Motorcomm)公司的YT8521SH-CA集成以太网收发器方案,提供2路10/100/1000Mbps自适应以太网,采用双层千兆RJ45连接器,RJ45连接器已内置隔离变压器。其中下层为ETH1千兆网口,上层为ETH2千兆网口。

2路千兆网口均使用独立的RGMII总线、MDIO总线实现PHY通信以及配置。其中,ETH1由ENET1_RGMII总线控制,ETH2由ENET_QOS_RGMII总线控制。

YT8521SH-CA符合10BASE-Te、100BASE-TX和1000BASE-T IEEE802.3标准,提供交叉检测、自动校正、极性校正和自适应均衡等功能。

图 69 ETH1/ETH2千兆网口实物图

图 70 ETH1接口电路设计

图 71 ETH2接口电路设计

设计注意事项:

(1) ETH1和ETH2的PHY使用1.8V IO电平。对应的RGMII总线电平选择通过CFG_LDO[1:0]进行配置,对应电路的供电引脚为YT8521SH-CA芯片的DVDD_RGMII。

(2) XTAL_I、XTAL_O引脚接入25MHz无源晶振。如需使用25MHz有源晶振,可从XTAL_I引脚接入,并将XTAL_O引脚悬空处理。

(3) 评估底板采用的YT8521SH-CA方案,使用了内部产生的1.2V电压(VDD_1V2_ETH1、VDD_1V2_ETH2)进行核心逻辑供电,无需额外提供1.2V电压。VDD_1V2_ETH1、VDD_1V2_ETH2请勿用于其它负载供电。

(4) YT8521SH-CA芯片要求在供电稳定后保持100ms,再拉高复位信号;推荐使用IO控制PHY芯片的复位。

(5) PCB布局布线说明:

a) ESD器件注意放置在紧靠RJ45连接器的位置。

b) MDIx_P/N_D信号注意按100ohm差分信号走线,晶振提供的时钟信号建议包地处理。

c) RGMII总线中的收发两组信号应分别做±50mil等长处理,请注意获取核心板硬件说明书中提供的对应信号在核心板内的走线长度。

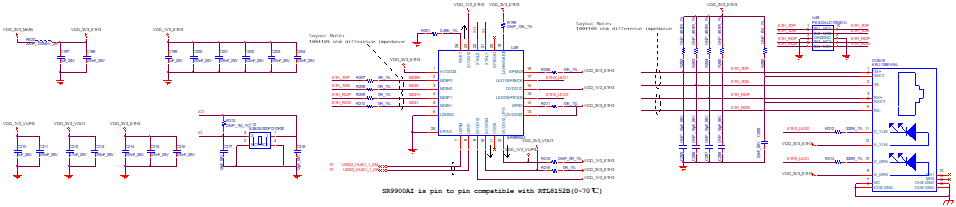

19.2 ETH3(USB2)百兆网口

评估底板采用和芯润德科技公司的SR9900AI集成以太网控制电路方案,通过USB2_HUB1_1总线拓展1路10/100Mbps自适应以太网,使用内置隔离变压器的百兆RJ45插座(CON16)。

SR9900AI符合IEEE802.3 10Base-T/100Base-TX和IEEE802.3 100Base-FX标准,提供极性、相位偏移校正,网线交叉检测及自动校正等功能。

备注:评估底板采用USB2.0 HUB芯片(CH334H)将USB2_HUB1总线拓展为4路USB2.0 HOST总线,将其中1路USB2_HUB1_1总线进行ETH3(USB2)百兆网口拓展。

图 72 ETH3(USB2)百兆网口实物图

图 73 ETH3(USB2)百兆网口电路设计

设计注意事项:

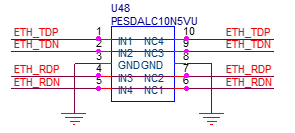

(1) 靠近RJ45连接器的PESDALC10N5VU为10pin封装的ESD器件,请注意并排的2个引脚(如IN1和NC4、IN2和NC3)在ESD器件内部并无连接,实际设计中应将对应引脚直接外部短接处理(如下图),即对应引脚的网络名需保持一致,便于PCB布线。

图 74 ESD电路设计

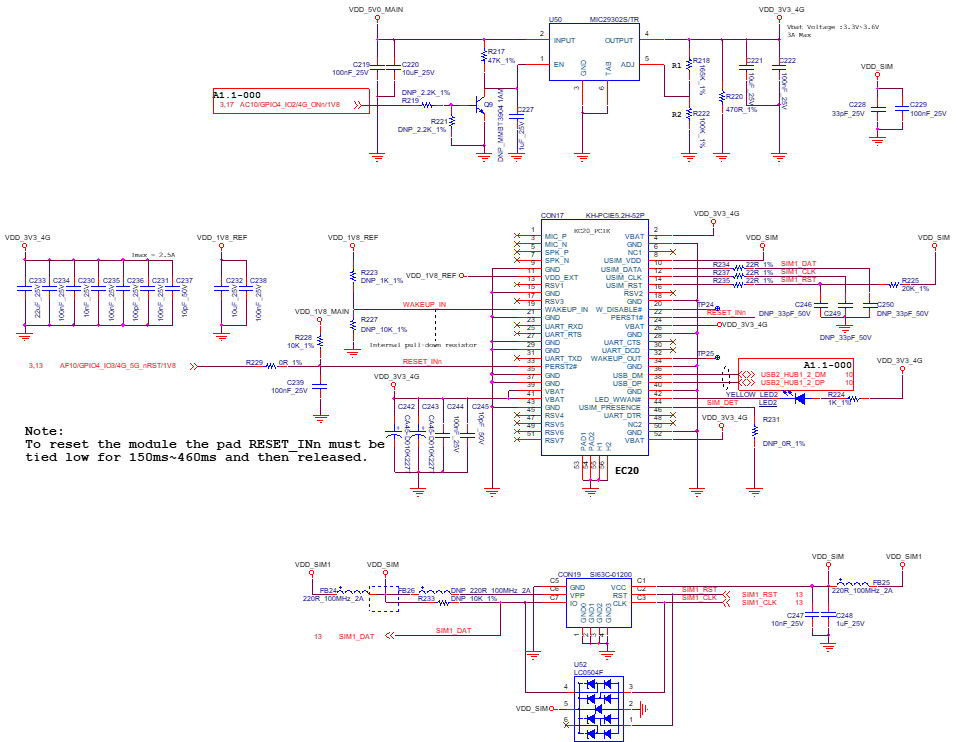

20 4G模块接口

CON17为4G模块拓展接口,采用Mini PCIe插槽。可适配移远EM05CEFC-128-SGAS 4G模块。评估底板通过USB2.0 HUB芯片(CH334H)将USB2_HUB1总线拓展为4路USB2.0 HOST总线,将其中1路USB2_HUB1_2总线进行4G模块拓展。

图 75 4G模块接口实物图

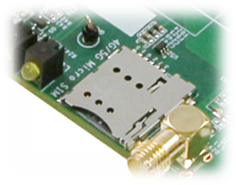

CON19为4G模块和5G模块共用的Micro SIM卡座,采用插卡自弹形式,不带检测引脚,使用时需正确插入相应的Micro SIM卡。

图 76 4G/5G Micro SIM卡座实物图

图 77 4G模块接口电路设计

设计注意事项:

(1) 为保证4G模块的电源稳定供应,其3.3V电源需由MIC29302S/TR独立供电,至少提供2A电流输出。如需替换其他电源,建议使用LDO,详细请参考4G模块数据手册要求。

(2) 如需控制4G模块供电,可实贴R219和R221电阻,通过GPIO控制4G模块电源使能状态。

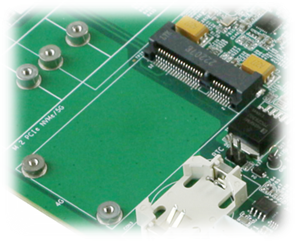

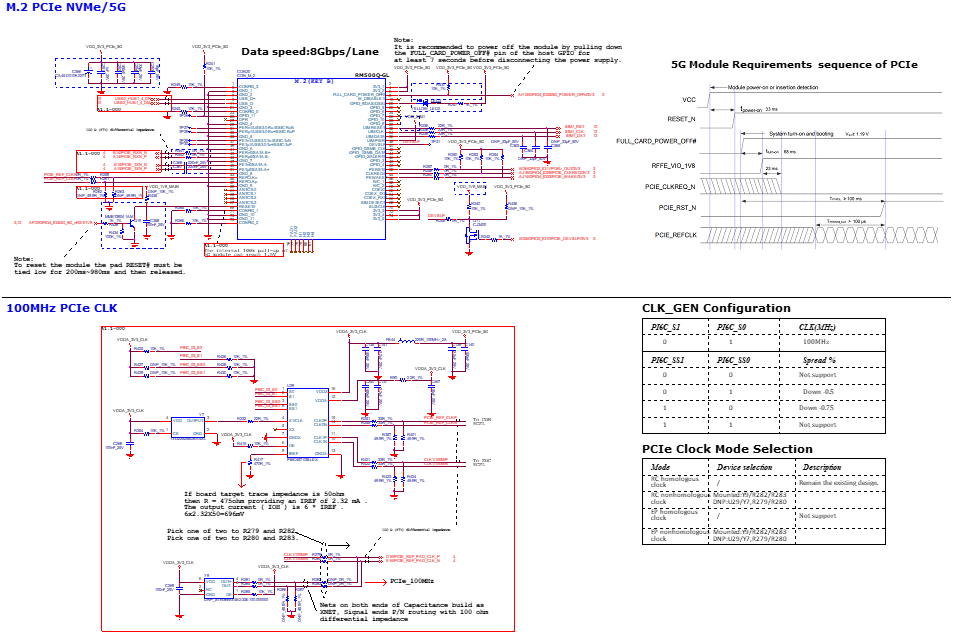

21 M.2 PCIe NVMe/5G接口

CON20为NVMe固态硬盘/5G模块拓展接口,采用M.2 B Key插槽,通过PCIe 3.0总线进行拓展,支持PCIe Gen3标准,最高通信速率8Gbps,默认作为PCIe RC(Root Complex)使用。可适配移远RM500Q-GL 5G模块及M.2 B Key接口类型NVMe固态硬盘。

评估底板通过USB2.0 HUB芯片将(CH334H)USB2_HUB1总线拓展为4路USB2.0 HOST总线,将其中1路USB2_HUB1_4总线进行5G模块拓展。

评估底板采用美台(Diodes)公司的时钟芯片PI6C557-03BLEX,输出2路HCSL电平的差分时钟,其中1路差分时钟提供至M.2 PCIe NVMe/5G接口(CON20),另外1路提供至核心板内部使用。

图 78 M.2 PCIe NVMe/5G接口实物图

图 79 M.2 PCIe NVMe/5G接口电路设计

设计注意事项:

(1) 为保证稳定的VDD_3V3_PCIe_5G电源输出,推荐使用EC2232E(U6)进行独立供电。

(2) 5G模块和4G模块共用4G/5G Micro SIM卡座(CON19),采用插卡自弹形式,不带检测引脚,使用时需正确插入相应的Micro SIM卡。

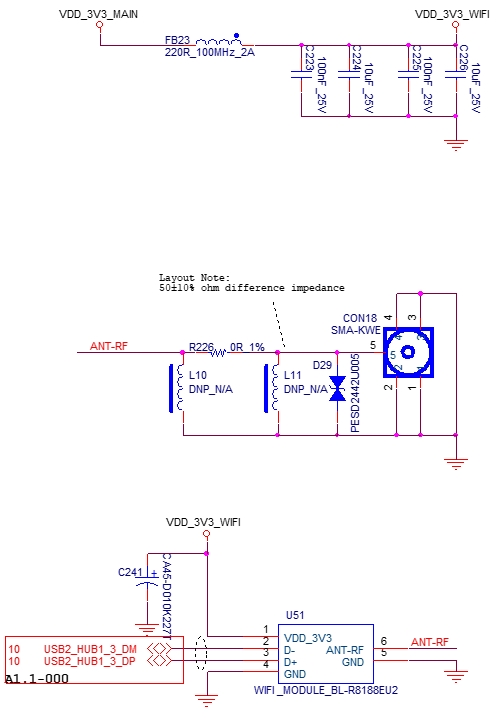

22 WIFI模块

U51为板载WIFI模块,型号为必联公司的BL-R8188EU2,采用邮票孔连接方式。评估底板通过USB2.0 HUB芯片(CH334H)将USB2_HUB1总线拓展为4路USB2.0 HOST总线,将其中1路USB2_HUB1_3总线进行WIFI模块拓展。

图 80 WIFI模块实物图

CON18为WIFI SMA接口,用于外接WIFI模块的2.4G天线。

图 81 WIFI SMA接口实物图

图 82 WIFI模块电路设计

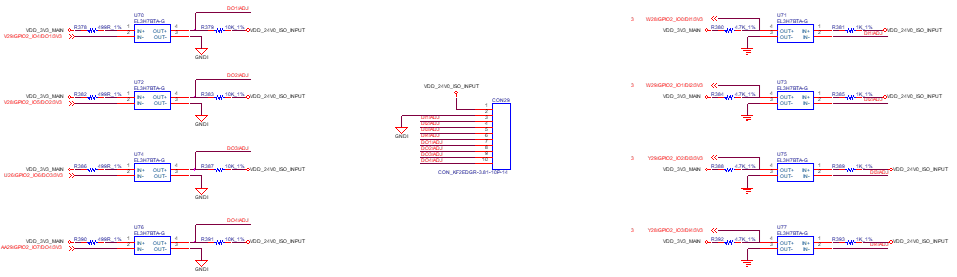

23 DI/DO接口

CON29为光耦隔离DI/DO接口,采用10pin规格、3.81mm间距绿色端子方式,引出4路开关量输入和4路开关量输出。

DI/DO接口的VDD和GNDI引脚电源输入范围为DC 3~24V。当开关量输入3~24V信号时,将会识别为高电平;当开关量输入1V以下信号时,则会识别为低电平。开关量输出为3~24V高电平或1V以下低电平信号。

图 83 DI/DO接口实物图

图 84 DI/DO接口电路设计

24 EXPORT拓展接口

评估底板提供1路拓展IO信号接口J12。采用2x 20pin规格排针方式,间距为2.54mm,引出POR_B、I2C、SPI、CLK、EARC、GPIO 3V3/1V8等拓展信号。

备注:EXPORT接口引出的IO信号电平并不一致,使用时请确认所选用信号的电平标准。

图 85 EXPORT接口实物图

图 86 EXPORT接口电路设计

设计注意事项:

(1) B6/GPIO1_IO02/PMIC_WDOG_B/PU/3V3、D6/GPIO1_IO03/PMIC_nINT/3V3和AD28/GPIO2_IO19/PMIC_SW_EN/PU/1V8在核心板内部已连接至PMIC(电源管理芯片),底板设计时请勿连接至其他功能。