再述时序约束

- 一、为什么要加时序约束?

- 二、时序分析是什么?

- 三、时序分析的一些基本概念

- 三、 时序分析的一些基本公式

一、为什么要加时序约束?

一次笔者在调试HDMI输出彩条,出现彩条时有时无现象,笔者视频输出芯片的驱动时钟使用的是FPGA内部晶体振荡器输出的,而采用PLL输出时钟则无此现象,由此可以断定问题原因在时钟不稳,或者FPGA输出时钟与数据不满足视频驱动芯片的建立和保持时间造成的。经过测量,确实发现时钟和数据出现不稳定现象。

由此可见,如果不见时序约束会造成逻辑功能不稳定,甚至故障。

二、时序分析是什么?

时序分析就是设计者首先提出时序要求,软件工具去分析,目前的代码、布线策略、器件等级是否满足设计者要求。如满足,达到设计者要求。如不满足,要么修改代码,要么降低时序要求。

三、时序分析的一些基本概念

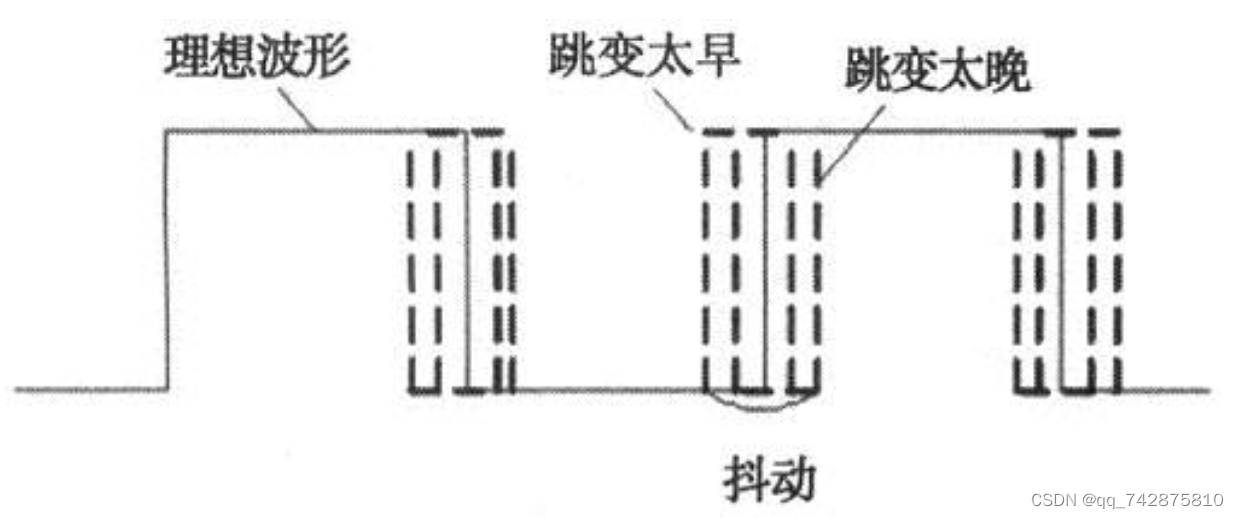

1.什么是时钟抖动?

时钟抖动的英文是clock jitter。意思是时钟周期在正确位置的左右摆动。

2.什么是时钟偏差?

时钟偏差英文是clock skew。时钟传输到源端寄存器和目标端寄存器的时间差叫时钟偏差。

3.什么是时钟的不确定性?

时钟不确定性英文是clock uncertainty。时钟的不确定性由skew和jitter导致的。

set_clock_uncertainty -from clk0 -to clk0 0.500

该约束含义是设计时钟 clk0 全部时钟间路径的裕量需严格地设置在 500ps,以使设计的

建立和保持抗噪声能力更强

三、 时序分析的一些基本公式

1.什么是数据到达时间?

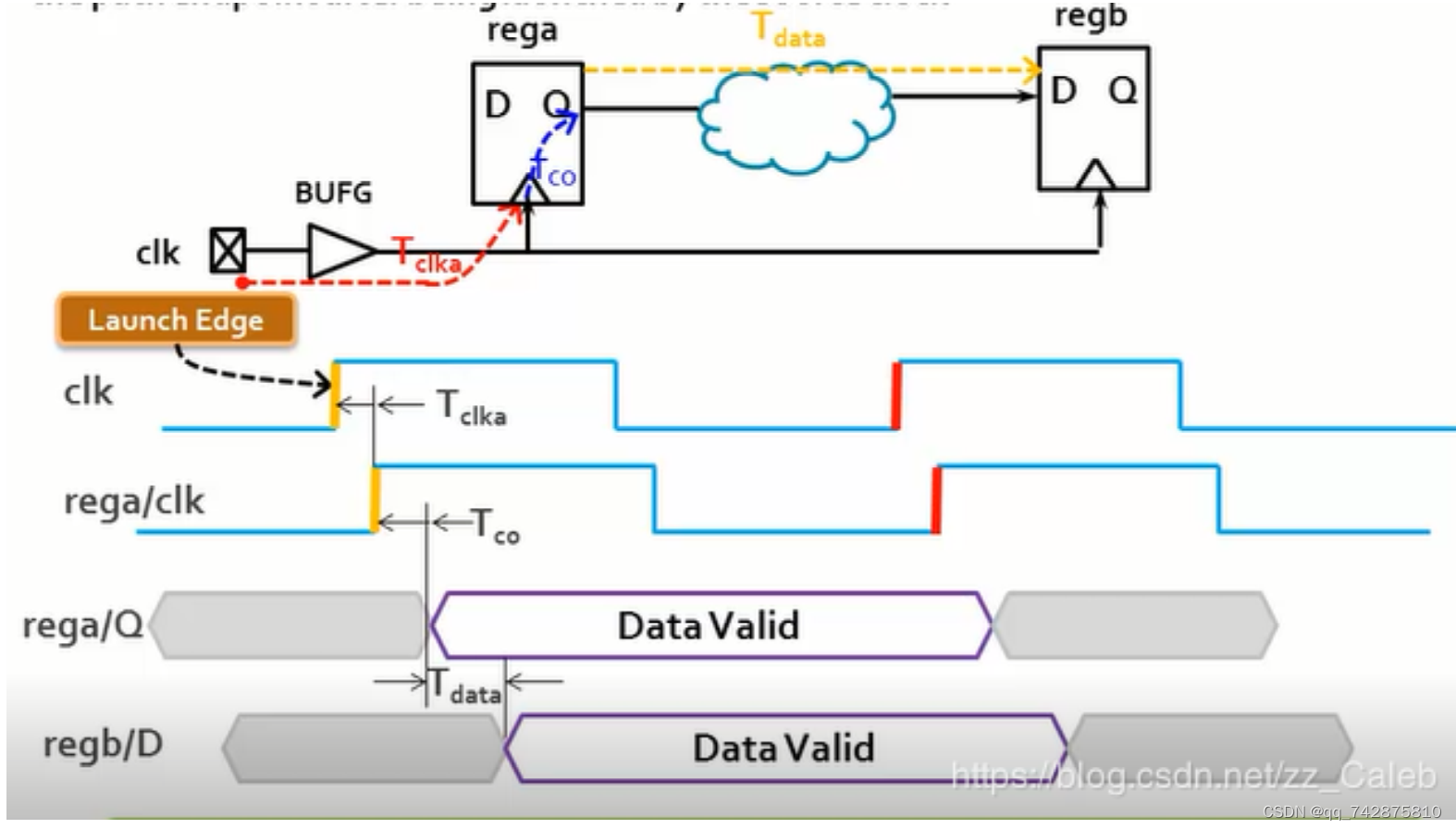

答:数据从发送沿发送,到达采样寄存器的D端口,经历的时间叫数据到达时间。发送沿是0时间点。

2.数据从发送沿到达采样寄存器的D端口,经过了那些路径?经过的路径延时即就是数据到达延时。

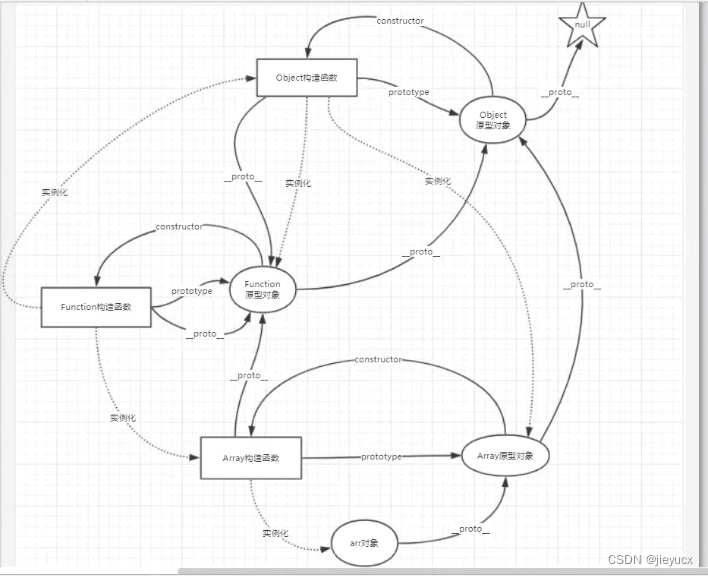

发送寄存器的传输延时Tco,组合逻辑延时Tdata,时钟传输延时Tclka(可忽略)。所以数据到达时间 Data Arrival Time = Tclka + Tco + Tdata。如下图。

3.时钟到达时间?

从概念上分析,数据在捕获沿采样。所以理论时钟的到达时间应该是一个周期,时钟的传输延时可以忽略。

Clock Arrival Time = 采样沿时间+ Tclkb。

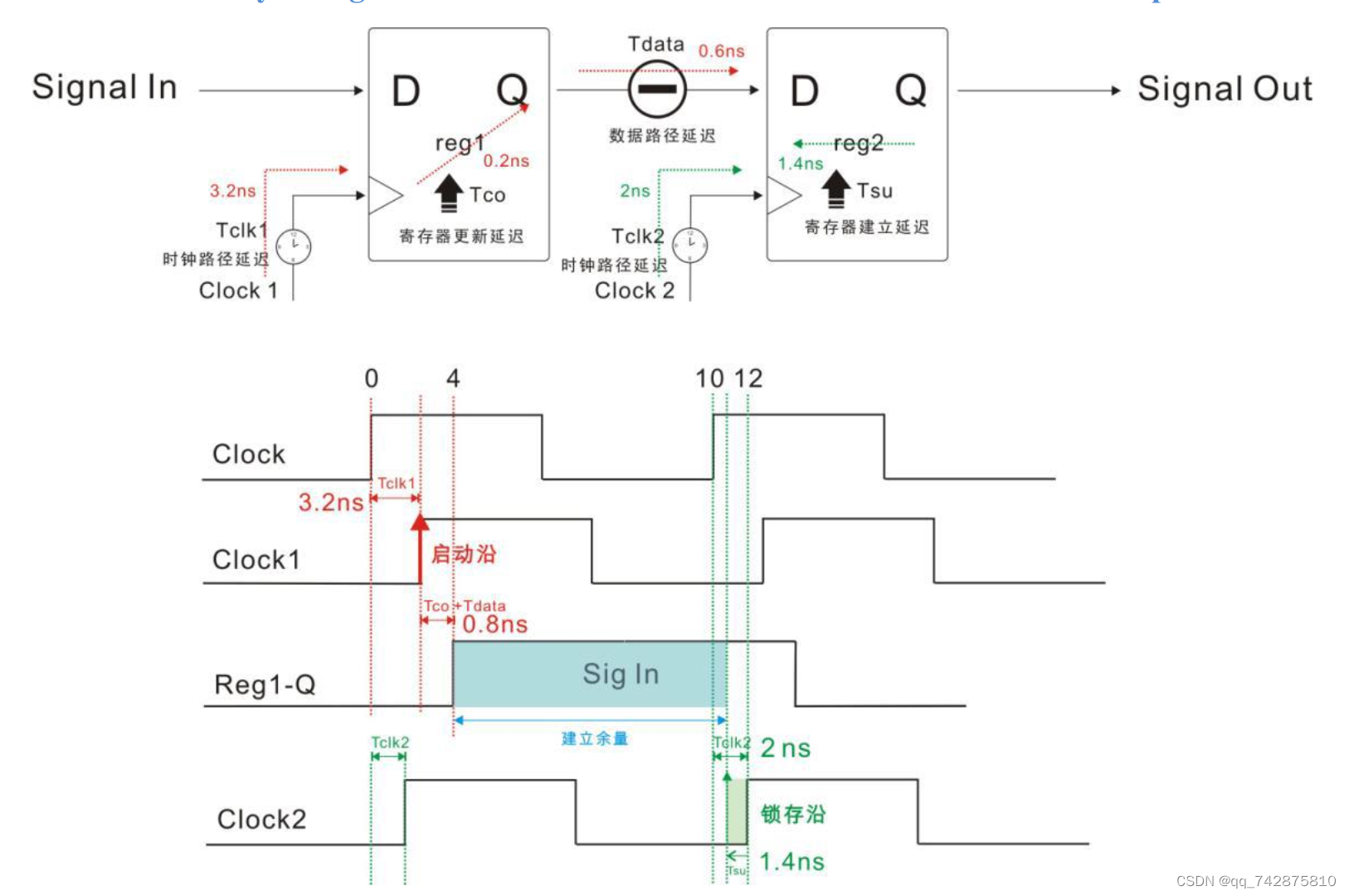

4.建立时间裕量

数据要求到达时间-数据实际到达时间=建立时间裕量。

建立时间裕量为正,说明数据能被正确采样。反之,不能被正确采样。如下图。

忽略时钟传输延时。

数据要求到达时间=Tclk-Tsu。

数据实际到达时间=Tco+Tdata

Setup Slack = Data Required Time - Time Arrival Time

建立时间裕量=数据要求到达时间-数据实际到达时间

=Tclk-Tsu-(Tco+Tdata)

=10-1.4-0.8-0.6

=7.2ns

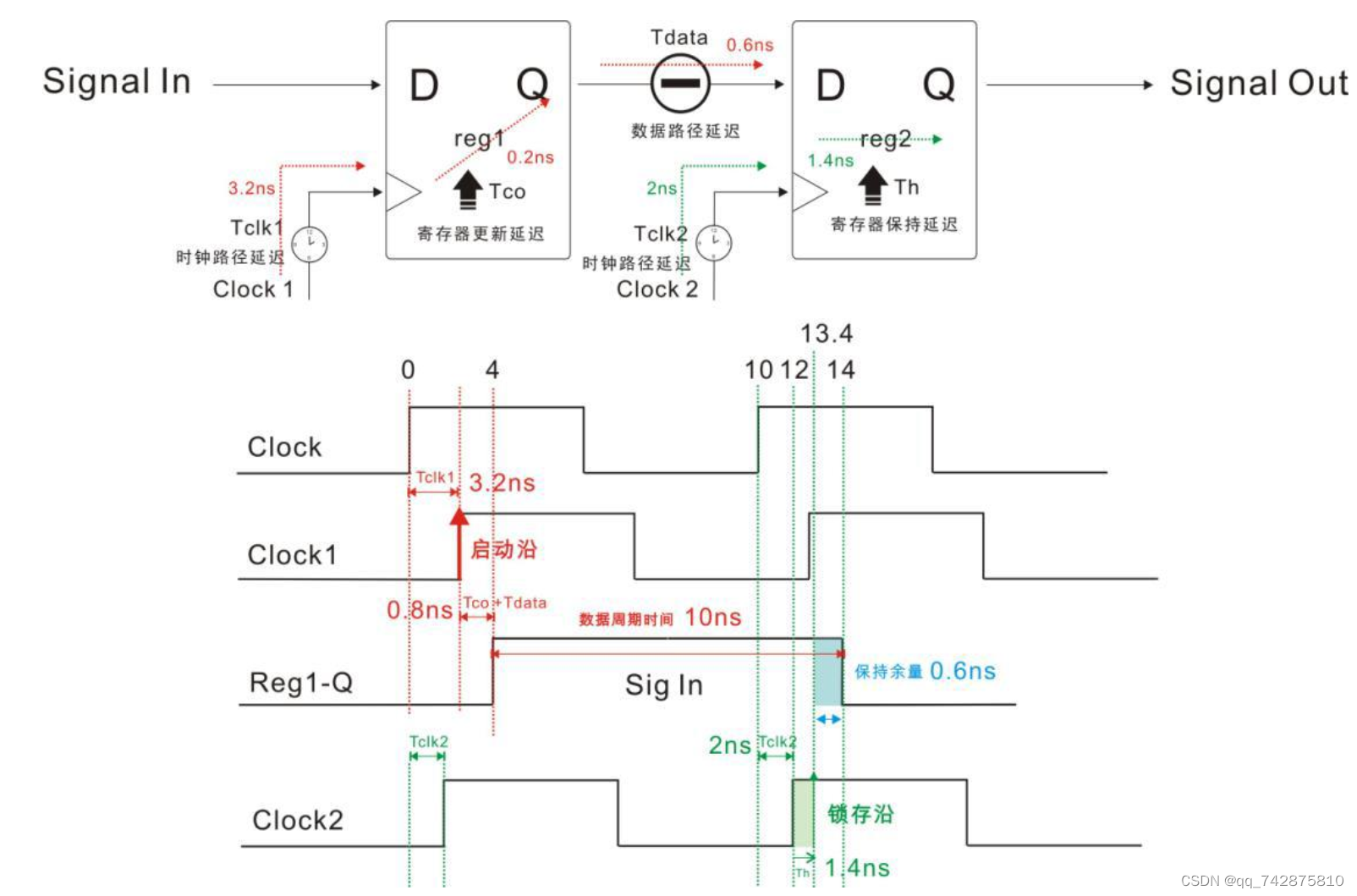

4.保持时间裕量

一般情况下忽略时间传输延迟,但是本例给出的数据正好让保持时间为0,所以加上时钟传输延时。

数据保持时间=Tclk1+Tco+Tdata+Tclk(数据保持稳定一个时钟周期)

数据要求保持时间=Tclk2+Tclk+Th(时钟沿后还要保持一定时间)

保持时间裕量=数据保持时间- 数据锁存(获取|读取)时间

保持余量 Hold Slack = 数据保持时间- 数据锁存(获取|读取)时间

=3.2+0.2+0.6+10-(2+10+1.4)

=0.6ns  5.多周期路径

5.多周期路径

大多数情况下,我们对时序分析是依照单周期来分析的,即本时钟周期发送数据,下一个时钟周期采样数据。但是,在一些情况下,源端发送数据后,目标端隔几个周期才回采样到正确的数据。比如数据传输链路复杂,运算复杂。比如乘法器,给出乘数和被乘数后,需要等待几个周期后才能获得正确的结果,如果在下一个周期去读数据,会读到一个错误的数据。同样时序约束如果按照单周期约束,也会报时序不满足。

不设置多周期路径约束的后果有两种:一是按照单周期路径检查的结果,虚报时序违规;二是导致布局布线工具按照单周期路径的方式执行,虽然满足了时序规范,但是过分优化了本应该多个周期完成的操作,造成过约束。过约束会侵占本应该让位于其他逻辑的布局布线资源,有可能造成其他关键路径的时序违规或时序余量变小。

在多周期路径的建立时间( Setup Time)检查中, 时序分析软件会按照用户指定的周期数延长Data required Time,放松对相应数据路径的时序约束,从而得到正确的时序余量计算结果;在保持时间( Hold Time)检查中, 时序分析软件也会相应地延长Data Required Time,不再按照单周期路径的分析方式执行(不再采用launch edge最近的时钟沿,而是采用latch

edge最近的时钟沿),这就需要用户指定保持时间对应的多周期个数。