目录

一、前言

二、工程设计

2.1 设计代码

2.2 综合结果

2.3 仿真结果

一、前言

计数器是较为基础的逻辑,很多其他逻辑可依靠计数器实现,如控制器,分频。原理为通过统计时钟脉冲的个数来输出计数值。

二、工程设计

2.1 设计代码

工程设计以计数20的计数器为例

module Counter(clk,out,rst);

input clk,rst;

output reg [5:0] out;

always@(posedge clk,negedge rst)

begin

if(!rst)

out<=6'b0;

else if(out==6'd19) //此处设置计数值,因为计数输出从0开始,因此如果计数20,则计数到19即结束

out<=6'b0;

else

out<=out+1'b1;

end

endmodule测试代码

module Counter_tb( );

reg clk,rst;

wire [5:0] out;

initial

begin

rst=1;

clk=0;

#50 rst=0;

#30 rst=1;

end

always #1 clk=~clk;

Counter Counter_test(.clk(clk),.rst(rst),.out(out));

endmodule

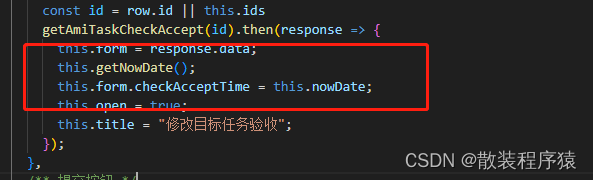

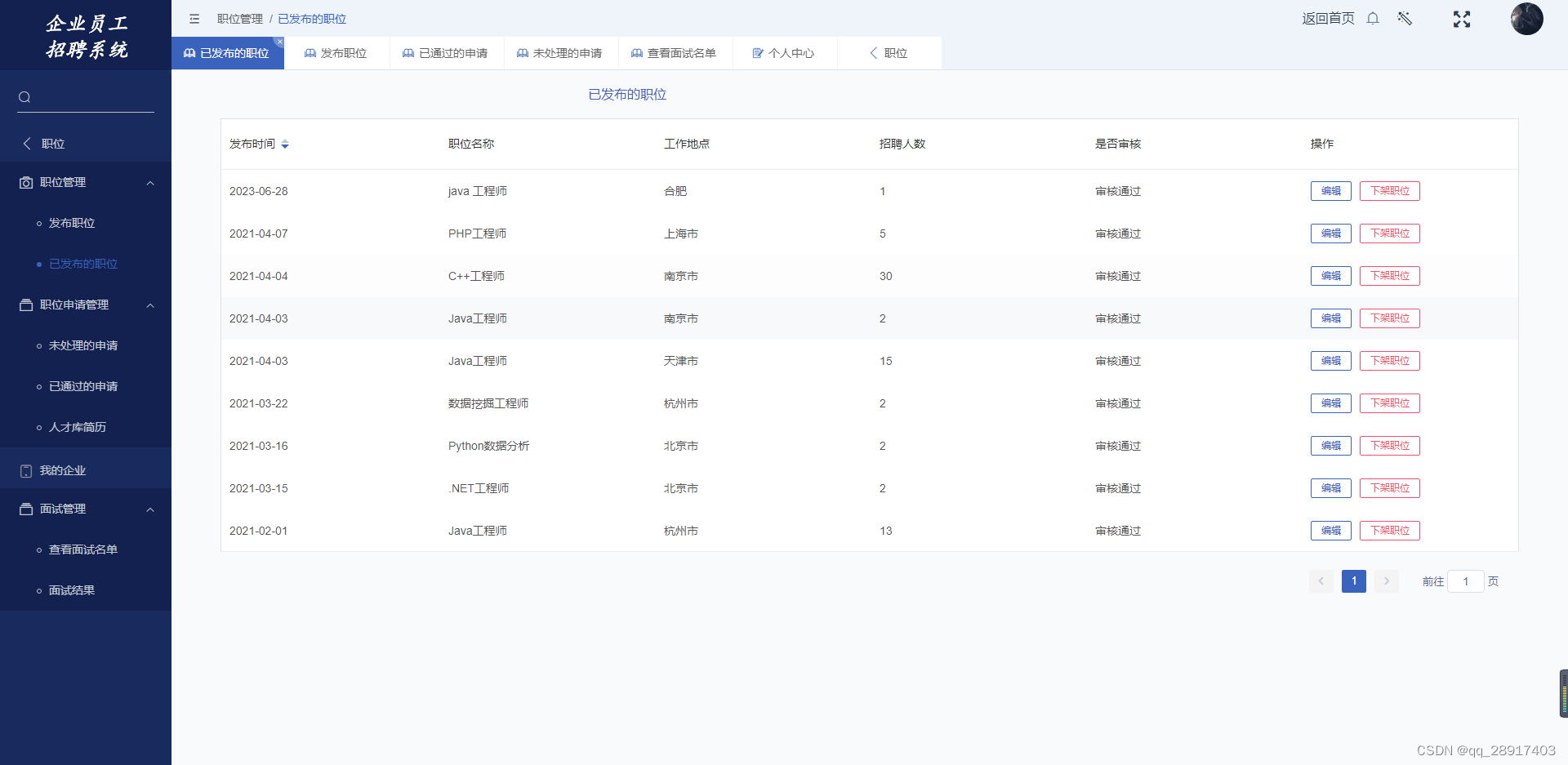

2.2 综合结果

综合后的网表可知,6位的计数器由6个LUT和6个FF实现,多余的一个连接到rst的LUT1是用于取反,因为rst低电平复位

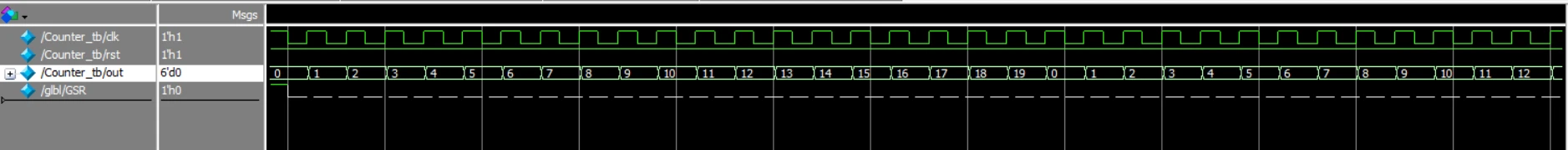

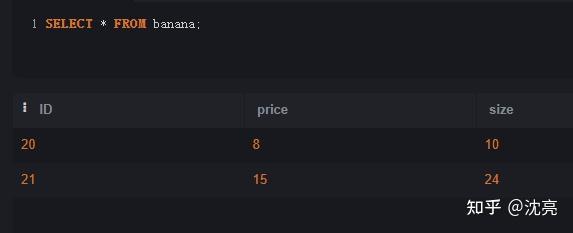

2.3 仿真结果

下图仿真中,计数输出out在计数到19后从0开始,符合预期