文章目录

- 前言

- 一、仿真的步骤

- 二、使用步骤

- 1.PDS编译仿真库

- 2.编写仿真tb文件

- 3.选择行为仿真

- 4.查看观察窗口

- 5.修改代码后重新编译

- 总结

前言

@和原子哥一起学习FPGA

开发环境:正点原子 ATK-DFPGL22G 开发板

参考书籍:

《ATK-DFPGL22G之FPGA开发指南_V1.1.pdf》

个人学习笔记,欢迎讨论

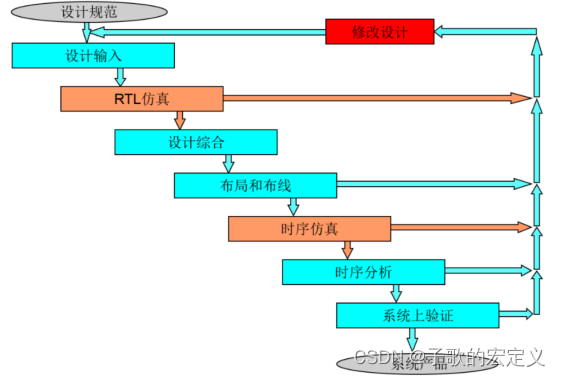

一、仿真的步骤

需要仿真的位置:

功能仿真:设计综合前进行 RTL 级仿真,称为综合前仿真,也称为前仿真或功能仿真。在完成一个设计的代码编写工作之后,可以直接对代码进行仿真,检测源代码是否符合功能要求。

时序仿真:在布局布线后进行的仿真称为布局布线后仿真,也称为后仿真或时序仿真。时序仿真可以真实地反映了逻辑的时延与功能,综合考虑电路的路径延迟与门延迟的影响,验证电路能否在一定时序条件下满足设计构想的过程,是否存在时序违规。

二、使用步骤

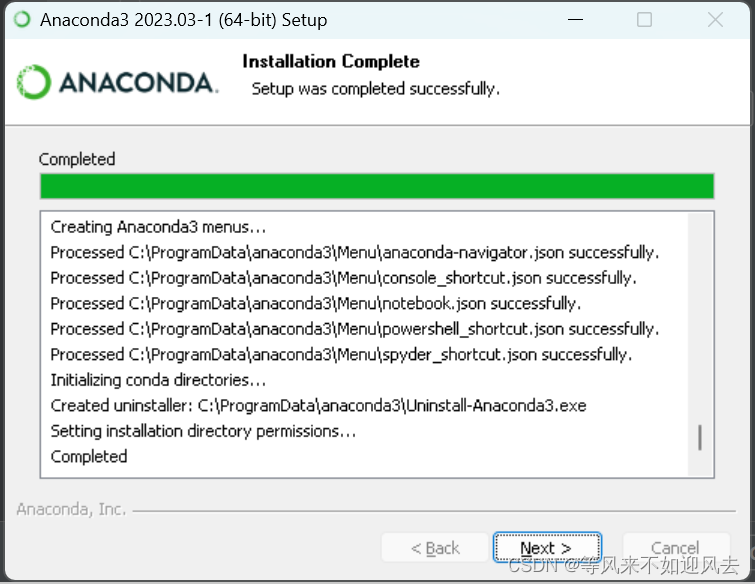

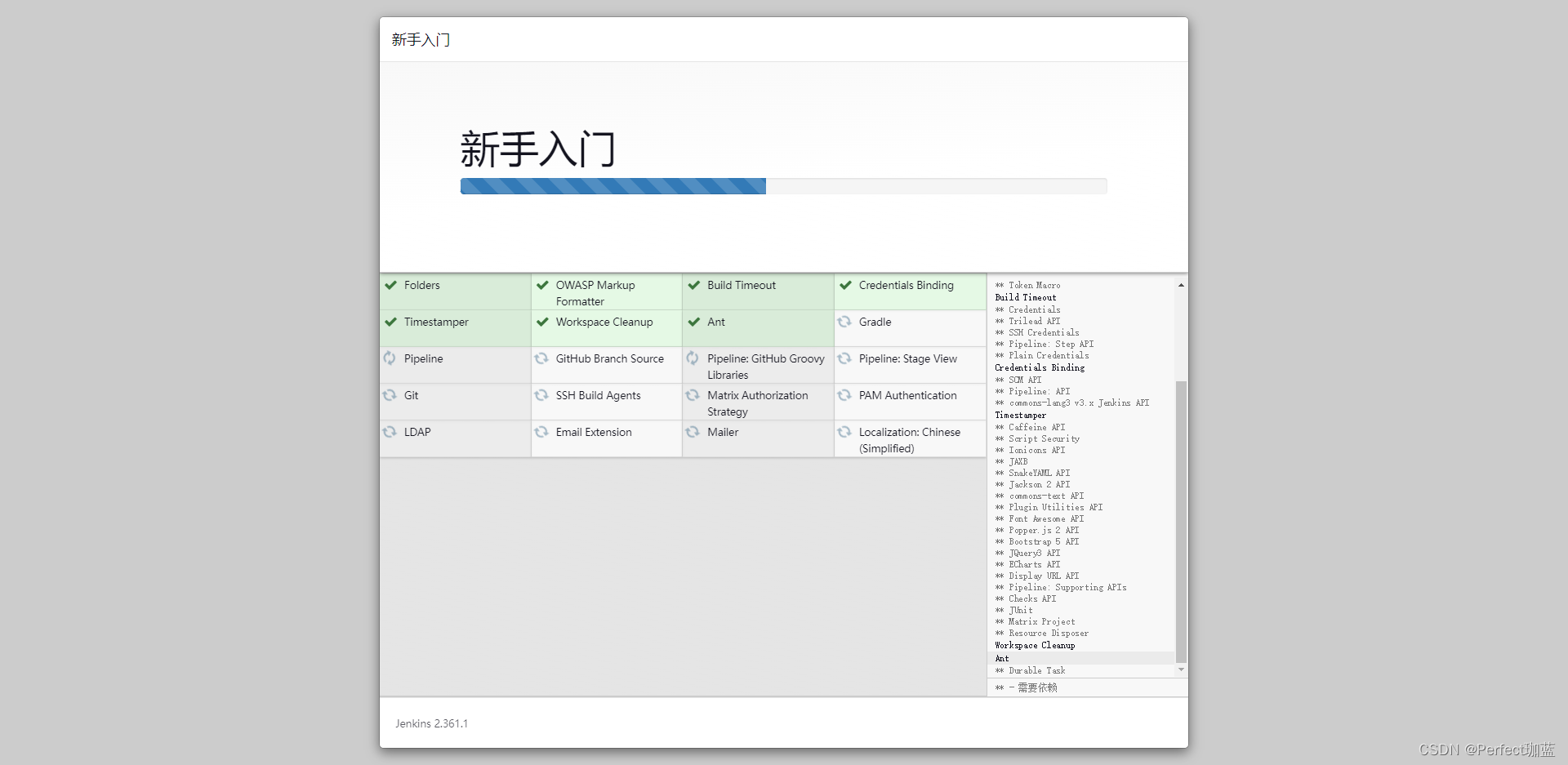

1.PDS编译仿真库

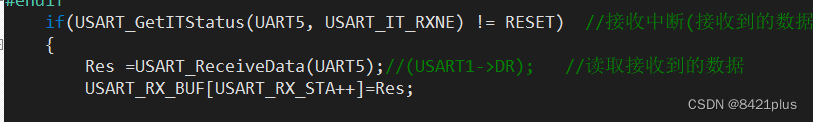

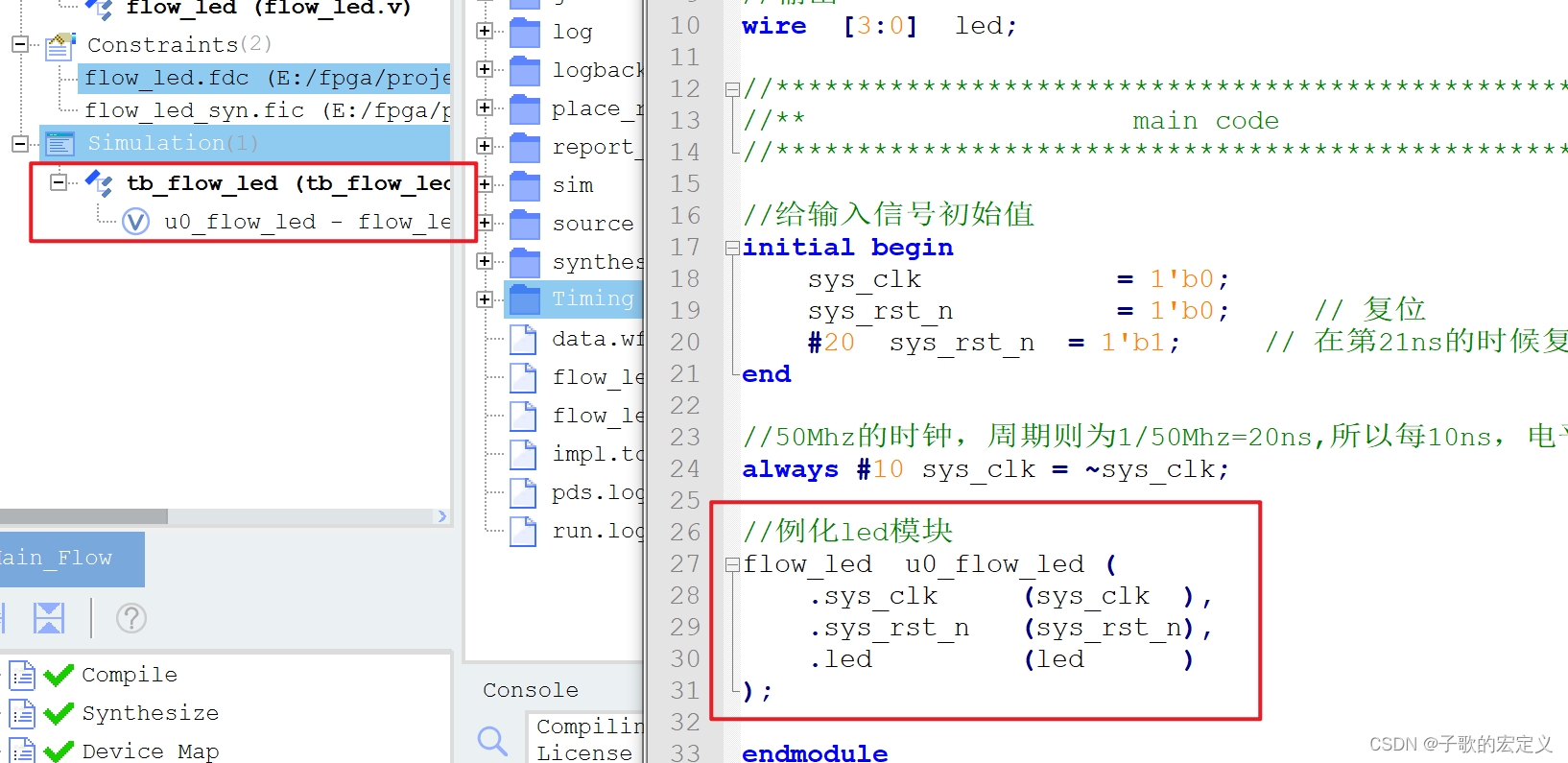

2.编写仿真tb文件

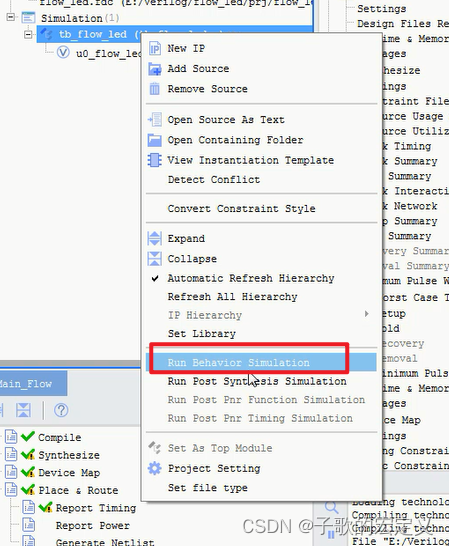

3.选择行为仿真

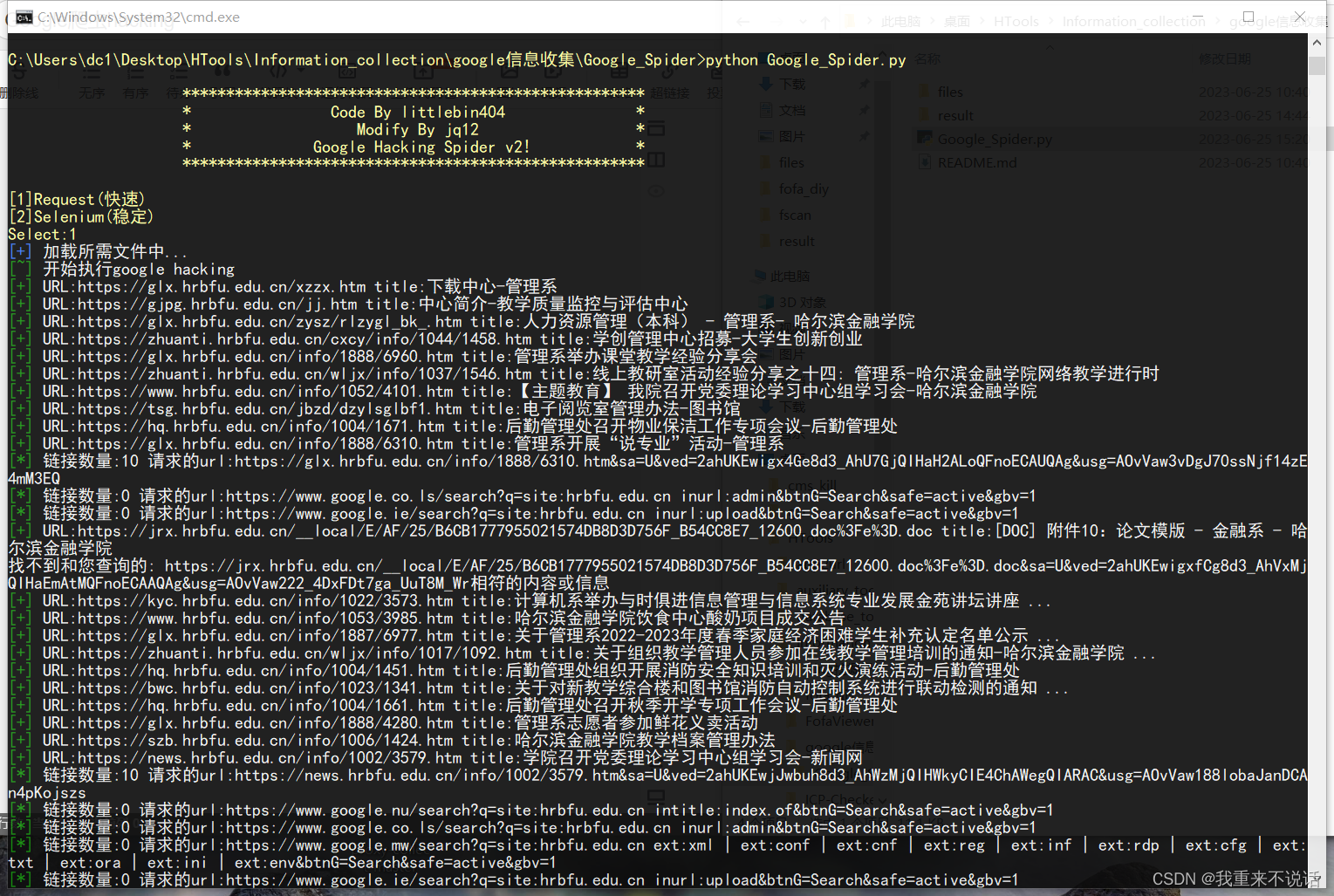

启动了第三方仿真软件

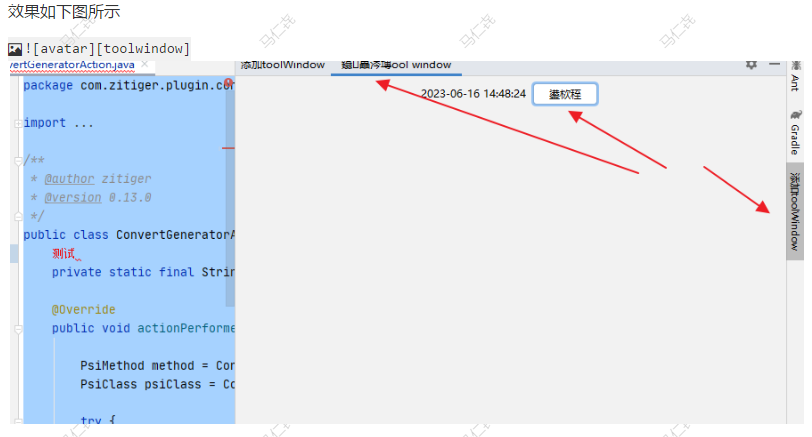

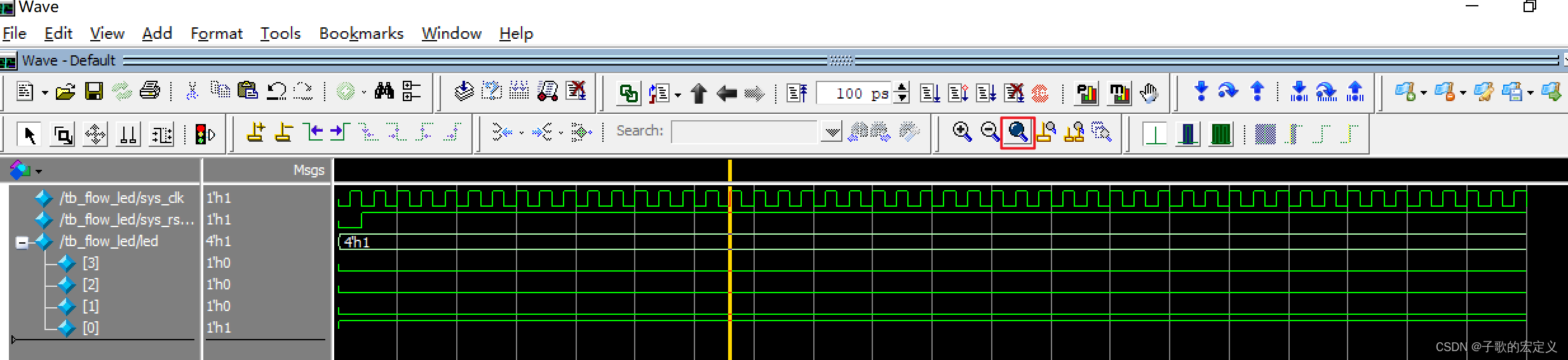

4.查看观察窗口

5.修改代码后重新编译

总结

调试手段+1,调试会使用FPGA资源,不能长时间调试,所以可以使用仿真来进行功能等验证,也可以用于测试