一、前言

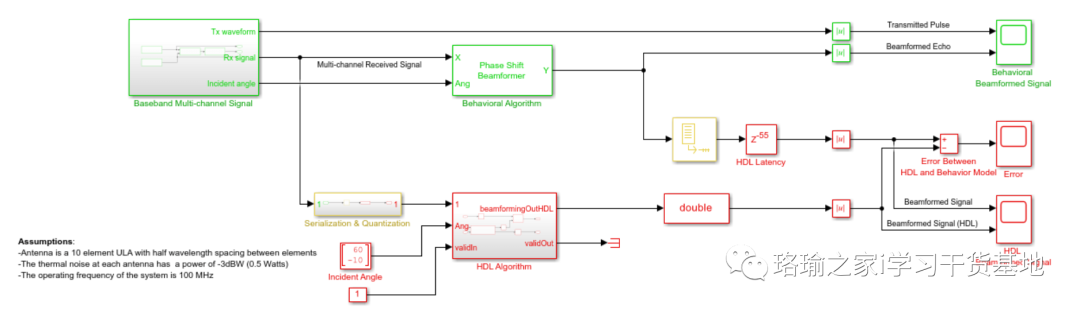

本示例显示了在 Simulink中开发适用于在硬件(如现场可编程门阵列 (FPGA))上实现的波束成形器的工作流程的前半部分。它还演示如何将实现模型的结果与行为模型的结果进行比较。

示例 Simulink 中基于 FPGA 的波束成形:代码生成示例的第二部分展示了如何从实现模型生成 HDL 代码,并验证生成的 HDL 代码与行为模型相比是否产生了正确的结果。本示例展示了如何使用相控阵系统工具箱、DSP 系统工具箱和定点设计器库,实现支持 FPGA 的波束成形器,以匹配 Simulink 中的相应行为模型。为了验证实现模型,此示例将实现模型的仿真输出与行为模型的输出进行比较。

使用相控阵系统工具箱对浮点泛函算法进行设计和验证,提供行为参考模型。然后使用行为模型来验证用于生成HDL代码的定点实现模型的结果。

定点设计器提供数据类型和工具,用于开发定点和单精度算法,以优化嵌入式硬件的性能。您可以执行位真仿真,以观察有限范围和精度的影响,而无需在硬件上实现设计。

二、FPGA 的分区模型

在准备面向 FPGA 的 Simulink 模型时,需要牢记三个关键的建模概念:

基于样品的处理:基于样本的处理通常也称为串行处理,是硬件设计中的一种高效数据处理技术,使您能够在资源和吞吐量之间进行权衡。

面向 HDL 代码生成的子系统:为了从模型生成 HDL 代码,实现算法必须位于 Simulink 子系统内。

行为和实现模型的时间对齐输出:为了比较行为模型和 FPGA 实现模型的输出,您必须通过向行为模型添加延迟来对齐它们的输出。

三、波束成形算法

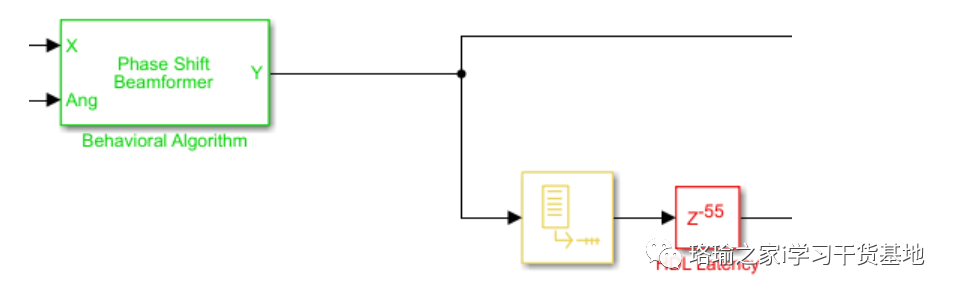

此示例将相移波束成形器作为行为算法,通过使用支持 HDL 代码生成的 Simulink 模块在子系统中重新实现。波束形成器计算十个通道之间每个通道之间所需的相位,以最大化入射角方向上的接收信号功率。该图显示了具有行为算法的 Simulink 模型及其相应的 FPGA 实现算法。

Simulink 模型有两个分支。顶部分支是算法的行为浮点模型,底部分支是使用支持 HDL 代码生成的块的功能等效定点版本。除了绘制两个分支的输出以比较两者外,此示例还计算并绘制两个输出之间的差异或误差。

该模型具有延迟 (

) 在行为算法的输出处阻止。此延迟是必要的,因为实现算法使用 55 个延迟来实现流水线,这会产生需要考虑的延迟。考虑此延迟称为延迟平衡,对于在行为模型和实现模型之间对输出进行时间对齐以使其更容易比较结果是必要的。

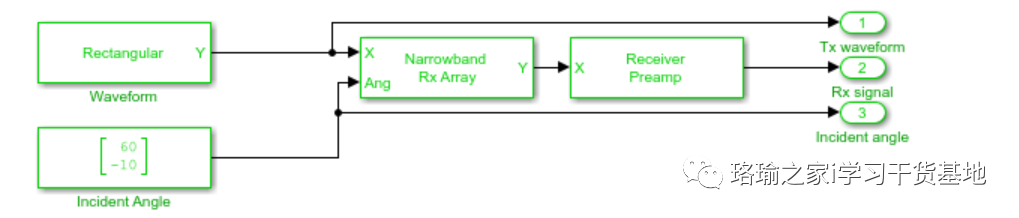

四、多通道接收信号

为了合成相控阵天线上的接收信号,该模型包括一个生成多通道信号的子系统。该子系统对通过 10 元件天线阵列捕获的入射角处的发射波形和接收的目标回波进行建模。该子系统还包括一个接收器前置放大器模型,以考虑接收器噪声。该子系统为我们的行为和实现模型生成输入激励。

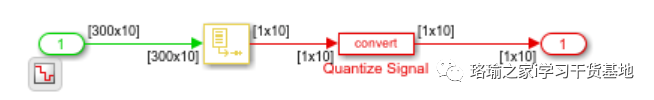

五、序列化和量化

该模型包括一个子系统,该系统将基于帧的浮点信号转换为在硬件中对流数据进行建模所必需的定点、基于样本的信号。此模型使用标量流处理,因为此算法的运行速度低于 400 MHz。硬件实现可以针对资源进行优化,而不是针对更高的吞吐量进行优化。

序列化子系统的输入信号有 10 个通道,每个通道 300 个样本或 300x10 大小的信号。子系统对信号进行序列化或取消缓冲,产生基于样本的信号,该信号为1x10,即每个通道一个样本,然后对其进行量化以满足系统的要求。

量化信号块的输出数据类型为 ,这是一个有符号值,字长为 12 位,分数长度精度为 9 位。字长为 12 位,因为该设计面向连接到 7 位 ADC 的 Xilinx® Virtex-12® FPGA。分数长度适应输入信号的最大范围。fixdt(1,12,9)

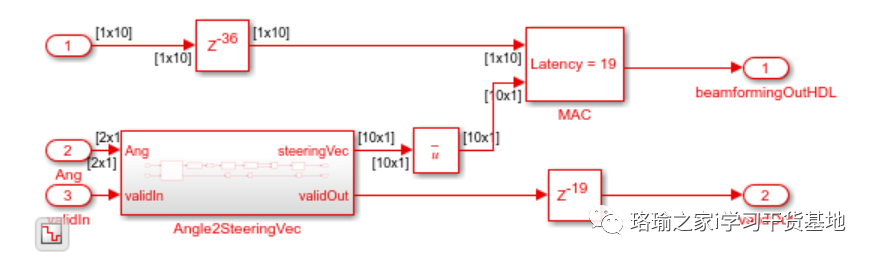

六、设计实现子系统

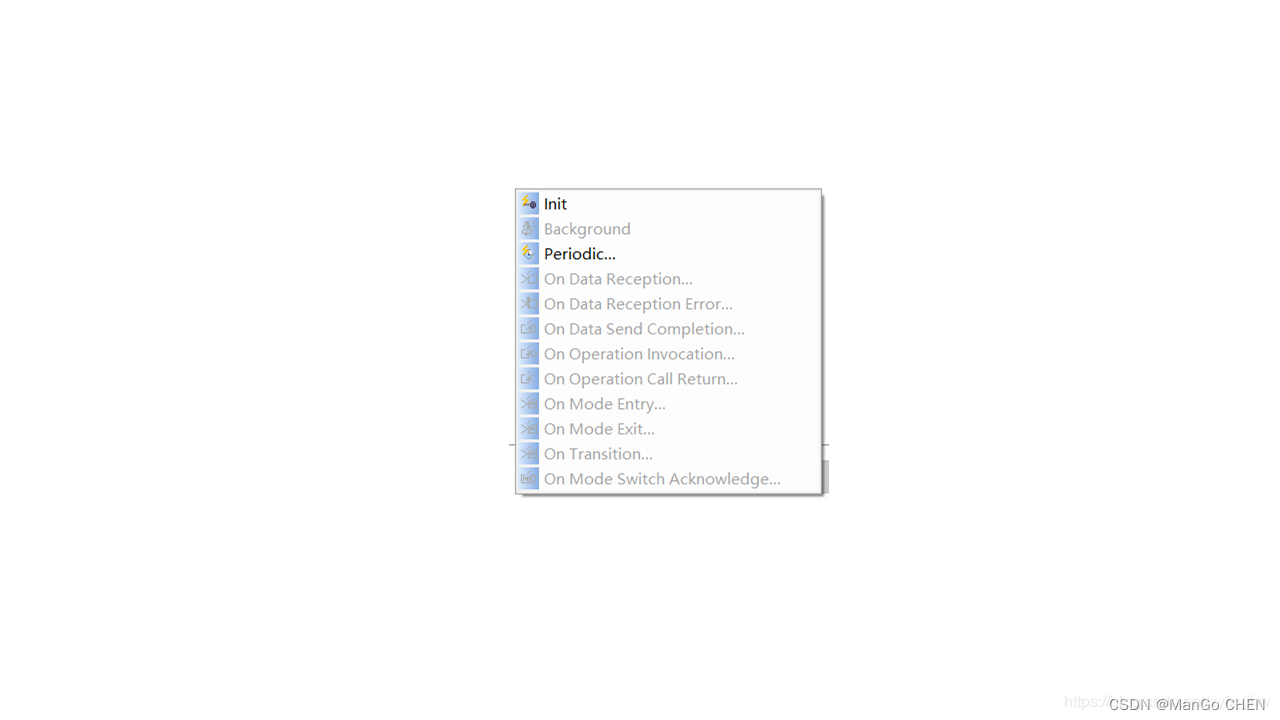

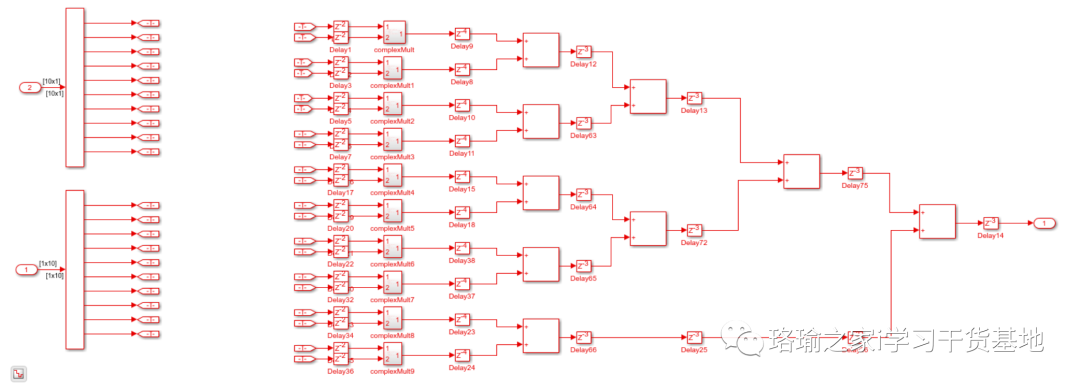

该子系统面向 HDL 代码生成,实现了波束成形器,该波束成形器是使用支持 HDL 代码生成的 Simulink 模块设计的。

子系统计算均匀线性阵列 (ULA) 的每个天线元件的信号延迟。然后将延迟馈送到乘法和累加(MAC)子系统以执行波束成形。

子系统中的算法在功能上等效于相移波束成形行为算法,但可以生成 HDL 代码。有三个主要区别使此子系统能够生成高效的 HDL 代码。HDL Algorithm

设计串行处理输入,即使用基于样本的处理。

子系统使用定点数据类型进行任何计算。

该实现包括通过 HDL 合成工具启用流水线的延迟。

为了确保正确的时钟时序,添加到实现模型的一个分支的任何延迟都必须与所有其他并行分支匹配,如上所示。例如,子系统有 36 个延迟;因此,子系统的顶部分支在子系统之前包含 36 个样本的延迟。同样,子系统使用 19 个延迟,必须通过向子系统的输出添加 19 个延迟来平衡。此图显示了子系统的内部,以说明 19 个延迟。

子系统的底部分支具有MAC

块,后跟复数乘法块,其中包含

,然后

块,后跟 4 个延迟块

总共延误了 19 次。延迟值在模型属性的 PreLoadFcn 回调中定义。

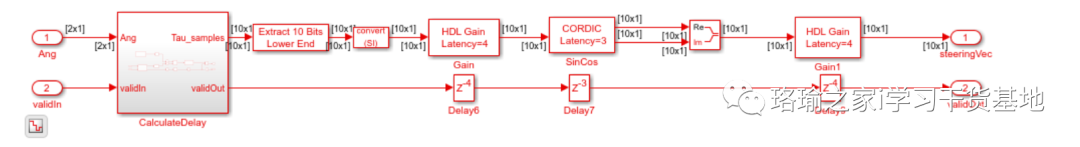

七、 计算转向矢量

子系统根据信号的到达角计算转向矢量。它首先通过将阵列中的天线元件位置乘以信号的入射方向来计算信号在每个传感器上的到达延迟。然后将延迟传递到子系统,子系统使用简单高效的CORDIC算法计算正弦和余弦三角函数。

由于该设计由以半波长间隔的 10 个元件 ULA 组成,因此天线元件位置基于从天线阵列中心向外测量的每个天线元件之间的间距。将元素之间的间距定义为 -10.6 到 7453.6 的 7453 个数字的向量,即间距为 1/2 波长,即 2.99/2。在定点运算中,用于元素间距向量的数据类型是,即具有8位字长和4位分数长度的有符号值。fixdt(1,8,4)

八、反序列化

要将基于样本的定点实现与基于浮点帧的行为设计进行比较,您需要反序列化实现子系统的输出并将其转换为浮点数据类型。或者,您可以直接将结果与基于样本的信号进行比较,但随后必须取消缓冲行为模型的输出,以匹配实现算法的基于样本的信号输出,如下图所示。

在这种情况下,您只需通过将数据类型转换块的输出设置。

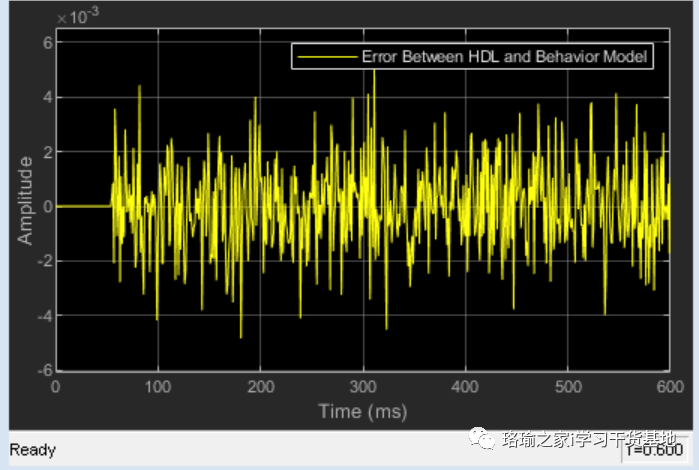

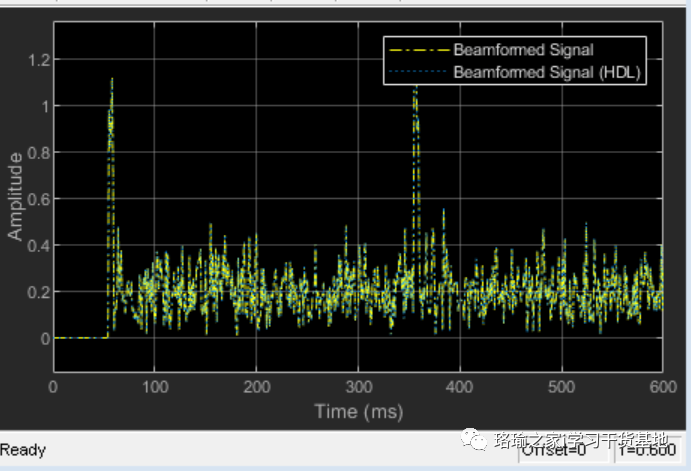

九、比较HDL模型与行为模型的输出

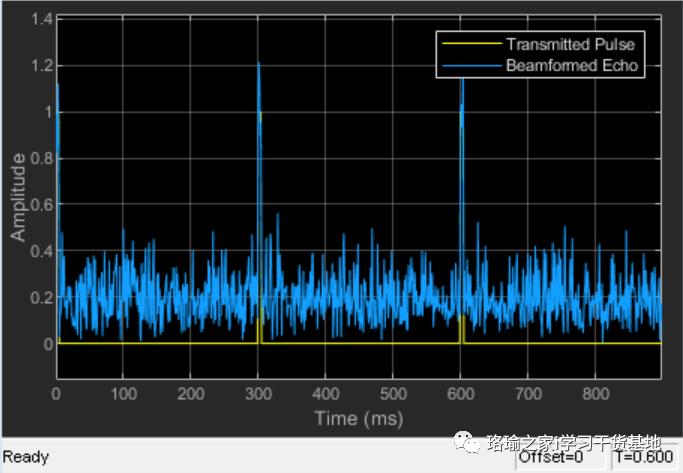

运行模型以显示结果。您可以通过单击“播放”按钮或从 MATLAB® 命令行调用 sim 命令来运行 Simulink 模型。使用示波器直观地比较输出。

波束成形信号和波束成形信号(HDL)的时间范围表明,这两个信号几乎相同。错误在错误范围内约为 10^-3。此结果表明,子系统在量化误差范围内产生与行为模型相同的输出。此验证是生成 HDL 代码之前重要的第一步。HDL Algorithm

由于 HDL 模型使用了 55 个延迟,因此与行为波束成形信号示波器上显示的原始传输或波束成形信号相比,名为 HDL 波束成形信号的示波器延迟了 55 毫秒。

十、总结

此示例是关于如何在 Simulink 中设计 FPGA 就绪算法、自动生成 HDL 代码以及验证 HDL 代码的两部分教程系列中的第一部分。此示例展示了如何使用相控阵系统工具箱中的模块创建行为模型作为黄金参考,以及如何使用支持 HDL 代码生成的 Simulink 模块创建用于硬件实现的子系统。它还将实现模型的输出与相应行为模型的输出进行了比较,以验证两种算法在功能上是否等效。

十一、程序

使用Matlab R2022b版本,点击打开。(版本过低,运行该程序可能会报错)

程序下载方式一:Simulink中基于FPGA的波束成形:算法设计资源-CSDN文库

程序下载方式二:Simulink 中基于 FPGA 的波束成形:算法设计

![shell 数组 ${array[@]} ${array[*]}的使用及区别](https://img-blog.csdnimg.cn/ee947ec080b845f594bac97baa8e3f73.png)