ZYNQ 7020黑金开发板的PL端有四个LED,如下图所示。

PL端也有四个KEY,如下图所示。

本文将把这四个按键和四个LED一一对应起来,在按键按下或松开时,对应的LED产生亮或灭的信号。

在原理图中找到PL端的LED和KEY如下图所示。

通过看图可知,LED在低电平时亮,而按键KEY在按下时是低电平,因此本实验最后的呈现应当是:按下按键,对应的LED亮;松开按键,对应的LED灭。

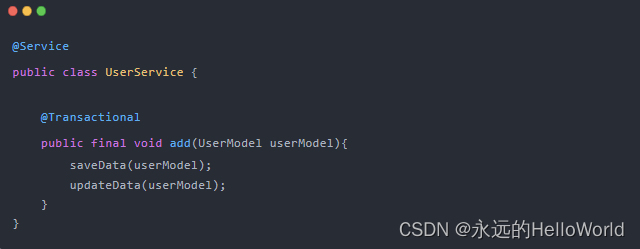

该实验对应的代码如下。

module key_led(

input clk,

input [3:0] key, //keydown value is 0, keyup value is 1

output [3:0] led //led lighten when low

);

reg [3:0] led_d1; //define two D Flip-flop

reg [3:0] led_d2;

always@(posedge clk)

begin

led_d1 <= key;

end

always@(posedge clk)

begin

led_d2 <= led_d1;

end

assign led = led_d2;

endmodule

添加了两个D触发器,第一级D触发器在时钟上升沿到来后记录按键的状态,并在下一个时钟上升沿到来后将本级D触发器的状态传递给第二级D触发器,然后第二级D触发器将值赋给LED。

其对应的RTL图如下图所示。

在到开发板上验证之前,先编写如下的仿真测试代码进行仿真。

module key_led_sim();

reg clk;

reg [3:0] key;

wire [3:0] led;

initial

begin

clk = 0;

key = 4'b1111;

#250

key = 4'b1010;

#250

key = 4'b0101;

#250

key = 4'b0001;

end

always #10 clk = ~clk;

key_led uut_key_led(

.clk(clk),

.key(key),

.led(led)

);

endmodule

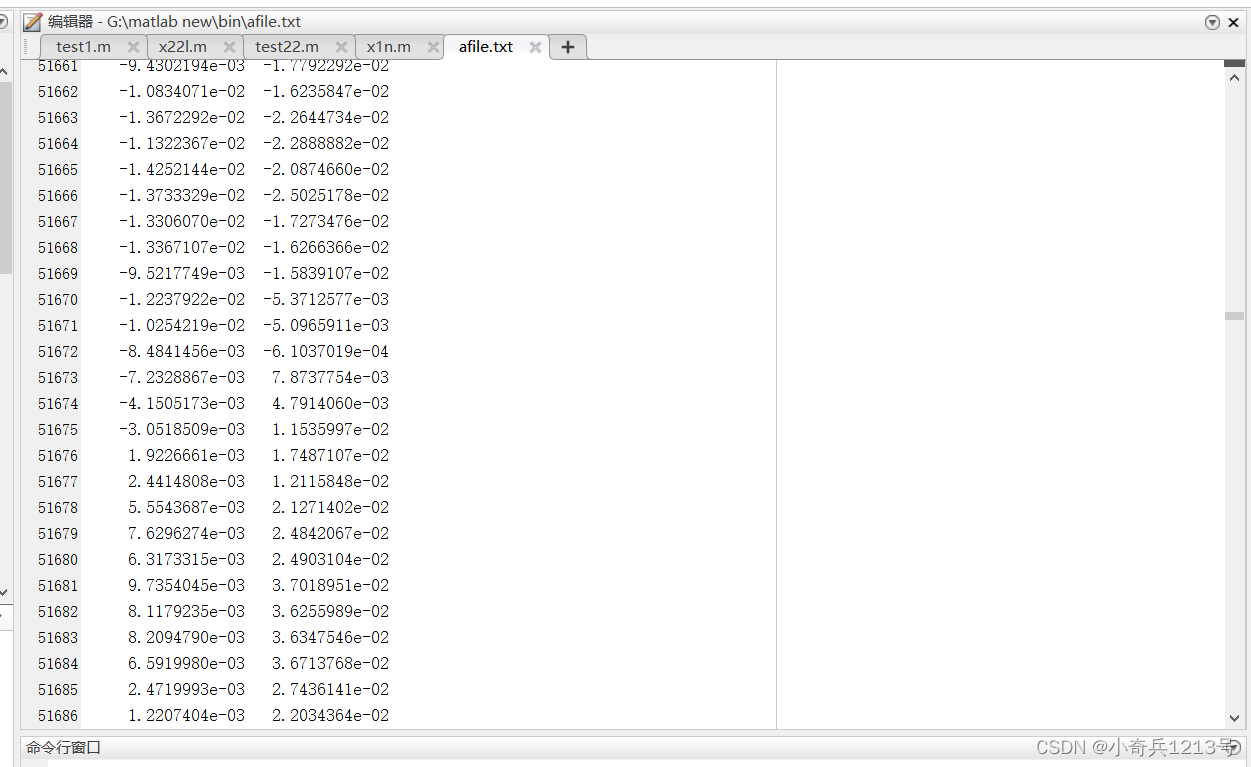

仿真结果如下图所示。

通过上述仿真结果可以看到,LED的输出是跟第二级D触发器同步的,落后第一级D触发器一个时钟周期,这与预设相一致,接下来就可以在开发板上验证了。

本实验中的引脚分配可以参照下表进行。

| 端口 | 引脚 |

|---|---|

| CLK | U18 |

| KEY1 | N15 |

| KEY2 | N16 |

| KEY3 | T17 |

| KEY4 | R17 |

| LED1 | M14 |

| LED2 | M15 |

| LED3 | K16 |

| LED4 | J16 |

分配引脚的界面如下图所示。

引脚分配完成后就可以生成比特流文件,并将其下载到开发板进行板上验证了,开发板上的验证结果如下动图所示。

按下 PL KEY1 (2/3/4)对应的 PL LED1 (2/3/4)亮,松开后对应的 LED 熄灭。

以上就是ZYNQ——按键和LED关联实验的所有内容了!

参考资料:

ZYNQ 开发平台 FPGA 教程 AX7020