目录

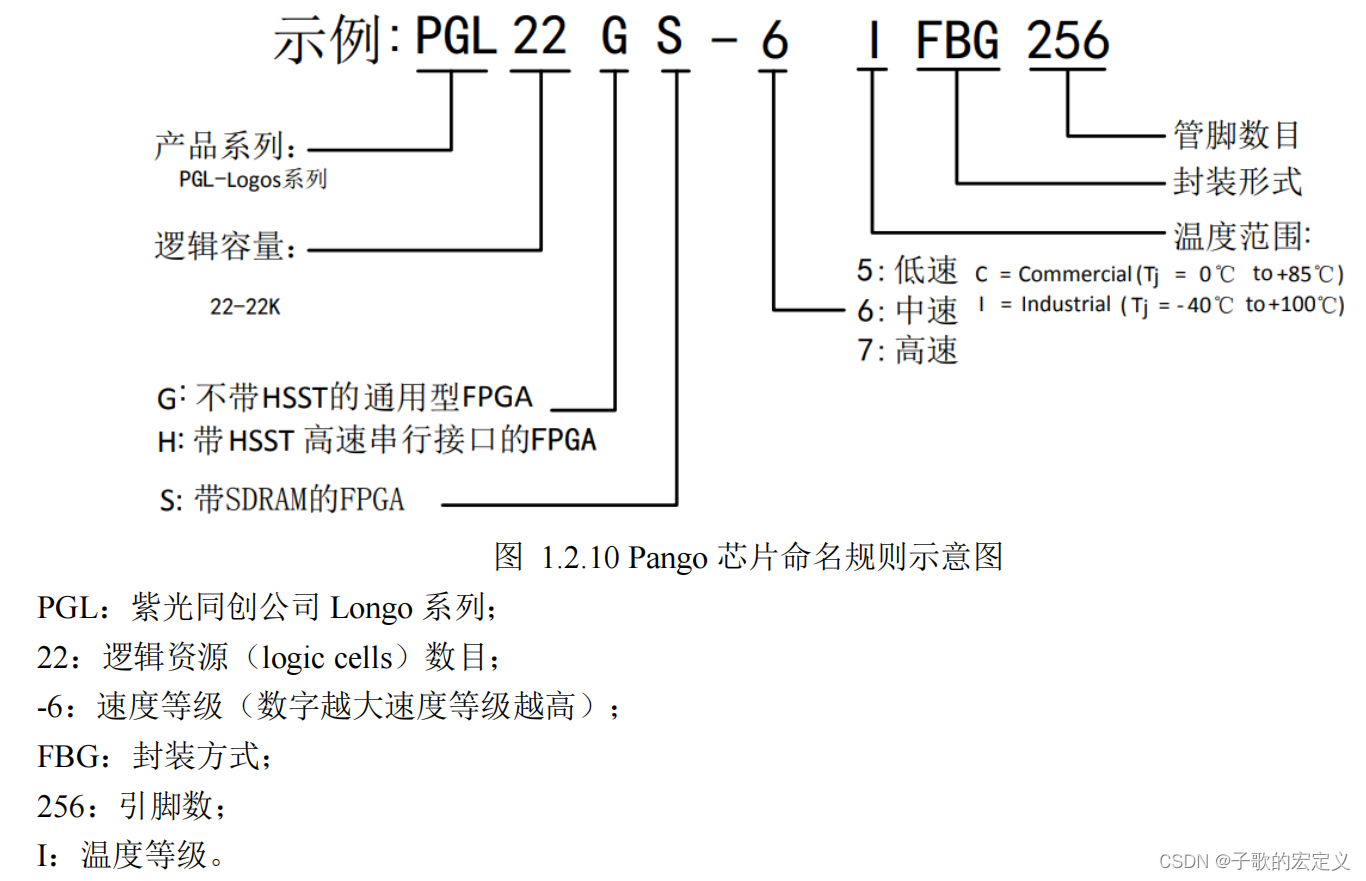

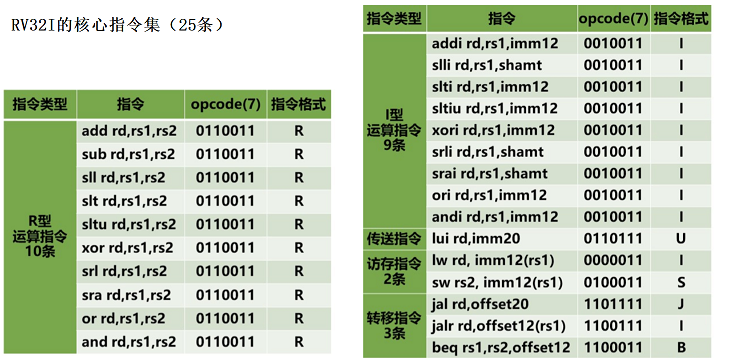

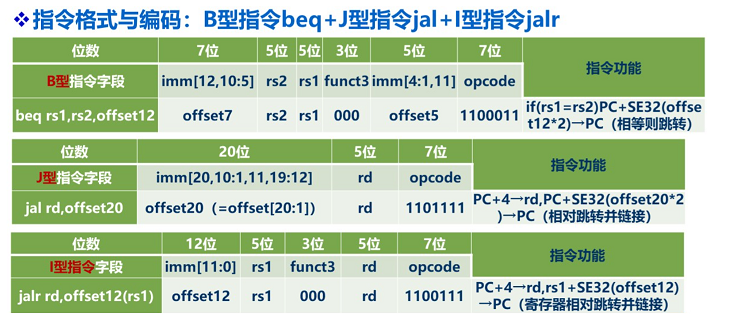

一、RISC-V模型机的目标指令集

二、RISC-V模型机的部件设计

三、运算及传送指令的数据通路设计

四、访存指令的数据通路设计

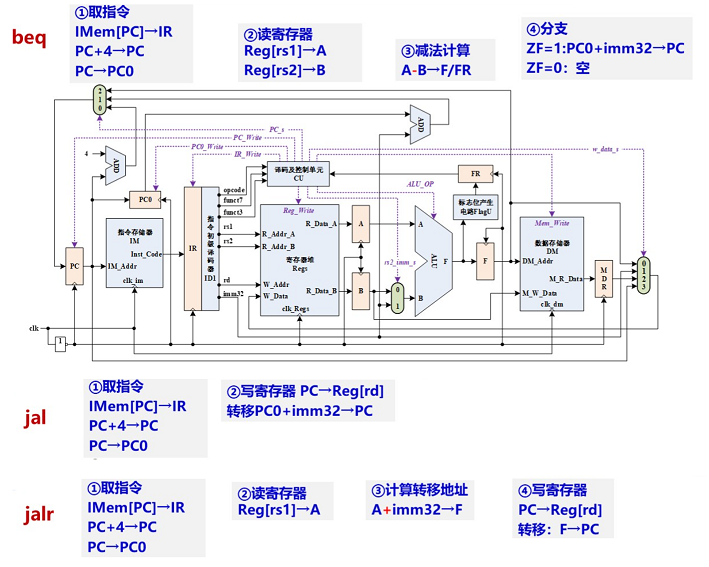

五、转移类指令的数据通路设计

六、RISC-V模型机控制单元CU的有限状态机设计

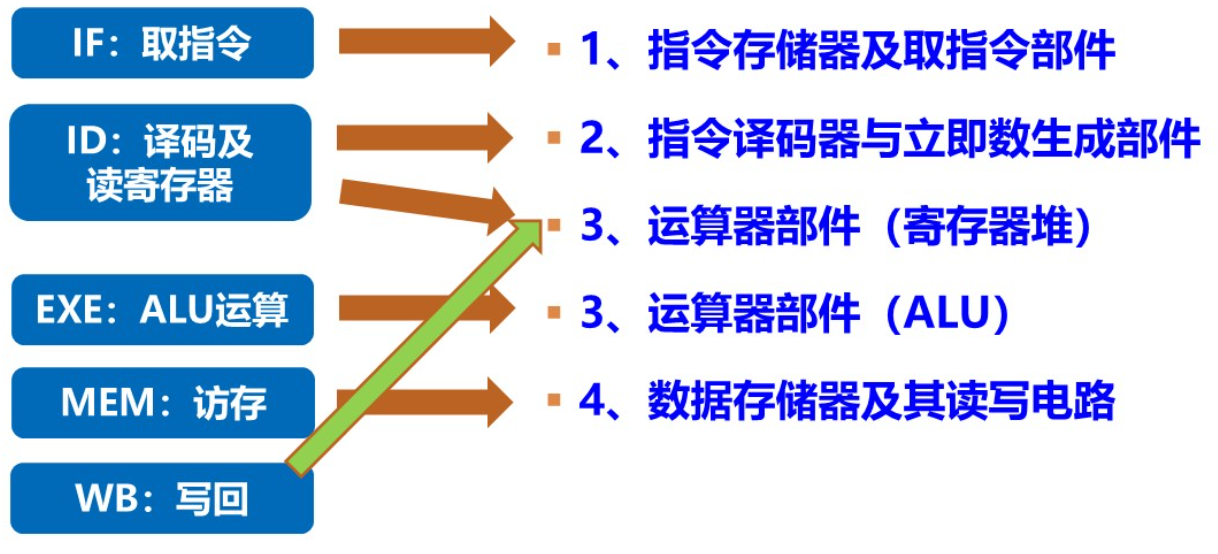

一、RISC-V模型机的目标指令集

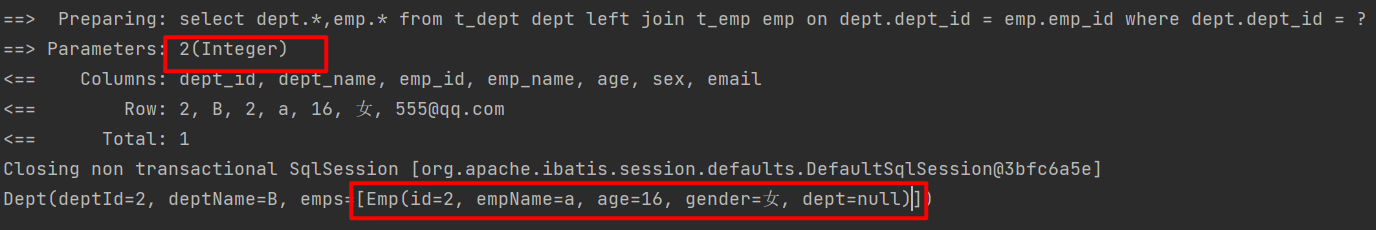

取指令并译码:根据PC从内存取出指令,PC+4 -> PC,译码

执行指令:首先根据指令字的字段,取出1~2个寄存器(rs1,rs2)内容,再根据指令具体功能,做不同操作

- 算术逻辑运算:ALU运算,写寄存器

- 传送类指令:生成立即数,写寄存器

- 访存指令:计算存储器地址(ALU运算),读/写存储器

- 转移类指令:比较数据(ALU运算),PC+偏移量 -> PC

二、RISC-V模型机的部件设计

CPU性能的重要指标:CPU速度(执行时间)

CPU执行指标 = 程序指令数 × 每条指令的时钟周期数(CPI)× 时钟周期长度

- 单周期CPU:CPI = 1,但是时钟周期很长

- 多周期CPU:CPI > 1,但是时钟周期很短,且某些硬件部件可共享

从CPU效率指标考虑,我们设计的RV32I的25条核心指令集,采用:

- 直接连接(无总线)

- 多周期CPU(性能和硬件成本优于单周期CPU)

- 哈佛结构(指令和数据分开存储)

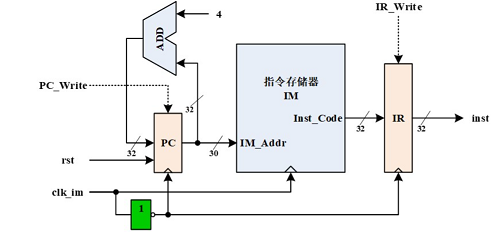

1. 指令存储器及取指令部件——取指令IF

- 程序计数器 PC:存放指令地址,32位,取指令后自增4个字节(独立加法器)

- 指令寄存器 IR:存放指令代码,32位

- Mem[PC] -> IR, PC+4 -> PC

- clk上跳沿:取指令(读存储器)

- clk下跳沿:指令置入IR,更新PC

2. 指令译码器与立即数生成器——指令译码ID

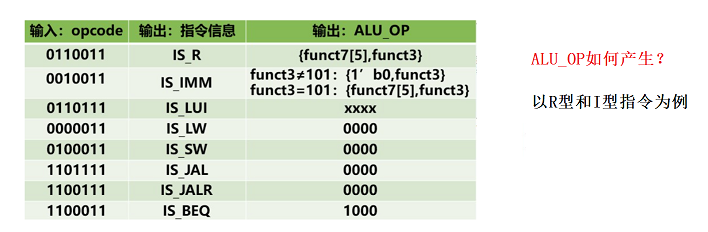

(1)指令译码器

- 初级译码器 ID1:①指令字段与格式解析器;②立即数生成器

- 二级译码器 ID2:产生指令信号、ALU_OP

(2)立即数生成器

- 立即数拼接与生成器:按照各格式,对立即数进行拼接与拓展,产生6个32位立即数

- 6选1多路选择器:按照当前指令的格式,在6个立即数中选择一个输出,记为imm32

(3)指令二级译码器

- 输入:ID1产生的opcode、func3、func7

- 输出:指令信息8个,运算码ALU_OP

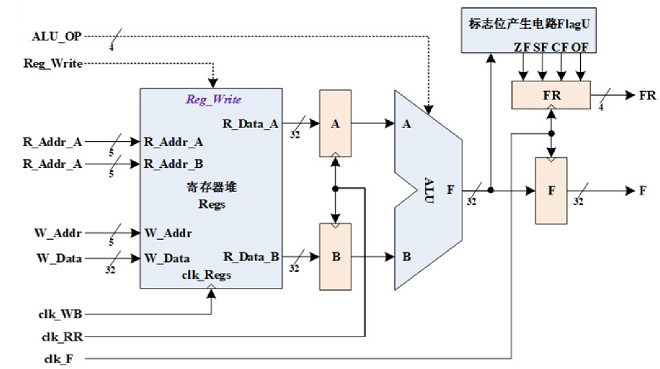

3. 运算器部件——执行EX

(1)通用寄存器堆 Regs

- 32×32位寄存器,寄存器地址5位

- 三端口:两个读端口,一个写端口(同时读出2个寄存器,写入1个寄存器)

- 读出无需时钟,写入需要时钟

- 读出的数据写入暂存器A和B,时钟clk_RR控制打入

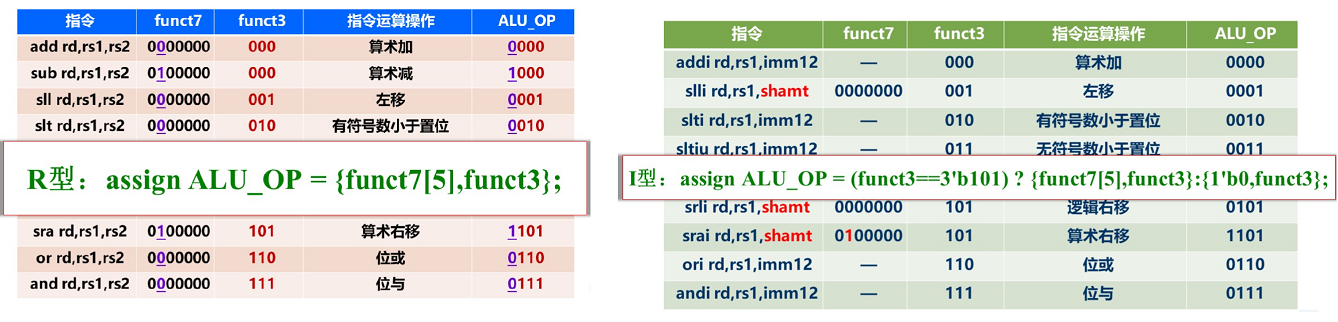

(2)多功能运算部件 ALU

- 32位,进行算术、逻辑、比较置数、移位运算

- 选择信号:运算功能码ALU_OP

- 组合逻辑电路:无需时钟信号

- clk_F:将运算结果打入暂存器F

(3)标志位寄存器 FR 及标志位产生部件 FlagU

- 组合逻辑电路

- 输入:运算结果ALU_F

- 输出:ZF、SF、CF、OF

- 标志位寄存器 FR:保存ZF、SF、CF、OF信号

- clk_F:将ZF、SF、CF、OF打入FR

(4)暂存器A、B、F

- 32位寄存器,在多周期CPU中,一个机器周期操作的结果要存到暂存器中,供下个机器周期操作使用

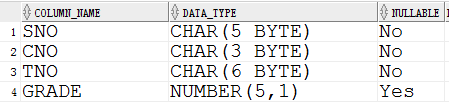

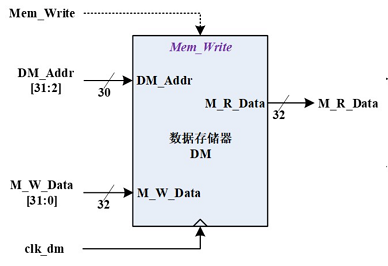

4. 数据存储器 DM

- 地址32位,数据32位,按字节编址,小端存储

- clk_dm上跳沿:Mem_Write=0(读);Mem_Write=1(写)

- DM_Addr:字地址(30位)

- M_R_Data:读出数据

- M_W_Data:写入数据

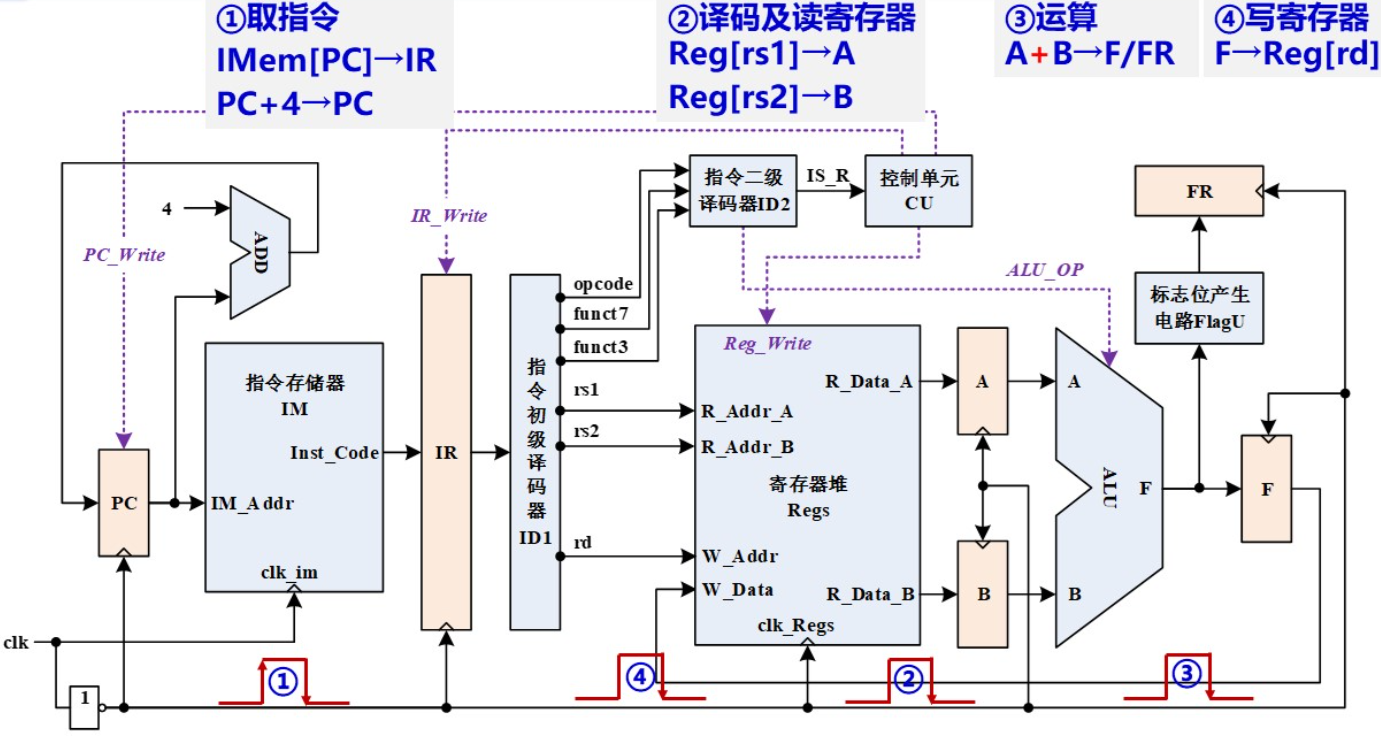

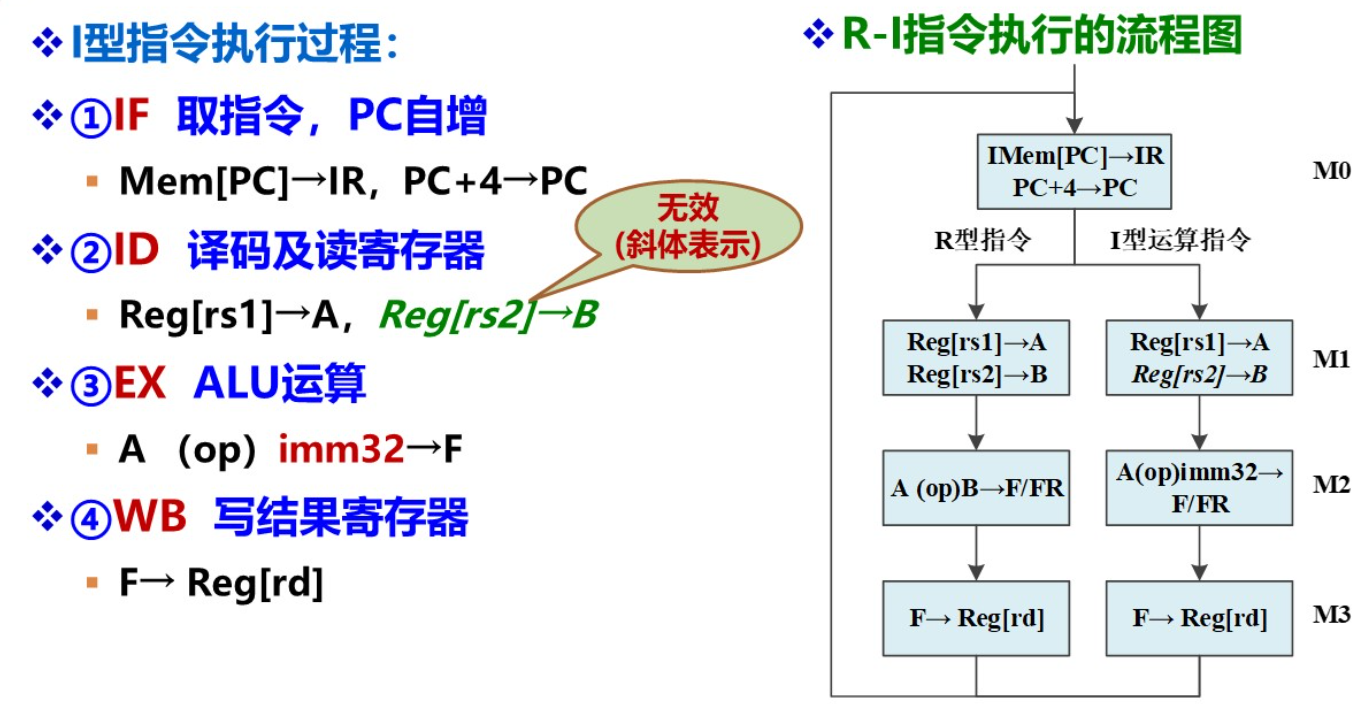

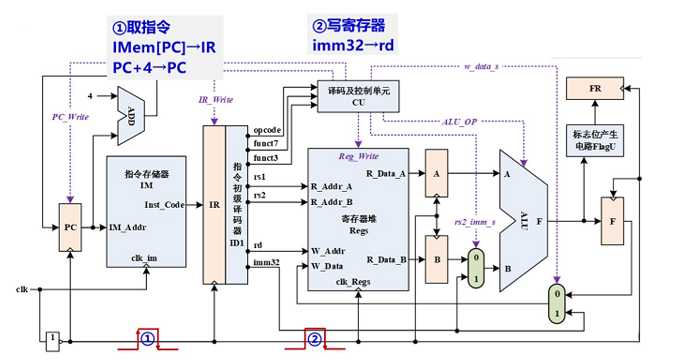

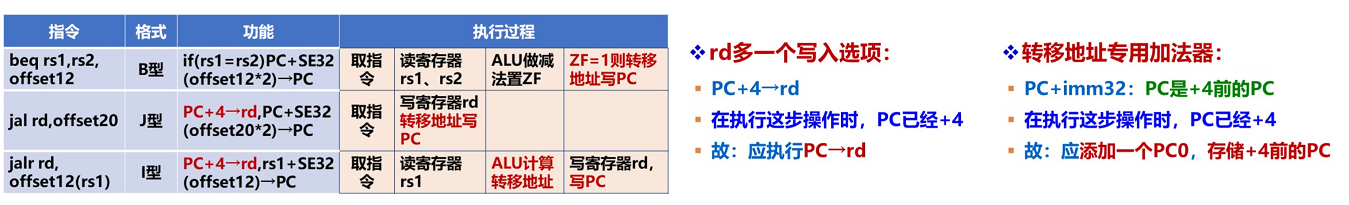

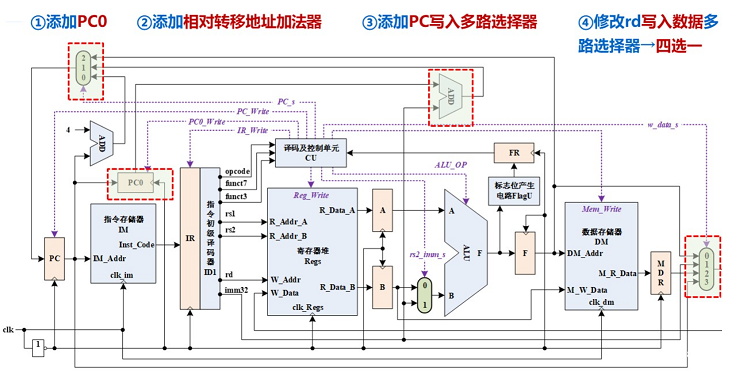

三、运算及传送指令的数据通路设计

如何连接部件?建立数据通路

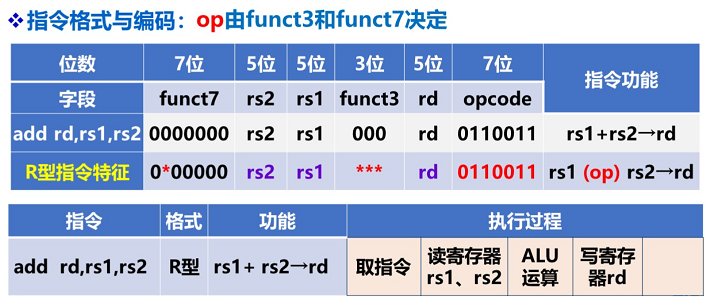

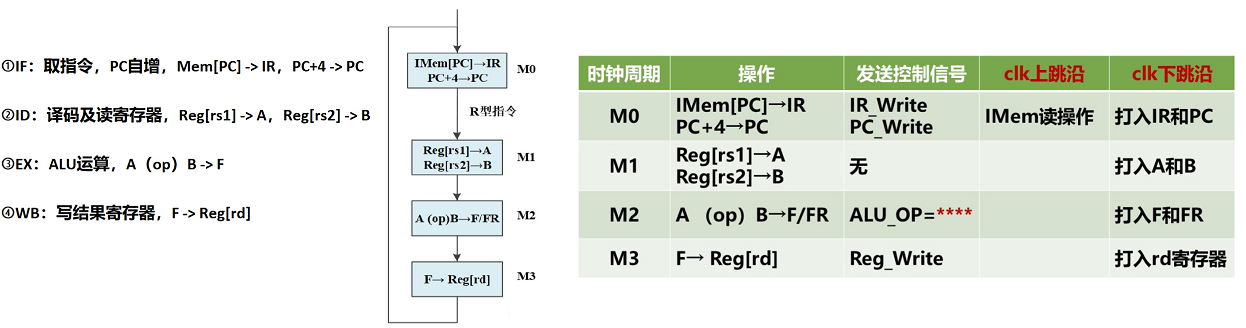

1. 运算型指令——R型指令

- 指令存储器 IM:取指令,由PC提供地址,在clk的上跳沿完成读操作,在clk下跳沿将机器指令写入IR

- PC的控制:自增通过专有加法器完成,不受时钟控制,更新在clk下跳沿完成(PC_Write=1)

- IR的控制:更新在clk的下跳沿完成(IR_Write=1)

- 指令初级译码器:读出32位指令,各字段分别送数据通路部件(rs1、rs2、rd送寄存器堆地址,opcode、func3、func7送二级译码器ID2译码)

- 寄存器堆:2个读端地址(rs1、rs2),一个写端地址(rd),2个读数据输出端口(直接打入暂存器A、B保存),一个写数据输出端口(从暂存器F的输出端引入),写控制信号在clk下跳沿有效(Reg_Write)

- ALU:10种运算功能,由4位ALU_OP指定,输入A、B由暂存器A、B的输出端提供,运算结果输出暂存器F

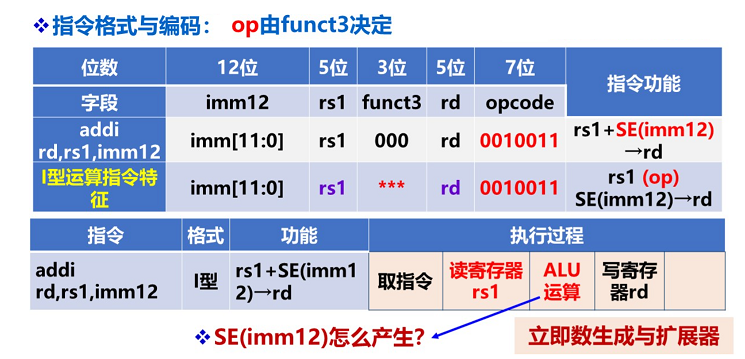

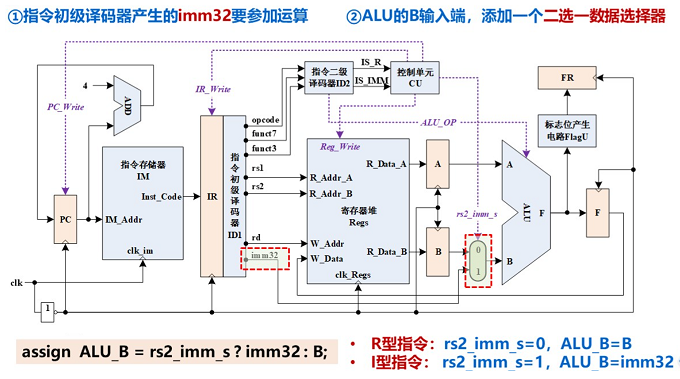

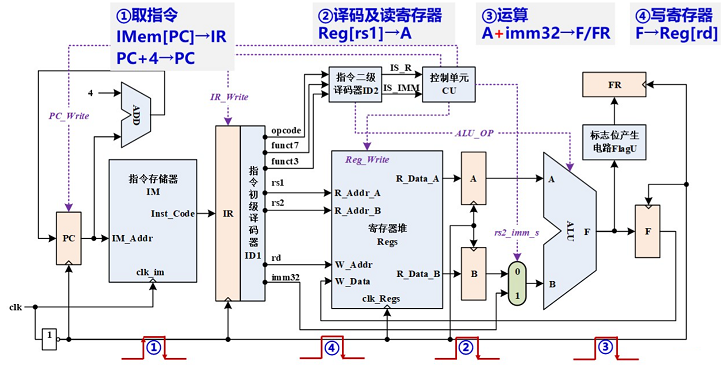

2. 运算型指令——I型指令

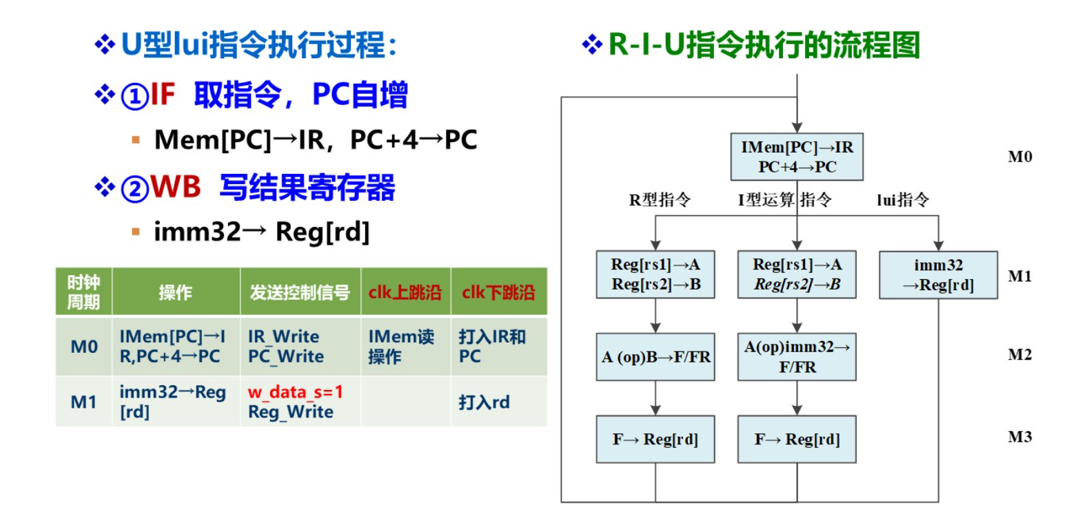

3. 传送类指令——U型指令

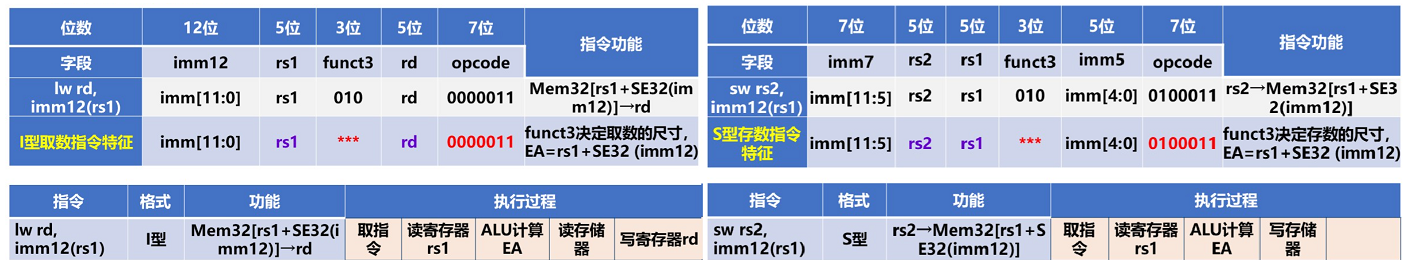

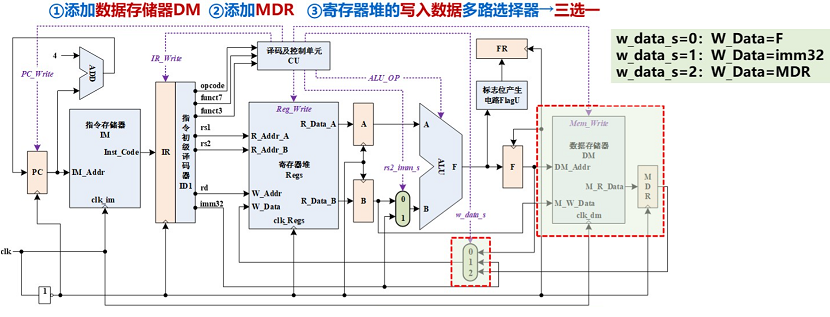

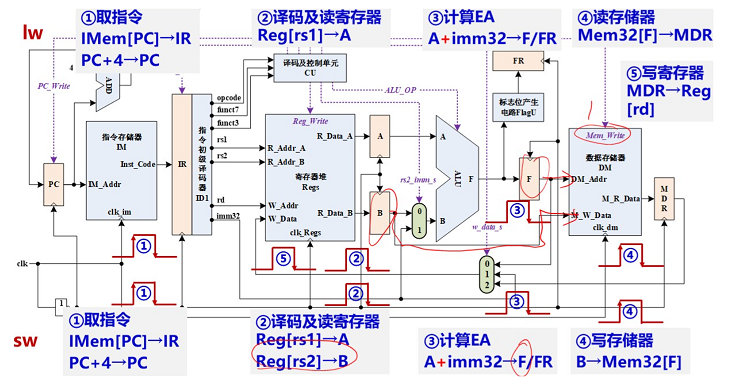

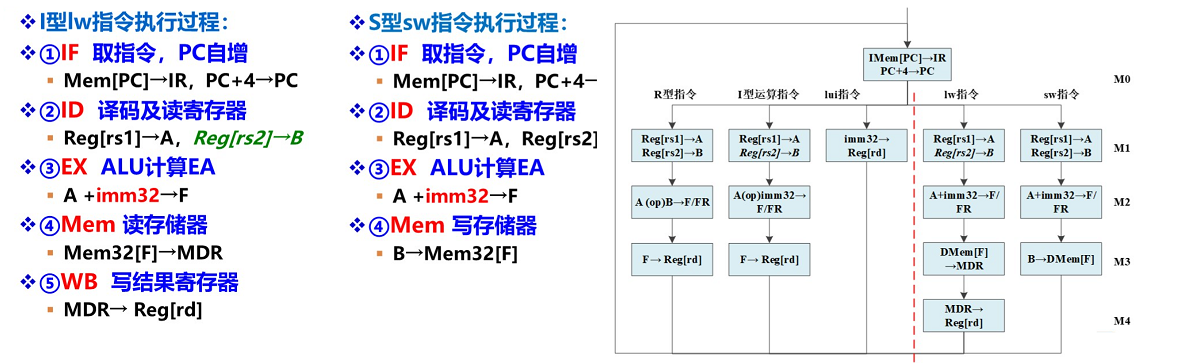

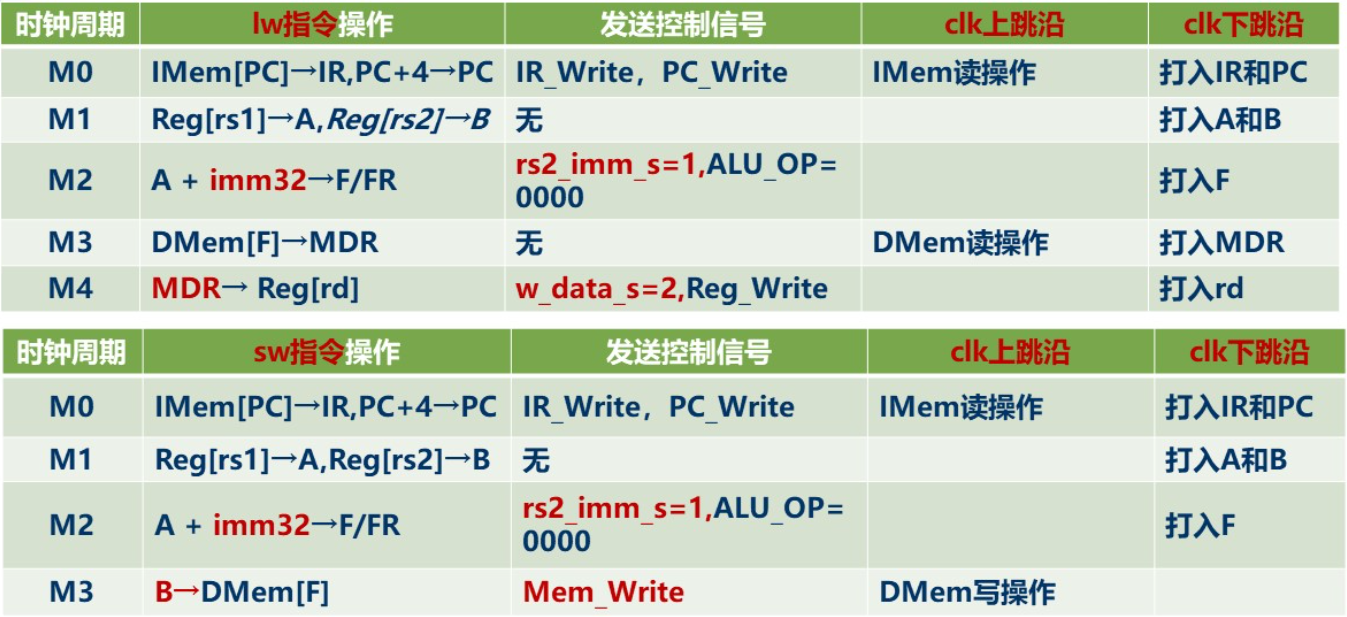

四、访存指令的数据通路设计

①访问DM时,地址DM_Addr从哪里来?

- EA = Reg[rs1] + imm32,如何实现地址加法?

- Reg[rs1] -> A,rs2_imm_s = 1,则 A + imm32 -> F

- 故访问DM时,地址DM_Addr可以直接由暂存器提供

②执行DM读操作时,读出的数据M_R_Data到哪里去?

- lw指令执行DM读操作,读出的数据写入rd寄存器

- 存储器读出数据端设置一个暂存器MDR,保存存储器读出的数据

- 在下一个周期再将MDR的内容写回到rd寄存器

- 故执行DM读操作时,读出的数据M_R_Data保存到MDR寄存器

- 写回周期写入rd的写数据W_Data来源,多了MDR,故W_Data的二选一变成三选一

③执行DM写操作时,写入的数据M_W_Data由谁提供?

- sw指令执行数据存储器的写操作,写入的数据是rs2寄存器的内容

- rs2寄存器的内容保存在B暂存器中

- 故执行DM写操作时,写入的数据M_W_Data由暂存器B提供

数据存储器

- 地址:暂存器F提供,Why? EA = rs1 + imm32

- 读出数据:接暂存器MDR,clk上跳沿读出,下跳沿打入MDR

- 写入数据:从暂存器B引入,Why?sw指令:rs2 -> Mem,rs2内容在B中

- 写使能信号:Mem_Write = 1,clk上跳沿写入

W_Data的三选一数据选择器

- R型指令:w_data_s = 0,W_Data = F

- I型运算指令:w_data_s = 0,W_Data = F

- U型指令lui:w_data_s = 1,W_Data = imm32

- I型访存指令lw:w_data_s = 2,W_Data = MDR

MDR

- 输入:DMem读出数据

- clk下跳沿读出数据打入MDR

- 输出:数据写入W_Data

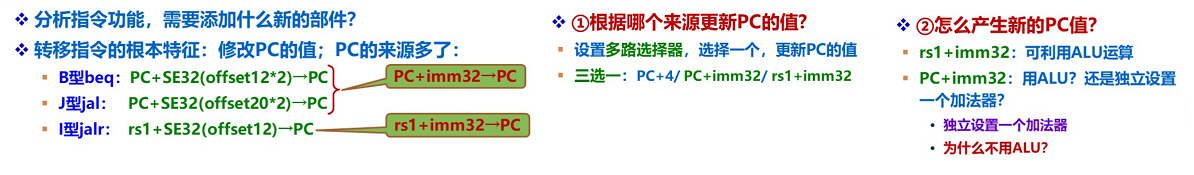

五、转移类指令的数据通路设计

转移地址专用加法器

- 输入:PC0 + imm32

- 输出:运算器结果写入PC受多路选择器控制

PC0暂存器

- 输入:PC取指令周期,在clk下跳沿,PC0_Write = 1,将PC打入PC0

- 输出:送入转移地址专用加法器

PC写入多路选择器:三选一

- 所有指令的取值周期:PC_s = 0,PC + 4 -> PC

- beq分支指令:ZF = 1 或 PC_s = 1,PC0 + imm32 -> PC

- jal转移并链接指令:PC_s = 1,PC0 + imm32 -> PC

- jalr转移并链接指令:PC_s = 2,F(=rs1+imm32) -> PC

W_Data的四选一数据选择器

- R型指令:w_data_s = 0,W_Data = F

- I型运算指令:w_data_s = 0,W_Data = F

- U型指令lui:w_data_s = 1,W_Data = imm32

- I型访存指令lw:w_data_s = 2,W_Data = MDR

- J型转移指令jal:w_data_s = 3,W_Data = PC

- I型转移指令jalr:w_data_s = 3,W_Data = PC

- B型beq指令呢?w_data_s = ? S型sw指令呢?无所谓,因为不写rd,Reg_Write = 0

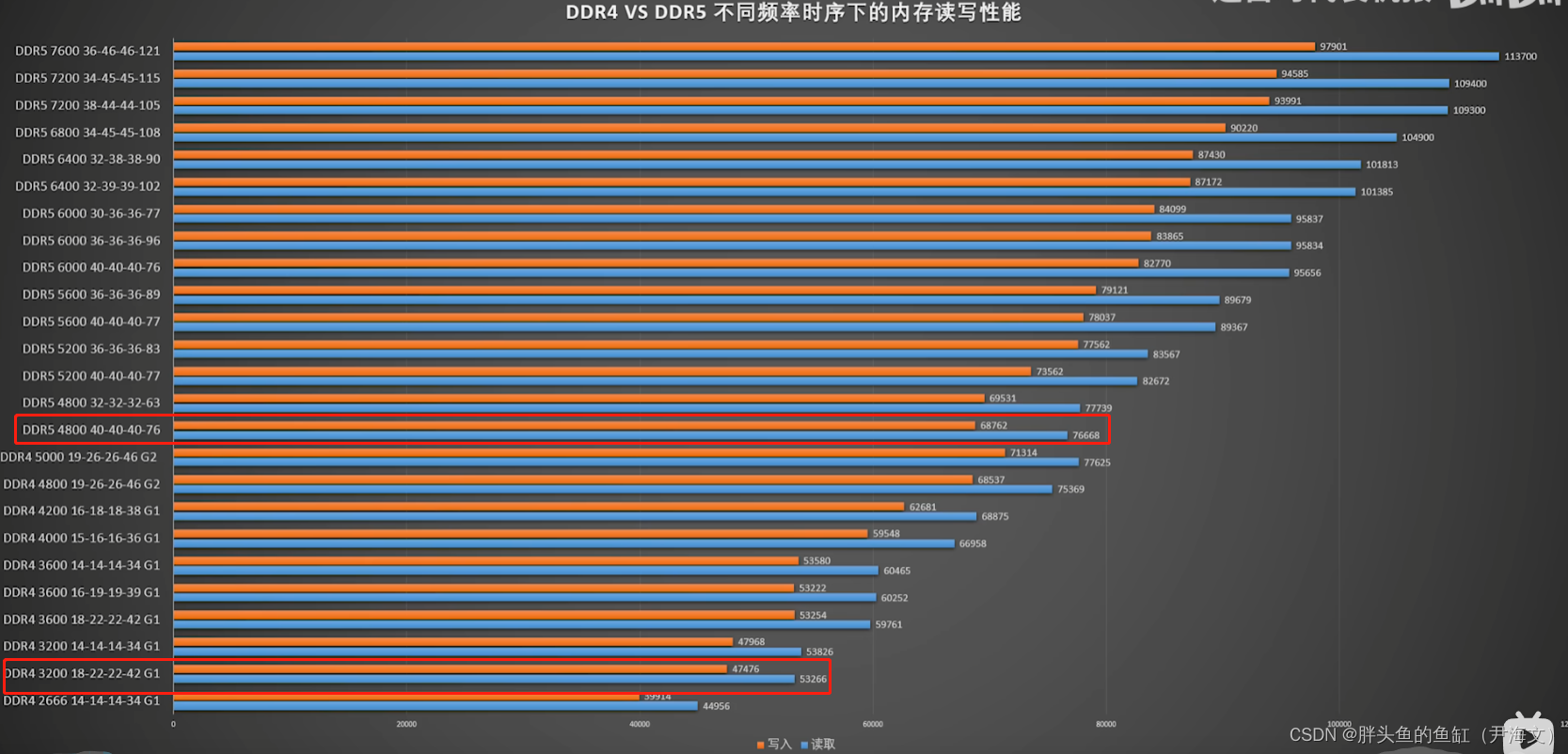

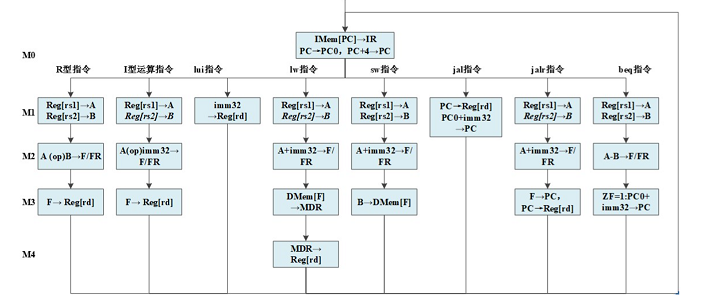

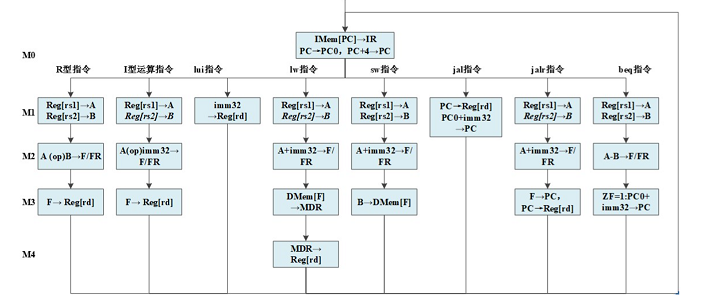

RV321目标指令集的25条核心执行执行的流程图

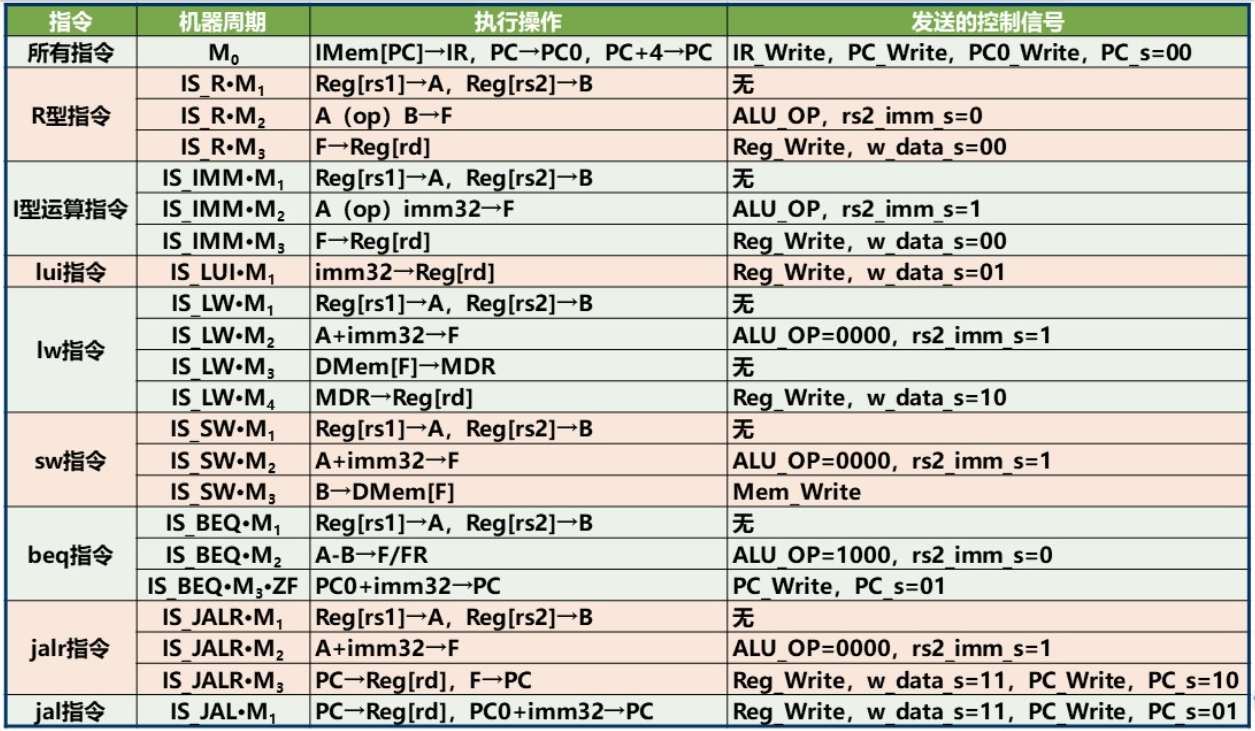

RV321目标指令集的25条核心执行执行的控制信号表

部件的控制信号表(高电平有效)

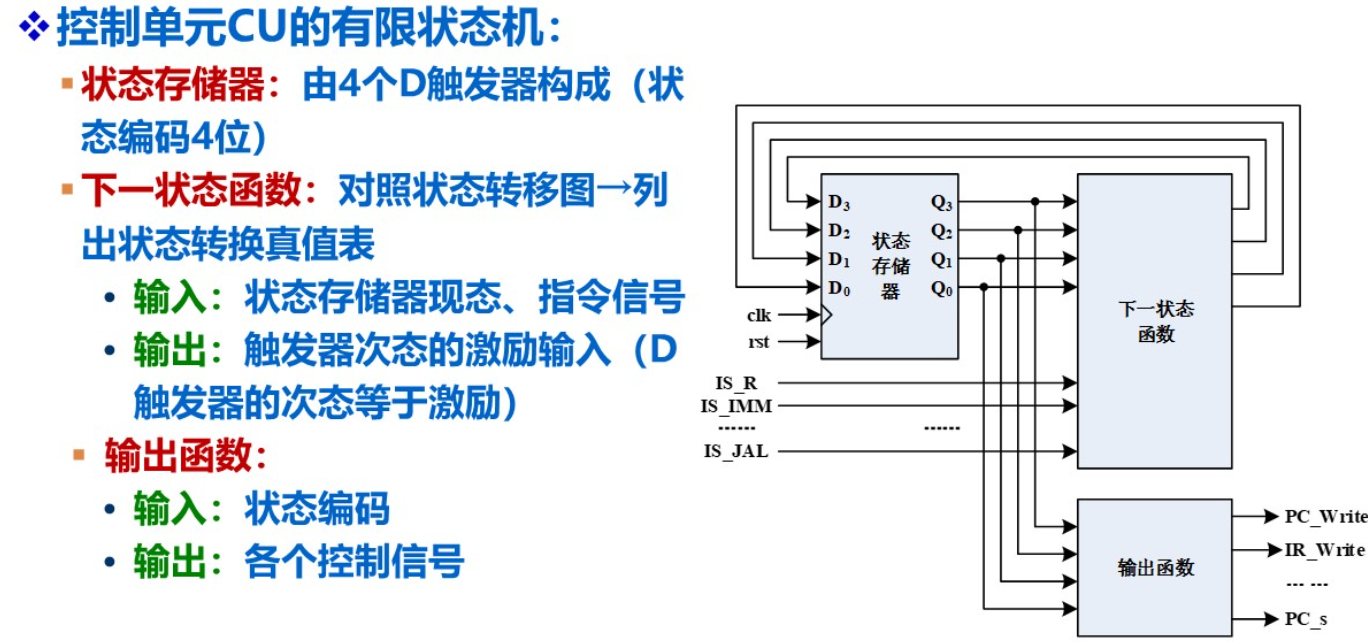

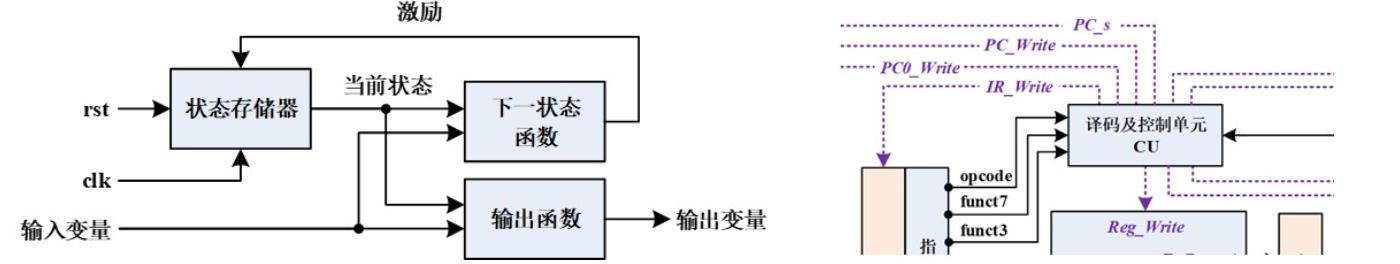

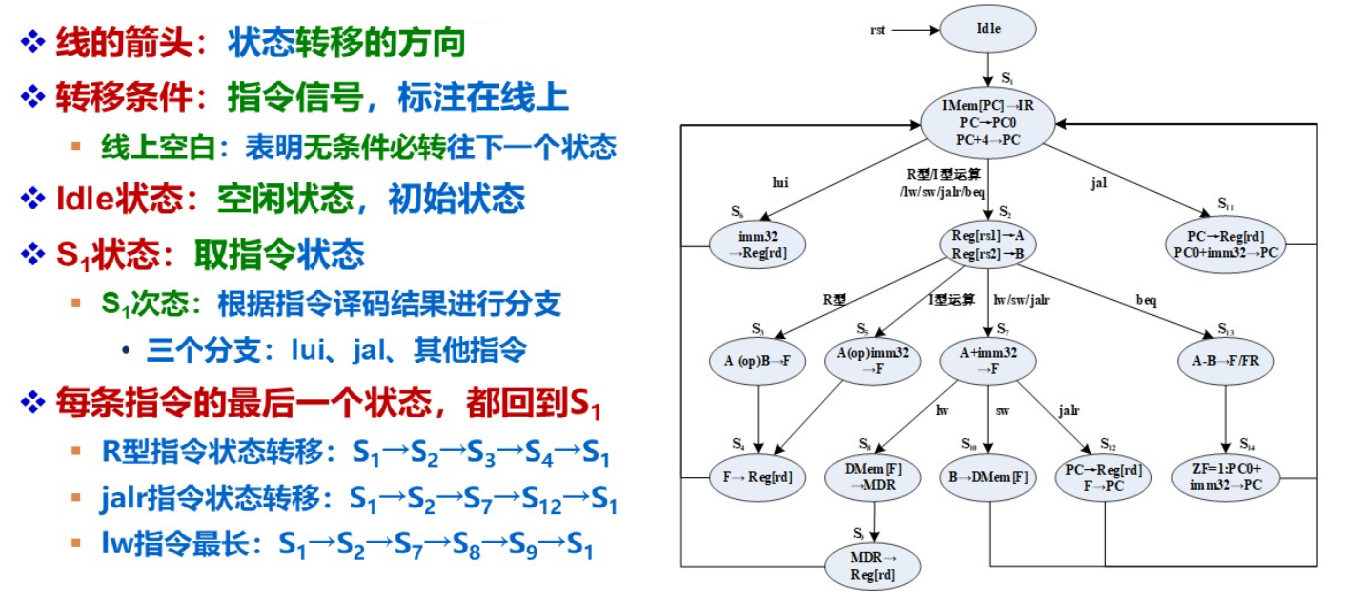

六、RISC-V模型机控制单元CU的有限状态机设计

如何产生部件控制信号?由操作控制信号形成部件(控制单元CU)产生

CU的实现方法

- 硬布线控制器:组合逻辑电路

- 微程序控制器:存储逻辑电路

- 有限状态机 FSM:适用于FPGA器件,本质上是组合逻辑+时序逻辑

有限状态机原理:Finite State Machine,通过状态迁移来完成特定的顺序逻辑控制

有限状态机构成:1个状态存储器 + 2个函数

- 状态存储器:由触发器构成,保存FSM的当前状态

- 下一状态函数:根据输入和当前状态来产生状态触发器的激励信号,实现向次态转移

- 输出函数:由当前状态、当前输入产生状态机的输出信号

- 复位信号rst:初始化有限状态机为初始状态

- 时钟信号clk:触发状态转移

1. 有限状态机原理

有限状态机设计步骤

- 确定电路的输入、输出与状态,画出状态转移图

- 状态化简:得到最简的状态转移图

- 状态编码:采用8421码或格雷码或独热码都可

- 求出下一状态和输出函数,用电路实现,或者采用HDL描述,用FPGA等器件实现

用有限状态机实现控制单元CU:

- 输入变量:指令译码输出的指令信号(IS_R、IS_IMM等)

- 输出变量:指令什么时间、要发送什么控制信号,由当前状态决定

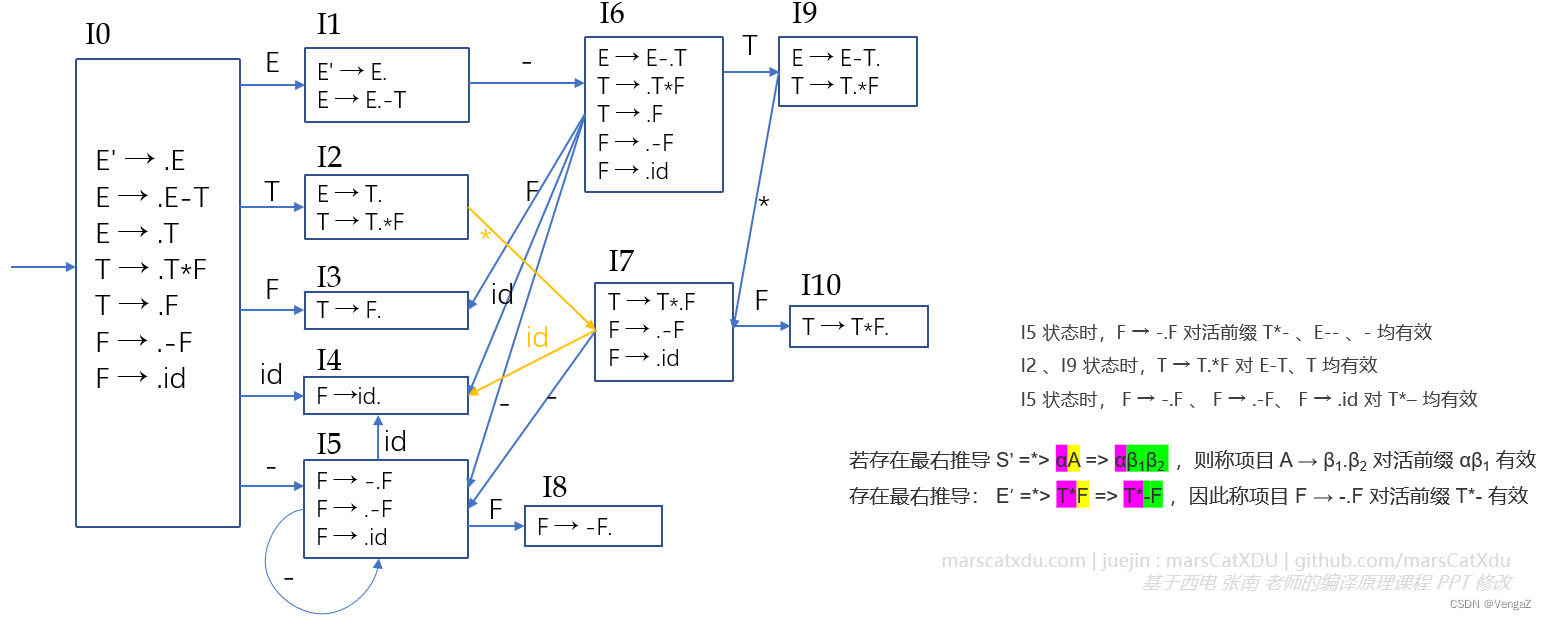

2. 指令执行的状态转移图

指令执行流程图就是一个状态转移图,每个方框就是一个状态

- 有重复状态,例如“Reg[rs1] -> A,Reg[rs2] -> B”

- 合并重复状态,得到最简状态图

3. 状态编码及输出的控制信号

4. 控制单元CU的有限状态机