RISCV Reader

RISCV的诞生

出众之处

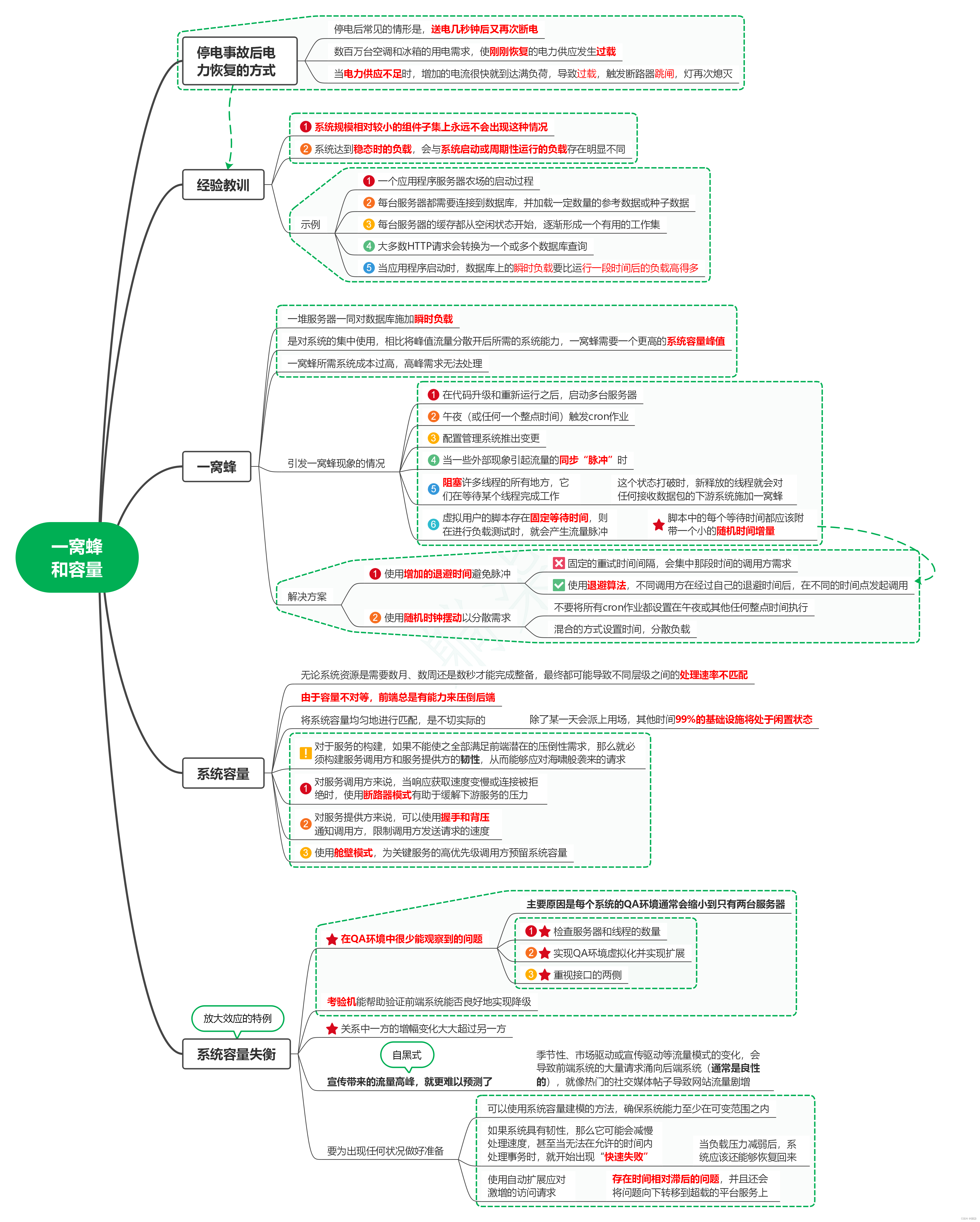

RISCV架构被设计的目的就是成为一个通用的指令集架构 ISA。不仅支持从微控制器到高性能计算机的各种处理器,兼容各种编程语言,还适应FPGA ASIC等所有实现技术,稳定……

计算机体系结构为了在指令集更新的时候保持其向后兼容性,传统做法是增量ISA,新处理器要实现新的ISA扩展和所有旧扩展。x86就是如此,但是其弊端在于哪怕过去的实现是错误的,为了兼容每次也必须实现。

而RISCV是模块化的,核心是RV32I基础ISA,运行一个完整的软件栈;其他扩展模块硬件可以根据自己的需要选择包含或者不包含。这使得RISCV有轻量,低能耗的特点。比如要包含乘法RV32M,单精度浮点RV32F,双精度浮点RV32D这三个扩展,加入基础ISA后的指令集名称为:RV32IMFD。

ISA设计中的7个衡量标准

成本

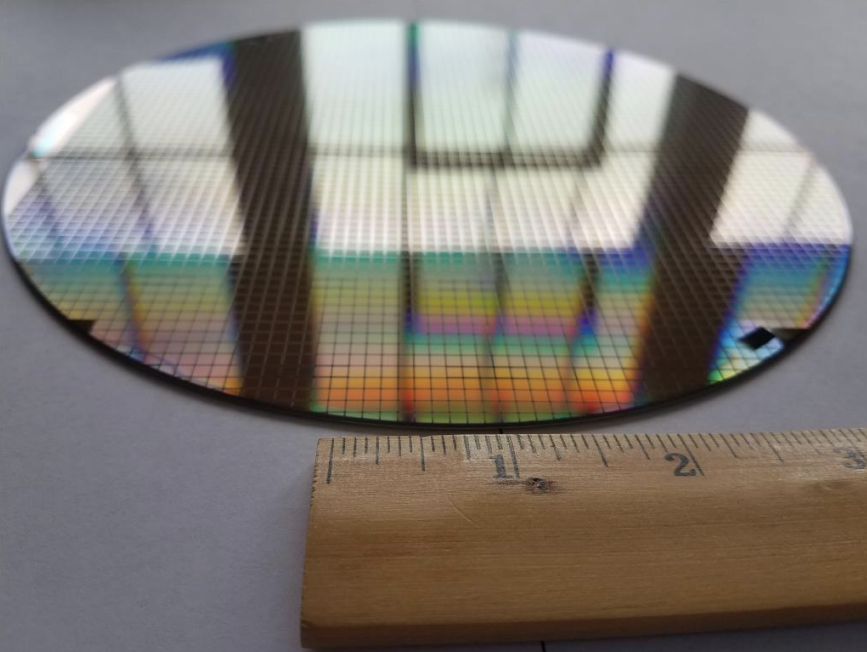

芯片/晶粒是从晶圆上切割出来的。

晶圆上可能有瑕疵,这样切割下来的晶粒如果包含瑕疵也用不了。因此晶粒体积越小包含瑕疵的比重也越少,利用率越高。ISA越简洁,晶粒越小,成本也因此减小。

简洁性

可以通过对指令的调整实现。简单指令的组合会比复杂指令性能更好。

性能

程序包含的指令数 * 指令平均需要的周期数 * 每个时钟周期用时=程序用时。

RISCV在这三个方面都有一定的优势。

架构和具体实现的分离

具体表现在于:架构师可能为了优化某一部分的性能和成本,在ISA中包含某些指令,但是这种做法可能给以后的实现造成负担;而程序员了解架构后能写出正确的程序,却不一定能保证性能。比如提升了单发射流水线的指令可能造成多指令并行流水线的负载降低,吞吐量整体降低。

提升空间

摩尔定律差不多终结了,不能再指望着晶体管翻番,有更多的地址存指令了。应当专注于特定领域来进行提升比如机器学习,图形,AR等特殊指令。因此ISA是否保留了操作码空间以供未来提升也是一个重要的衡量要素。

比如Thumb2,引入了16位的Thumb指令,和16+32位指令的Thumb2,并用一位模式位来切换。

程序大小

程序小了需要存储空间也少了,芯片面积也可以缩减;而且指令缓存未命中问题也会减少(因为一共就没用几条指令),功耗也会降低。这个并不是说单纯指令短了程序就小,x86的变长指令代码反而比RV32C和Thumb2大。

易于编程/编译/链接

一方面,我们知道存储金字塔模型中寄存器是最顶端速度最快的,因此要合理分配好寄存器。RISCV有32个。

另一方面,每条指令的执行速度应当保持稳定。在缓存命中的前提下RISCV的指令基本稳定一个时钟周期执行完成,但是比如x86的算数操作数有可能在寄存器里,有可能在存储器里……这种位置不确定的操作数,复杂的指令使得运行速度不一定稳定,性能测试难以保证。

本书介绍

在后面的章节中会首先介绍RV32I,各种RV32G(General)包括RV32M,RV32F和RV32D,RV32A 原子操作,16位的压缩扩展RV32C,向量扩展RV32V,RV64G,以及RISCV基金会在考虑的新扩展。