本文将详细描述将vim变成写Verilog代码的IDE客制化的实现过程,同时最后提供自己的环境。实现的过程中有使用自己写的,也有参考借鉴其他同学进行一定的修改,也有直接使用插件实现的相关功能。对应的功能实现部分均会给出相应的参考与插件地址等有关该功能的实现信息。有兴趣的同学可以据此,在此基础上实现适合自己的IDE工具。

都是慢慢抄,慢慢学,慢慢修改,千万记得自己总结,抄到的才是自己的~

GVIM写Verilog环境搭建——将文本编辑器客制化定义为你自己的IDE

- 概述

- 特性

- 演示

- 实现方式与演示

- 基本的映射,相关功能

- 基本语法检查功能

- 其他tips

概述

本文将分享使用gvim写verilog一系列的方便编码工具,将vim打造成一个IDE(IDE 是 Integrated Development Environment 的缩写,中文称为集成开发环境,用来表示辅助程序员开发的应用软件,是它们的一个总称。)目的是使得编码过程中任何让你觉得繁琐的,重复性劳动,全部交给工具做,帮助更快更好的实现你的目标。这里笔者个人经验感觉哈,若是有些你觉得感觉繁琐的,愚蠢的操作,一定时没有使用正确的方式去做这件事~可以思考优化下做事的方式

关于VIM的版本建议linux下使用8.2以上的版本,windows使用最新的版本。更高的版本VIM进行了很多优化,其中重要的两个:1,支持插件管理(可以使得使用管理插件的方式更为便捷) 2,加入了异步执行命令的机制。关于版本的问题更详细的可以查看vim.org上有关版本更新的日志。这里不多进行赘述。

特性

组为个性化的定制,笔者定义实现的所有功能如下所示:

- 基本的映射,相关功能

- 快速生成端口列表(input、output)

- 自动生成实例化模板,自动对齐

- 定义版权,作者,模块名称

- 状态栏配置,buffer栏的快速切换,删除

- 括号自动补全,括号颜色特征不同

- 目录结构显示

- 中文doc文件代替

- 查找单词在当前目录下其他文件下的使用位置

- 自动仿真脚本模板

- 自动实现顶层集成

- 自动生成端口列表

- 自动生成仿真代码脚本优化

- 基本的语法检查功能

演示

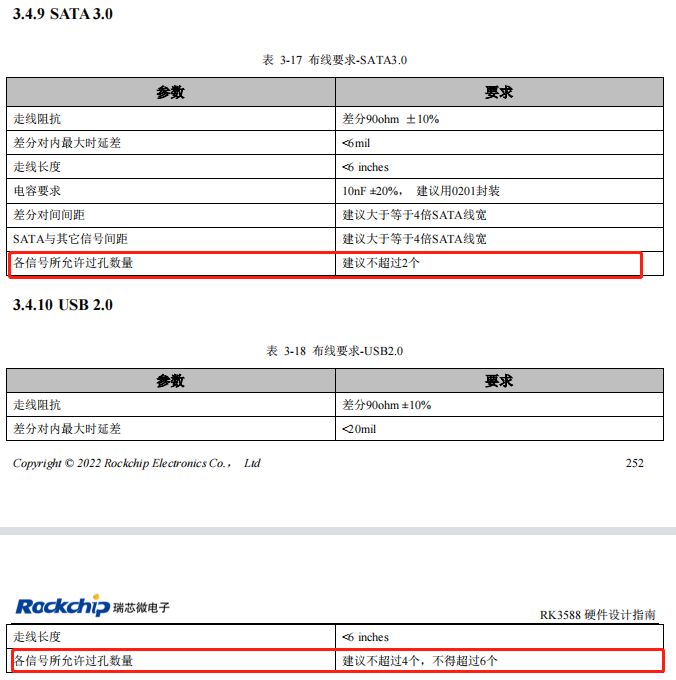

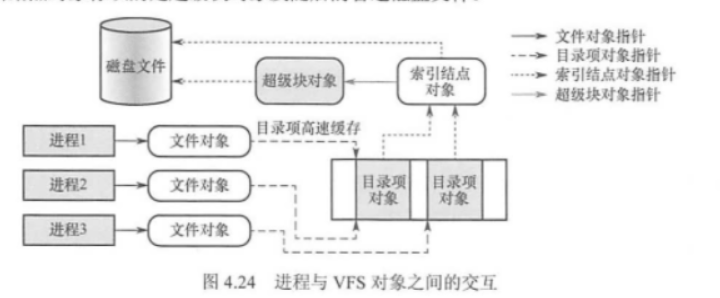

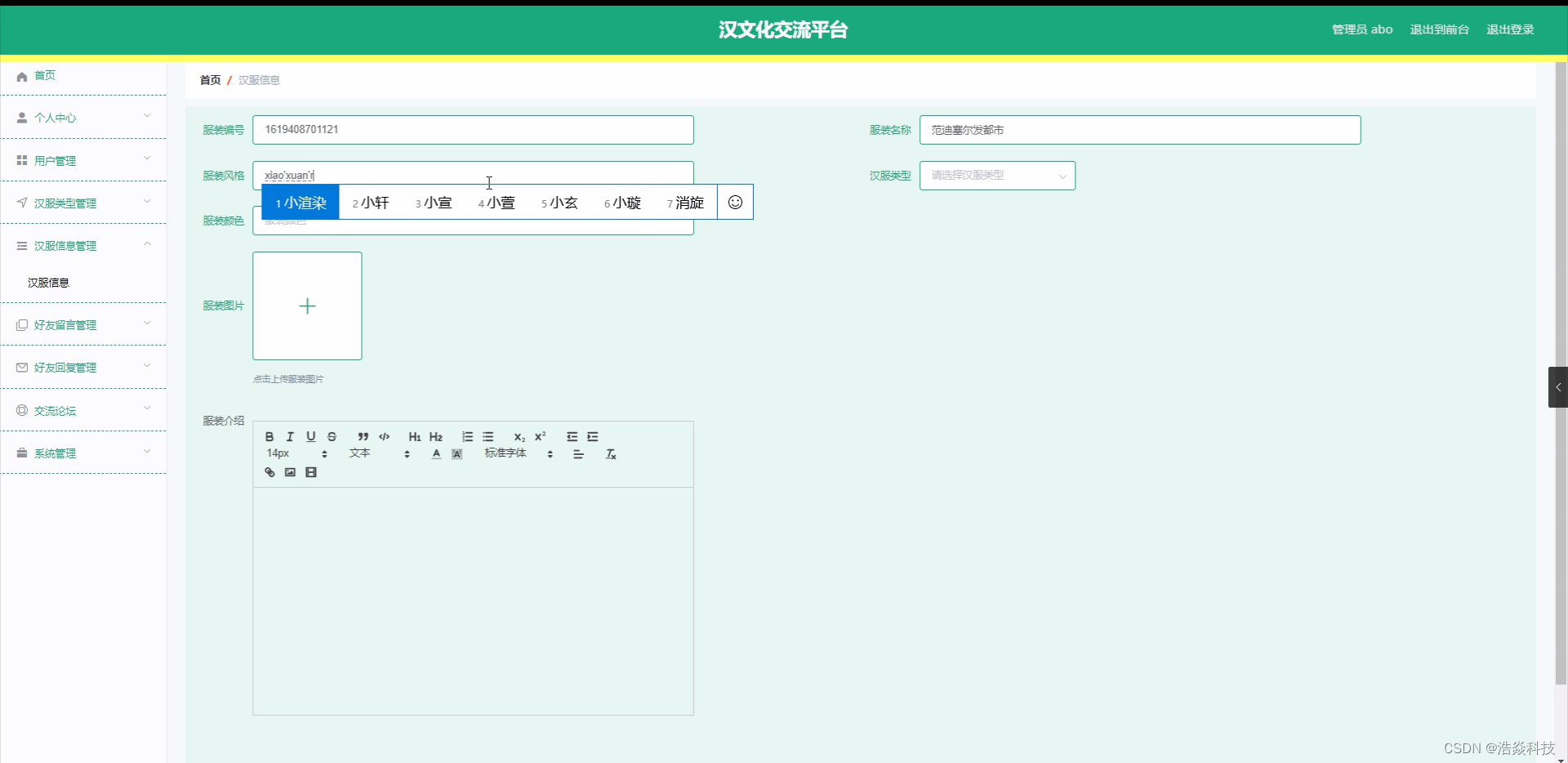

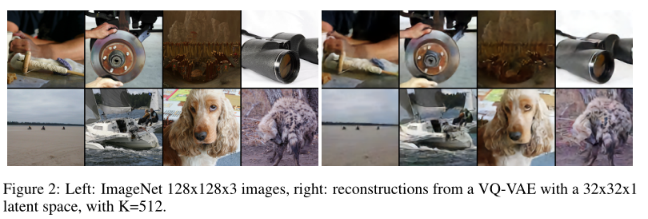

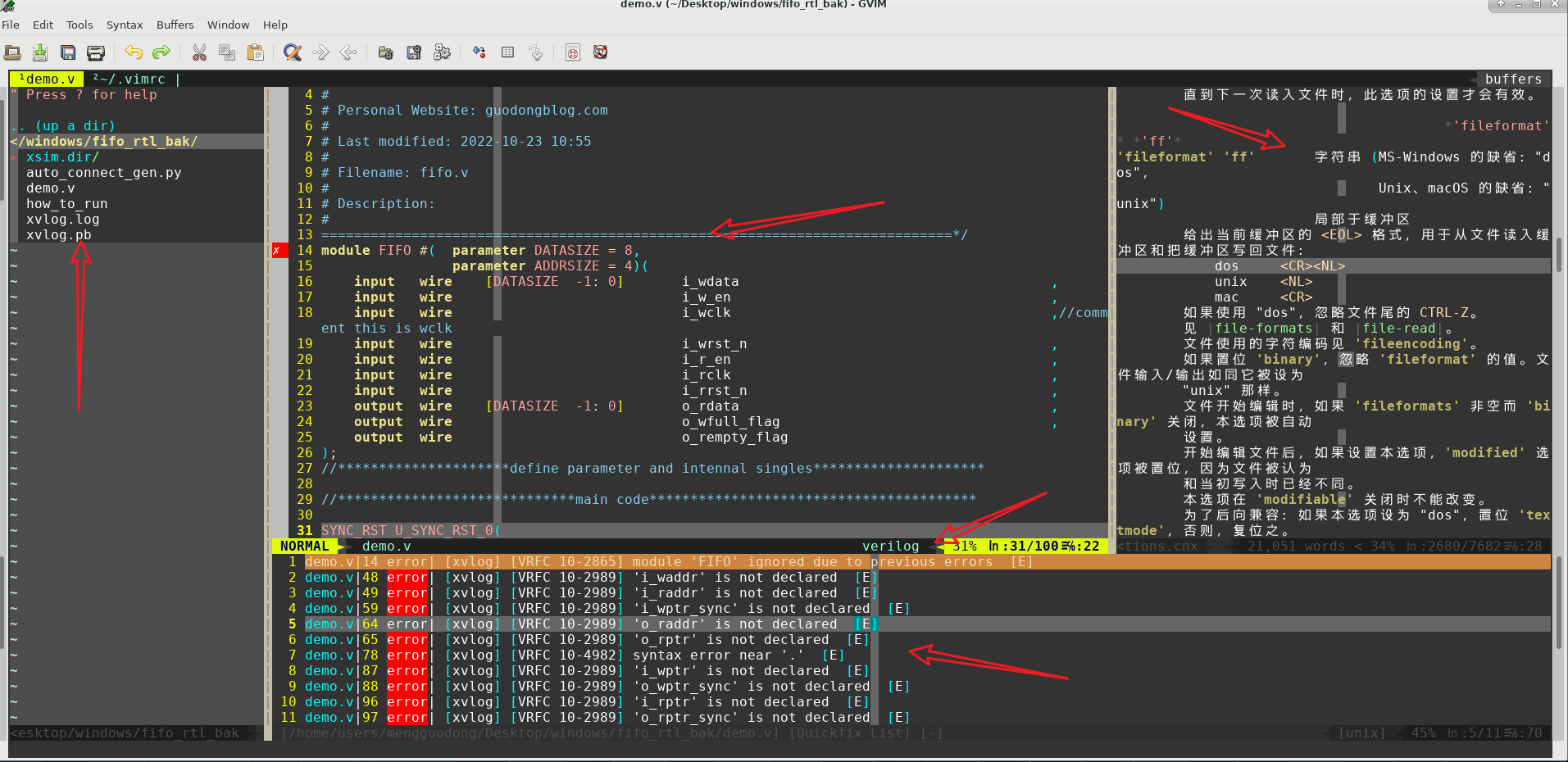

下文将着重介绍每一个功能的使用方式,演示与优化等~下图是展示vim的使用展示图,包括文本编辑区的代码高亮,括号高亮等,buffer的展示,代码error,warning的展示,状态栏的信息展示,中文doc文件展示,文件目录窗口等。

实现方式与演示

基本的映射,相关功能

基本语法检查功能

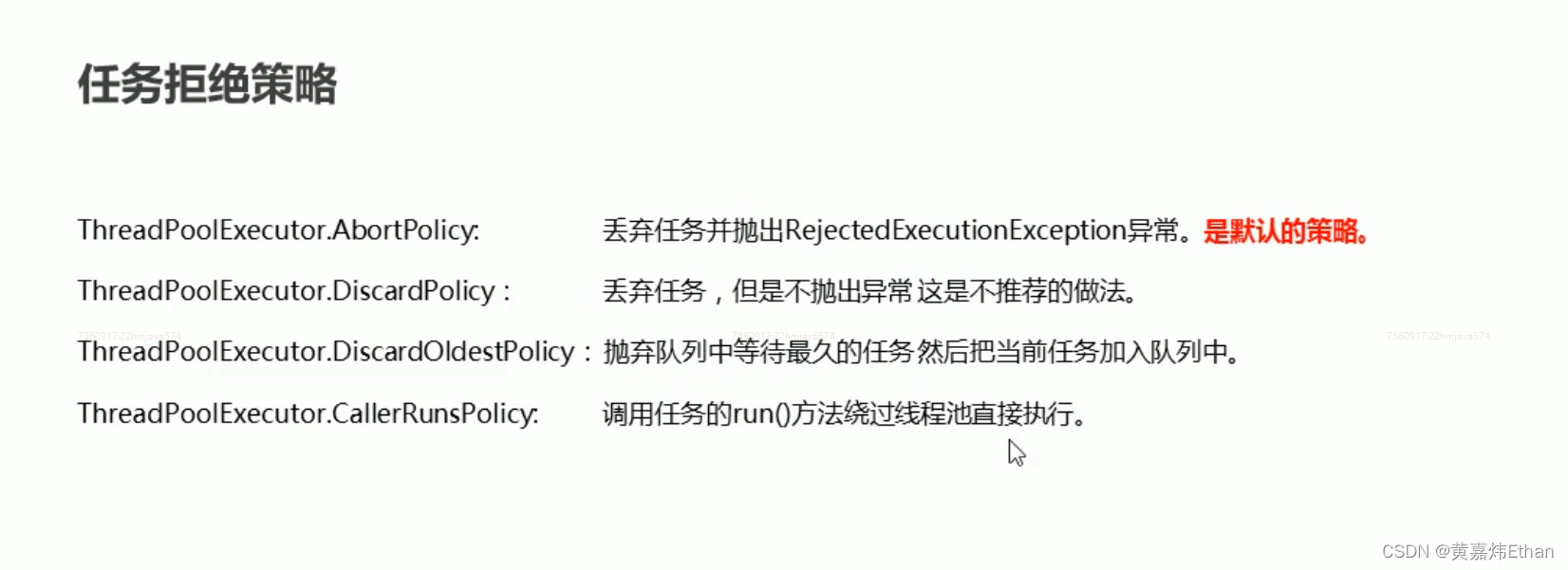

该功能使用的插件是Ale(Asynchronous Lint Engine 异步lint引擎),该插件是非常优秀的异步代码检查工具,支持众多编码语言。这里的异步是指他的进行过程是在后台自行进行的,不会影响到你当前对于vim的操作,vim在8.1版本后推出了异步执行命令的机制,以此为基础的代码包括大名鼎鼎的Youcompleteme, Ale。Ale项目地址如下:https://github.com/dense-analysis/ale,点击这里访问。个人理解就是插件会调用可以使用的linter(语法检查工具),然后将其输出的检查信息整理展示出来,达到一个语法检查的目的。其中linter需要自行安装。跟详细的使用以及关于ale的介绍见这里 ALE的基本介绍、使用与配置

其他tips

更聪明的自动补全功能

任意自加数的生成

遇见插件在linux下报错^M的问题

注意将Tab替换为空格键

查看vim版本,支持的接口等