目录

第一部分、相关知识

1、UART和RS232的区别

2、UART与USART的区别

3、全双工?

4、RS232通信协议

5、波特率

6、如何将外部异步信号变为内部同步信号?

7、什么时间点让FPGA去采集rx线上的数据?

第二部分、串口通信时序图

1、发送线RX流程

1.1、模块图

1.2、端口介绍

1.3、时序波形图

1.4、RX接收代码

2、接收线TX流程

2.1、模块图

2.2、时序波形图

2.3、 TX发送代码

3、Top层代码

第三部分、仿真代码的编写

1、testbench代码

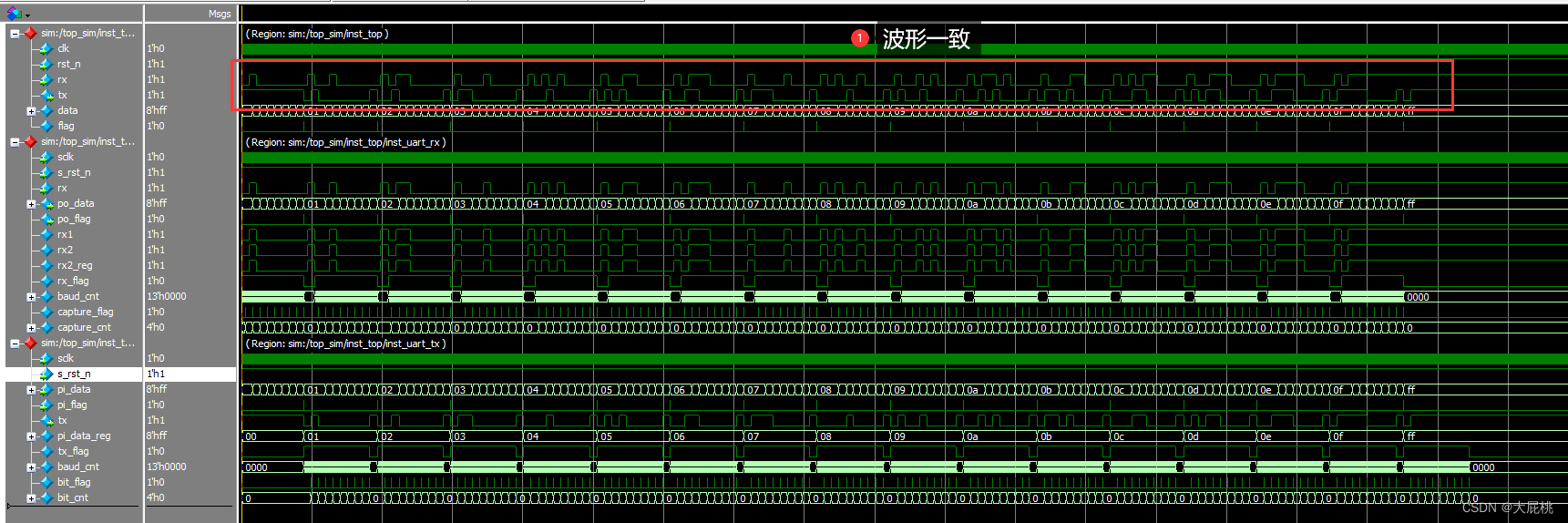

2、仿真结果

3、上板测试

第四部分、总结

第一部分、相关知识

1、UART和RS232的区别

- UART就是一堆电路,是异步串行通信的一种电路实现;

- RS232属于异步串行通信方式,跟UART相比,区别仅在于UART使用的是TTL电平,而RS232使用的是另一种电平标准。

2、UART与USART的区别

UART:UART 的全称叫做通用异步收发传输器。

- 将数据在串行通信和并行通信间的传输转换。通俗的讲就是把多比特的数据转化为单比特的数据,或者把单比特的数据转化为多比特的数据。工作原理是将数据的每个 bit 一位接一位地传输。

- UART 是一种通用串行数据总线,用于异步通信。该总线双向通信,可以实现全双工传输和接收

USART:通用同步和异步收发器

- 当进行异步通信时,这两者是没有区别的。

- 区别在于USART比UART多了同步通信功能,因此USART可以提供一个主动的时钟线。使用外部时钟使 USART 的数据速率远高于标准 UART 的数据速率。

3、全双工?

全双工:表示发送和接收不会相互影响。

4、RS232通信协议

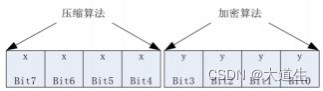

rs232 是 uart 的一种,有两根线,分别是 rx 和 tx,这两根线都是 1 比特位宽的。其中 rx 是接收线, tx 是发送线。

- rx,位宽为 1 比特, pc 机通过串口往 FPGA 发 8 比特数据时, FPGA 通过串口线 rx 一位一位地接收,从最低位到最高位依次接收,最后在 FPGA 里面位拼接成8 比特数据。

- tx,位宽为 1 比特, FPGA 通过串口往 pc 机发 8 比特数据时, FPGA 把 8 比特数据通过 tx 线一位一位的传给 pc 机,从最低位到最高位依次发送,最后上位机通过串口助手把这一位一位的数据位拼接成 8 比特数据。

在不发送或者不接收数据的情况下, rx 和 tx 处于空闲状态,此时 rx 和 tx 线都保持高电平

如果有数据传递,首先会有一个起始位(0),然后是 8 比特的数据位,接着有 1 比特的停止位

如果停止位以后不再发数据,将进入空闲状态,否则又将数据线拉低(进入起始位状态)。

注意:起始位和停止位各算一位,因此一共是10位数据,而停止位不需要去做判断。

5、波特率

波特率:在串口通信时的速率,单位时间内载波变化的次数,这里选用的是9600Bd,即发送一比特数据需要的时间为 1/9600 秒。

用串口发送或者接收数据(起始位、数据位、停止位)时,每发送或者接收一位数据的时间都需要 1 个波特,即 1/9600 秒。

串口发送或者接收一比特数据的时间为一个波特(1/9600),因此如果用 50M的系统时钟来计数,就需要记数 cnt=(1/9600s)/20ns≈5208 个系统时钟,才再次发送或者接收下一个数据。

注意:cnt=(1/9600s)/20ns≈5208.33 ,累计误差0.33 * 10 = 3ns,这个误差太小了,是不会影响到传输的。而且计数器每次都是从0开始计数,因此,该误差也不会累加。

上位机通过串口发 8 比特数据时,会自动在发 8 位有效数据前发一个波特时间的起始位,也会自动在发完 8 位有效数据后发一个停止位。同理,串口助手接收 fpga 发送的数据前,必须检测到一波特的起始位才会接收数据,接收完数据后,再接收一个停止位,所以 FPGA 通过串口除了发数据以外,还要发起始位和停止位。

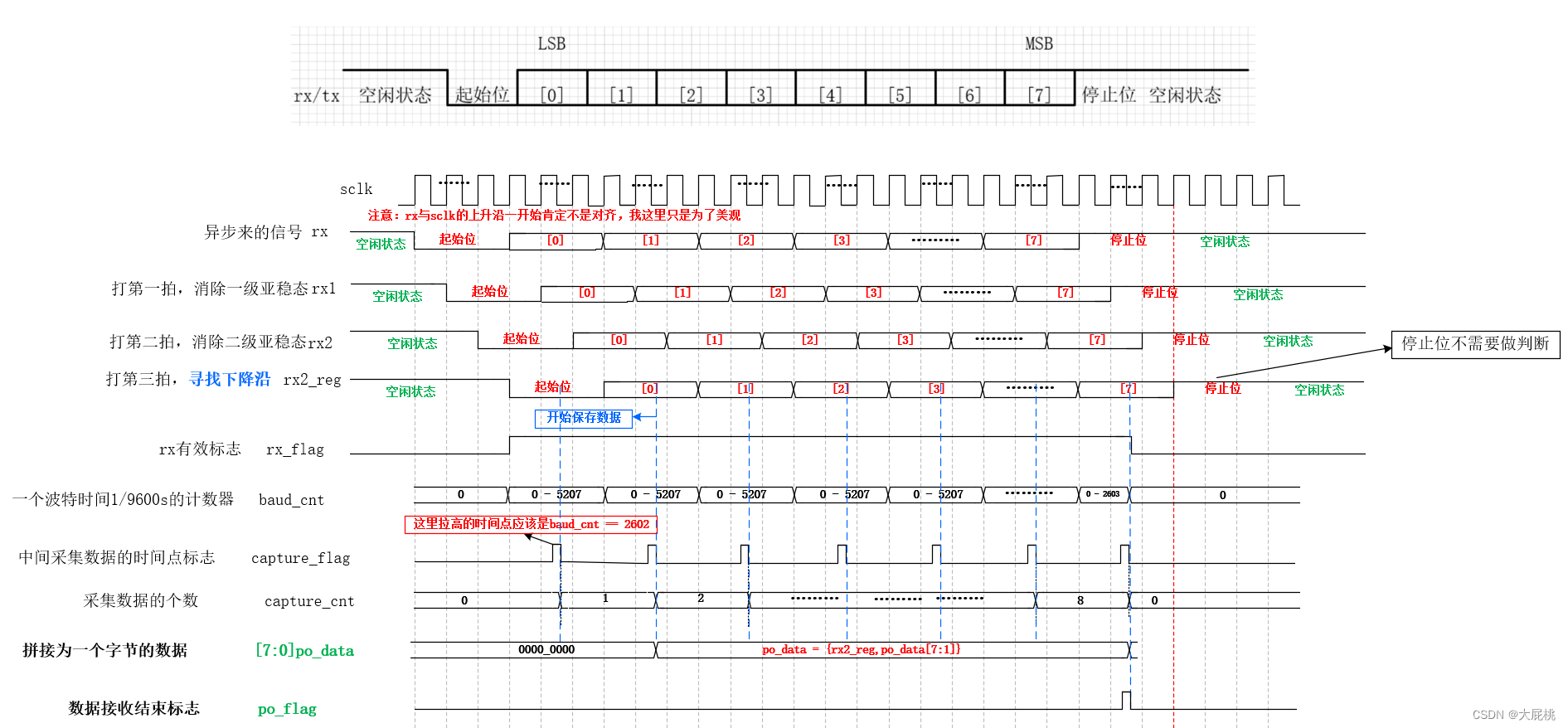

6、如何将外部异步信号变为内部同步信号?

通过前面的介绍可知,RS232为通用异步收发传输器,那么rx传到FPGA内部的数据与系统的时钟是不匹配的,没有任何逻辑关系,因此要借助寄存器将rx进行打两拍操作后,才能用来进行逻辑运算。

这么做的目的是尽量降低亚稳态,如果不做这样 的处理,就可能导致采集的数据不稳定,只有做了亚稳态处理后的数据才在后面使用。

7、什么时间点让FPGA去采集rx线上的数据?

外部的数据通过 rx 线传到 FPGA, FPGA 采数据时,在中间时刻采数可以保证采的数据最 稳定。

第二部分、串口通信时序图

1、发送线RX流程

1.1、模块图

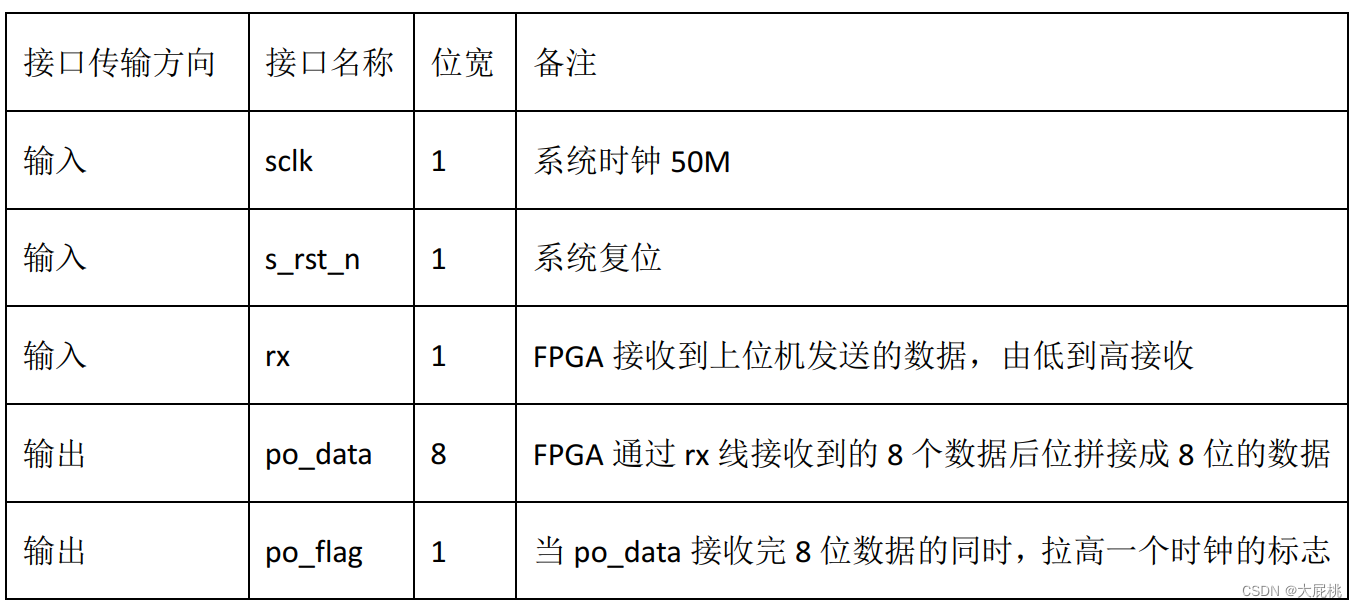

1.2、端口介绍

1.3、时序波形图

1.4、RX接收代码

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2023 All rights reserved

// -----------------------------------------------------------------------------

// Author : BigFartPeach

// CSDN : 大屁桃

// E-mail : 2624507313@qq.com

// File : uart_rx.v

// Create : 2023-06-20 12:45:49

// -----------------------------------------------------------------------------

module uart_rx(

input wire sclk,

input wire s_rst_n,

input wire rx,

output reg [7:0]po_data,

output reg po_flag

);

// //9600波特率参量

// parameter BAUD_END = 5207;//波特率9600,接收间隔最大计数MAXEND = 50M/9600 = 5208.33 - 1 = 5207

// parameter BAUD_HALF = 2602;//5208/2 - 1 = 2603,要在2603这里点看到波形

// parameter BAUD_BIT_WIDTH = 12;//5207需要13位来保存,[12:0]

//115200波特率参量

parameter BAUD_END = 433;//波特率115200,接收间隔最大计数MAXEND = 50M/115200 = 434.02 - 1 = 433

parameter BAUD_HALF = 216;//434/2 - 1 = 216

parameter BAUD_BIT_WIDTH = 8;//5207需要9位来保存,[8:0]

//变量

reg rx1;//用来降低亚稳态

reg rx2;//用来降低亚稳态

reg rx2_reg;//用来打拍rx2,判断下降沿

reg rx_flag;//rx信号有效标志位

reg [12:0]baud_cnt;//9600波特率的1个波特时间1/9600s的计数器

reg capture_flag;//中间采集数据的时间点

reg [3:0]capture_cnt;//采集数据的计数器

//利用移位寄存器打拍,打拍信号可以不加复位

always @(posedge sclk) begin

{rx2_reg,rx2,rx1} <= {rx2,rx1,rx};

end

//rx有效标志位,rx_flag

always @(posedge sclk or negedge s_rst_n) begin

if (!s_rst_n) begin

rx_flag <= 1'b0;

end

//rx_flag受baud_cnt影响,究竟是什么样的影响?

else if(capture_flag == 1'b1 && capture_cnt == 'd8)begin

rx_flag <= 1'b0;

end

else if (rx2 == 1'b0 && rx2_reg == 1'b1) begin

rx_flag <= 1'b1;

end

end

//一波特时间对应的计数器

always @(posedge sclk or negedge s_rst_n) begin

if (!s_rst_n) begin

baud_cnt <= 'd0;

end

else if(baud_cnt == BAUD_END)begin

baud_cnt <= 'd0;

end

//baud_cnt会计数到2603,若判断条件换成rx_flag == 1'b0,baud_cnt会计数到2604

else if(capture_flag == 1'b1 && capture_cnt == 'd8)begin

baud_cnt <= 'd0;

end

else if (rx_flag == 1'b1) begin

baud_cnt <= baud_cnt + 1'b1;

end

end

//中间采集数据的时间点标志

always @(posedge sclk or negedge s_rst_n) begin

if (!s_rst_n) begin

capture_flag <= 1'b0;

end

else if (baud_cnt == BAUD_HALF) begin

capture_flag <= 1'b1;

end

else begin

capture_flag <= 1'b0;

end

end

//采集数据的计数

always @(posedge sclk or negedge s_rst_n) begin

if (!s_rst_n) begin

capture_cnt <= 'd0;

end

else if (capture_cnt == 'd8 && capture_flag == 1'b1) begin

capture_cnt <= 'd0;

end

else if(capture_flag == 1'b1)begin

capture_cnt <= capture_cnt + 1'b1;

end

end

//输出po_data

always @(posedge sclk or negedge s_rst_n) begin

if (!s_rst_n) begin

po_data <= 'd0;

end

else if (capture_cnt >= 1'b1 && capture_flag == 1'b1) begin

po_data <= {rx2_reg,po_data[7:1]};

end

end

//输出结束标志

always @(posedge sclk or negedge s_rst_n) begin

if (!s_rst_n) begin

po_flag <= 1'b0;

end

else if (capture_cnt == 'd8 && capture_flag == 1'b1) begin

po_flag <= 1'b1;

end

else begin

po_flag <= 1'b0;

end

end

endmodule2、接收线TX流程

2.1、模块图

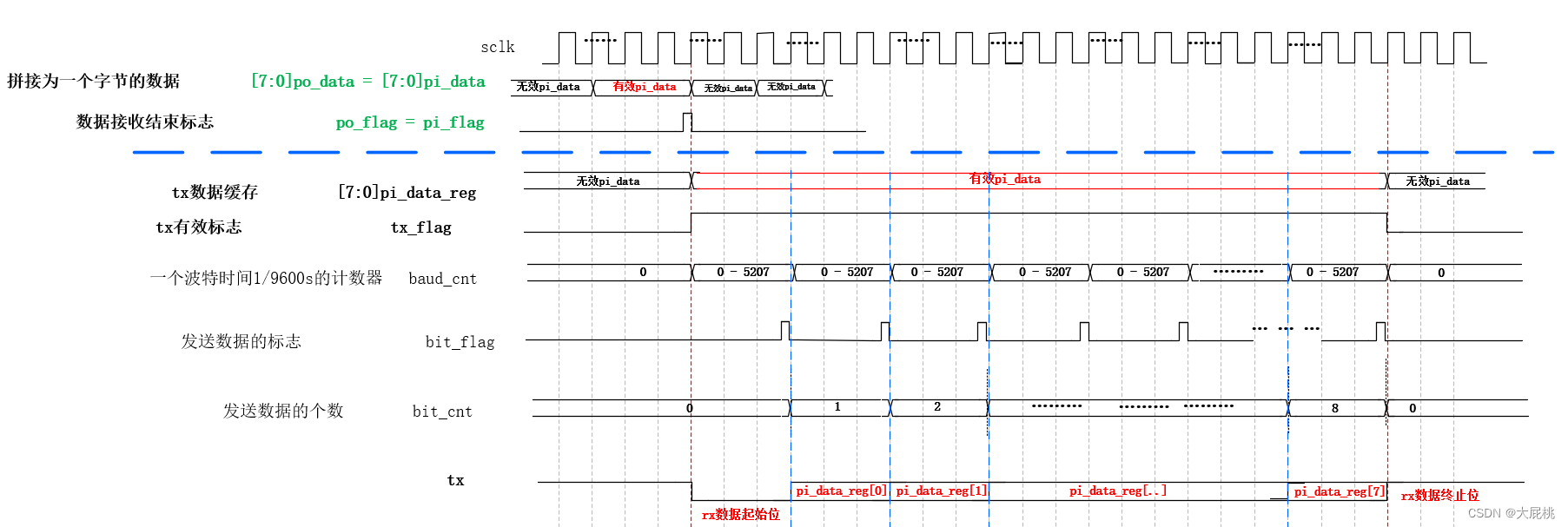

2.2、时序波形图

2.3、 TX发送代码

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2023 All rights reserved

// -----------------------------------------------------------------------------

// Author : BigFartPeach

// CSDN : 大屁桃

// E-mail : 2624507313@qq.com

// File : uart_tx.v

// Create : 2023-06-20 14:14:25

// -----------------------------------------------------------------------------

module uart_tx(

input wire sclk,

input wire s_rst_n,

input wire [7:0]pi_data,

input wire pi_flag,

output reg tx

);

// //9600波特率参量

// parameter BAUD_END = 5207;//波特率9600,接收间隔最大计数MAXEND = 50M/9600 = 5208.33 - 1 = 5207

//115200波特率参量

parameter BAUD_END = 433;//波特率115200,接收间隔最大计数MAXEND = 50M/115200 = 434.02 - 1 = 433

//变量

reg [7:0]pi_data_reg;//保存输入的数据

reg tx_flag; //发送数据的有效位,服务于计数器

reg [12:0]baud_cnt; //9600波特率的1个波特时间1/9600s的计数器

reg bit_flag; //计满flag

reg [3:0]bit_cnt; //发送数据计数。

//保存输入的数据,因为po_data在接收数据的时候一直在变

always @(posedge sclk or negedge s_rst_n) begin

if (!s_rst_n) begin

pi_data_reg <= 'd0;

end

else if(pi_flag == 1'b1)begin//这里是寄存的作用,不是直接传过来

pi_data_reg <= pi_data;

end

end

//发送数据有效时间段

always @(posedge sclk or negedge s_rst_n) begin

if (!s_rst_n) begin

tx_flag <= 1'b0;

end

else if(bit_flag == 1'b1 && bit_cnt == 'd8)begin

tx_flag <= 1'b0;

end

else if (pi_flag == 1'b1) begin

tx_flag <= 1'b1;

end

end

//一波特时间对应的计数器

always @(posedge sclk or negedge s_rst_n) begin

if (!s_rst_n) begin

baud_cnt <= 'd0;

end

else if (baud_cnt == BAUD_END) begin

baud_cnt <= 'd0;

end

else if(tx_flag == 1'b1)begin

baud_cnt <= baud_cnt + 1'b1;

end

end

//bit_flag

always @(posedge sclk or negedge s_rst_n) begin

if (!s_rst_n) begin

bit_flag <= 1'b0;

end

else if (baud_cnt == BAUD_END - 1'b1) begin

bit_flag <= 1'b1;

end

else begin

bit_flag <= 1'b0;

end

end

//发送数据计数

always @(posedge sclk or negedge s_rst_n) begin

if (!s_rst_n) begin

bit_cnt <= 'd0;

end

else if(bit_cnt == 'd8 && bit_flag == 1'b1)begin

bit_cnt <= 'd0;

end

else if (bit_flag == 1'b1) begin

bit_cnt <= bit_cnt + 1'b1;

end

end

//发送数据

always @(posedge sclk or negedge s_rst_n) begin

if (!s_rst_n) begin

tx <= 1'b1;

end

else if(pi_flag == 1'b1)begin

tx <= 1'b0;//起始位,判断到有输入,立马拉低

end

else if (bit_flag == 1'b1 && bit_cnt <= 'd7) begin

tx <= pi_data_reg[bit_cnt];

end

else if(bit_flag == 1'b1 && bit_cnt == 'd8)begin

tx <= 1'b1;//停止位

end

end

endmodule3、Top层代码

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2023 All rights reserved

// -----------------------------------------------------------------------------

// Author : BigFartPeach

// CSDN : 大屁桃

// E-mail : 2624507313@qq.com

// File : top.v

// Create : 2023-06-20 14:31:06

// -----------------------------------------------------------------------------

module top(

input wire clk,

input wire rst_n,

input wire rx,

output wire tx

);

wire [7:0]data;

wire flag;

uart_rx inst_uart_rx (

.sclk (clk),

.s_rst_n (rst_n),

.rx (rx),

.po_data (data),

.po_flag (flag)

);

uart_tx inst_uart_tx (

.sclk (clk),

.s_rst_n (rst_n),

.pi_data (data),

.pi_flag (flag),

.tx (tx)

);

endmodule第三部分、仿真代码的编写

注意:在testbench同文件位置建立如下文本

00000001

00000010

00000011

00000100

00000101

00000110

00000111

00001000

00001001

00001010

00001011

00001100

00001101

00001110

00001111

111111111、testbench代码

关于top层的testbench代码如下:

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2023 All rights reserved

// -----------------------------------------------------------------------------

// Author : BigFartPeach

// CSDN : 大屁桃

// E-mail : 2624507313@qq.com

// File : top_sim.v

// Create : 2023-04-25 11:24:00

// -----------------------------------------------------------------------------

module top_sim();

reg clk;

reg rst_n;

reg rx;

wire tx;

reg [7:0]mem[15:0];

initial begin

clk = 0;

rst_n = 0;

rx = 1;

#100;

rst_n = 1;

end

always #10 clk = ~clk;

initial begin

$readmemb("./data.txt",mem);

end

initial begin

#200;

read_text();

end

//多次读文本数据

task read_text();

integer i;

begin

for(i = 0; i < 16; i = i + 1)begin

send_bit_data(mem[i]);

end

end

endtask

task send_bit_data(input [7:0]data_txt);

integer i;

begin

for(i = 0; i < 10;i = i + 1)begin

case (i)

0: rx = 0;//起始位

1: rx = data_txt[0];//rx = mem[i - 1];

2: rx = data_txt[1];//rx = mem[i - 1];

3: rx = data_txt[2];//rx = mem[i - 1];

4: rx = data_txt[3];//rx = mem[i - 1];

5: rx = data_txt[4];//rx = mem[i - 1];

6: rx = data_txt[5];//rx = mem[i - 1];

7: rx = data_txt[6];//rx = mem[i - 1];

8: rx = data_txt[7];//rx = mem[i - 1];

9: rx = 1;//停止位

endcase

#104166;//1/9600波特时间

end

end

endtask

top inst_top (

.clk(clk),

.rst_n(rst_n),

.rx(rx),

.tx(tx)

);

endmodule2、仿真结果

可以看到rx与tx的波形一致。

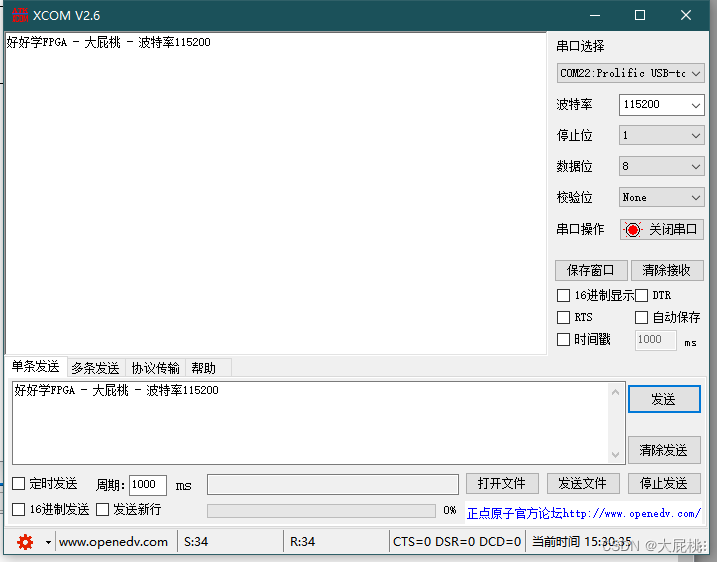

3、上板测试

波特率为9600发送后返回的数据

波特率为115200发送后返回的数据

第四部分、总结

本篇博客介绍了串口的基本知识以及驱动代码的编写,博客中若有错误欢迎大家及时私信我。

最后,希望我的博客对你有帮助😎😎😎😎,有需要的小伙伴可以查看本专栏更多的往期文章专栏链接如下:FPGA的学习之旅_大屁桃的博客-CSDN博客

博客中涉及到的工程链接如下,工程基于ISE软件,没有积分的小伙伴评论留下邮箱即可:

FPGA入门第六篇、异步串口通信工程资源-CSDN文库