一、概览

chiplet技术顺应了芯片生产与集成技术发展的趋势,也开拓了半导体技术发展的新的发展方向,将创造出一种新的芯片设计和商业模式

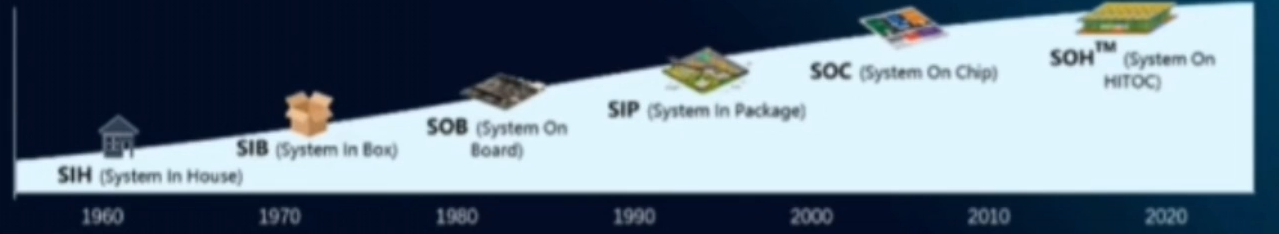

1.1 芯片生产与集成技术发展的趋势

(1)低半径高带宽的物理连线(bandwidth / memory wall)

封装技术的进步给高速总线带来带宽密度的提升、摩尔定律(工艺进步推动芯片性能的提升)

(2)数据搬运开销(power wall)

(3)更高晶体管集成度 (dark silicon)

(4)商业模式的进步

降低成本(设计模块化)

1.2 Chiplet技术特征

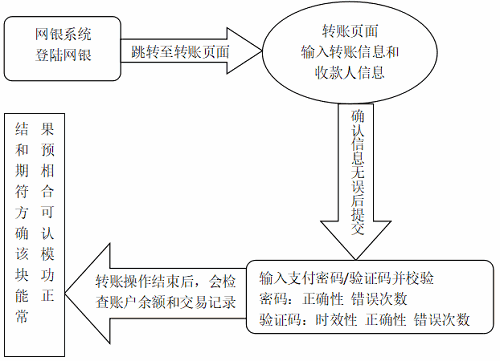

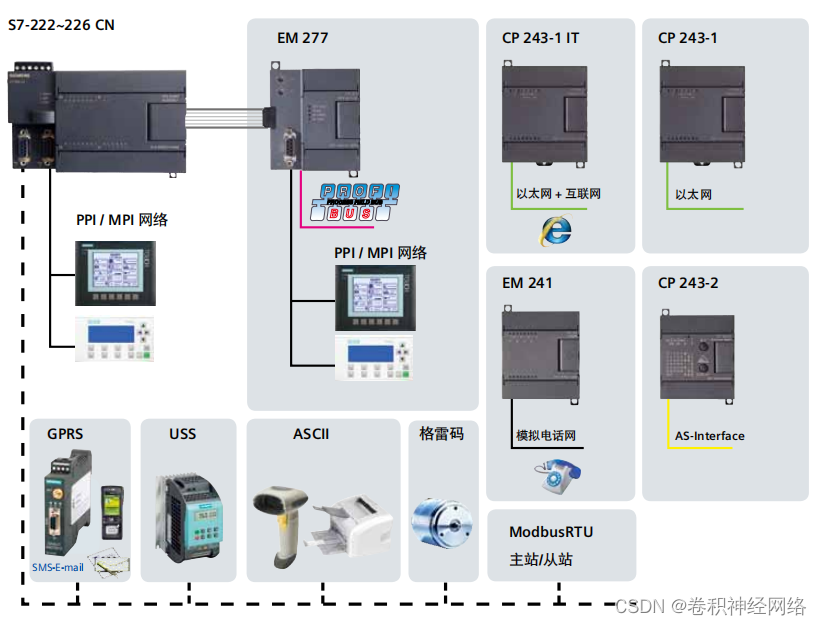

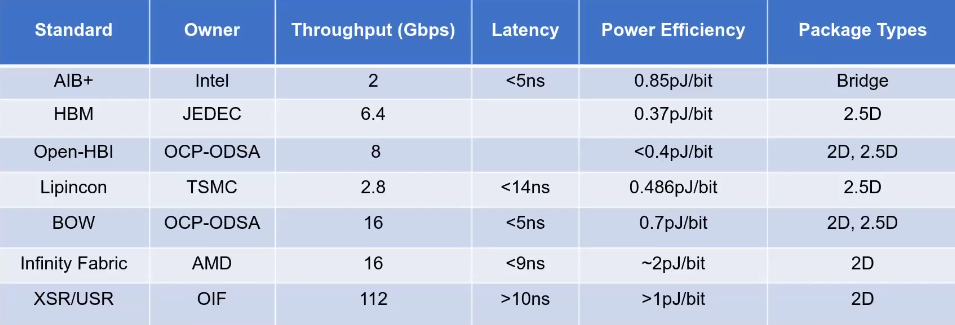

如图(图片来源于奎芯科技直播课)是已有的一些chiplet技术,当前这些技术针对物理层有明确的规范要求,对协议层定义较模糊,需要定制化地对现有协议作配置

1.2.1 chiplet 接口形式

- 串行接口

传统的serdes架构,利用差分对传输,比较适合普通的基板封装(organic substrate)。

XSR/USR属于串行接口。

- 优势:

1)单lane数据传输率较高,带宽较高,目前以达到112GT/s、224GT/s

2)pin脚需求较小 - 劣势:

1)serdes架构,延迟较大

2)功耗较大

3)低密度route

- 并行接口

单端信号传输,forward clock,适合线距较短的先进封装使用。

AIB、HBM、Open-HBI、LIpincon、BOW、UCIe属于并行总线接口。

- 优势:

1)高密度route,整体布局较紧凑

2)低延时

3)低功耗 - 劣势:

1)为保证多组IO引脚之间延迟移植,数据传输率难以做高

2)IO数量多

1.2.2 chiplet技术优势

1)成本优势

2)die的可复用性,敏捷开发优势

1.2.3 chiplet技术难点

chiplet技术虽然不是一个新的技术,但是在即将大规模应用的当下,仍然有很多工程技术问题要解决。

-

芯粒互连

NoC或interposer上互联、Multi-Die计算体系结构的设计、系统级设计的片间划分、 -

芯片封装

先进封装是否足够可靠:

- 材料种类数量提升,材料物性不匹配

- 聚合物材料的引入恶化了先进封装的失效问题

-

EDA技术

Chiplet模块的DFT、验证、可靠性与DFM,封装设计仿真

Synopsys有最新的3DIC Compiler,这也是行业内第一个完整的Chiplet设计平台,具备360o视角的3D视图,支持2.5D/3D封装设计和实现的自动化和可视化,同时面向供电、发热和噪声进行优化。 -

供电和散热技术

集成规模的增大导致整个芯片功率的增大和供电难,散热成本和散热组件在整个计算系统中的体积占比高 -

测试验证

作为封装内的互联总线,无法像外封装一样通过测量仪器对芯片引出来的引脚进行信号质量检测

1.3 chiplet产业生态

1.3.1 Chiplet协议

- UCIe

参考链接:UCIe技术——概览索引

1.3.2 Chiplet组织

- ODSA

ODSA官方链接

1.3.4 chiplet应用案例

-

英特尔:英特尔的Xeon Scalable处理器、FPGA加速器和Ethernet网卡等产品中都使用了UCIe技术。

第五代志强处理器Emerald Rapids -

AMD:AMD的EPYC处理器和Radeon Instinct加速器等产品中也采用了UCIe技术。

参考链接:

从AMD CPU IO Die演进看高速接口IP发展趋势 -

NVIDIA:NVIDIA的Tesla加速器和DGX系统中也使用了UCIe技术。

-

Mellanox:Mellanox的InfiniBand和Ethernet互连解决方案中也采用了UCIe技术。

-

华为lego模式

二、技术架构

2.1 数据传输协议

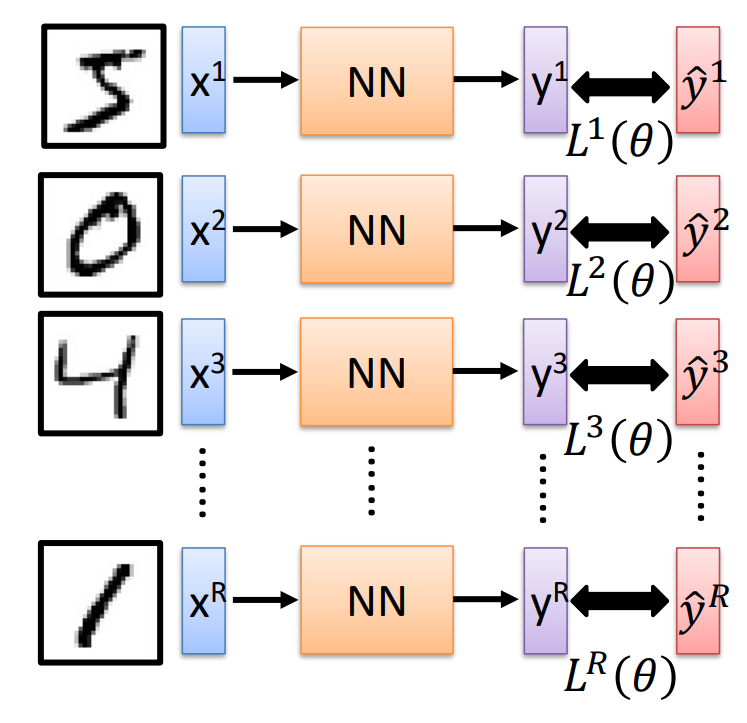

多个chiplet之间需要通过数据传输协议进行数据传输,而该协议可分为一致性协议和非一致性协议。

一致性数据传输

维护一致性的代价和设计的物理面积成正比,因为面积越大,延迟也会越大。常用的一致性数据传输协议有CCIX、CXL、Tilelink、OpenCAPI等。

非一致性数据传输

非一致性协议相比一致性协议,延迟更容易控制,例如Tensorflow就是一款使用非一致性数据传输的加速器。

非一致性数据传输可以通过两种方式实现:

-

一种是将die内互联向die外互联扩展,但大多数die内互联都使用同步总线,向die外扩展不是很容易;

-

另一种是使用在die外互联中使用非一致性数据传输协议,如PCIe。

Netronome已经开发出一款轻量级的可变数据结构和协议用于chiplet间的数据传输。

2.2 物理层信号调制技术

NRZ

Non-Return-to-Zero,即不归零编码。使用两个信号电平来表示数字逻辑信号0/1信息的调制技术,负电平代表0,正电平代表1,波特率和比特率相同。不归零是指每传输完1比特,信号无需返回到零电平,这样可节约数据带宽。

CNRZ

PAM4

4-Level Pulse Amplitude Modulation,4电平脉冲幅度调制,使用四个信号电平来进行信号传输。每个符号周期代表2位逻辑信息。波形有四种电平(1000/0100/0010/0001),分别代表00、01、10、11,即波特率是比特率的一半。

相同码率(比特率)下,PAM4的波特率是NRZ的一半,因此PAM4信令中传输相同数量的符号造成的信号损耗大大降低。

PAM4 的眼高是 NRZ 的 1/3,导致 PAM4 将 SNR(信噪比)提高 -9.54 dB(链路预算惩罚),这会影响信号质量并引入额外的高速信号的限制,垂直眼图开度小也导致PAM4的BER更高,但是前向纠错(FEC)可以改善该问题。