一、SoC架构

1.1 整体架构

Zeppelin

参考链接:wikichip: Zeppelin

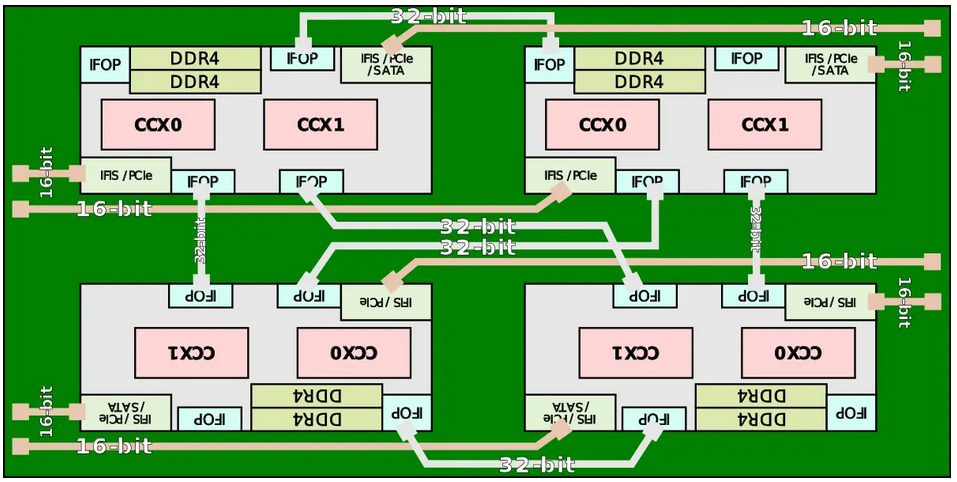

通过infinity fabric总线将单die分成多die的SoC架构,每个Die包含两个CPU核(CCX)、2各DDR通道、USB、低功耗IO以及多个IFOP和IFIS serdes接口。

如下所述中,Zen系列中的每个die都是一个Zeppelin

Zen

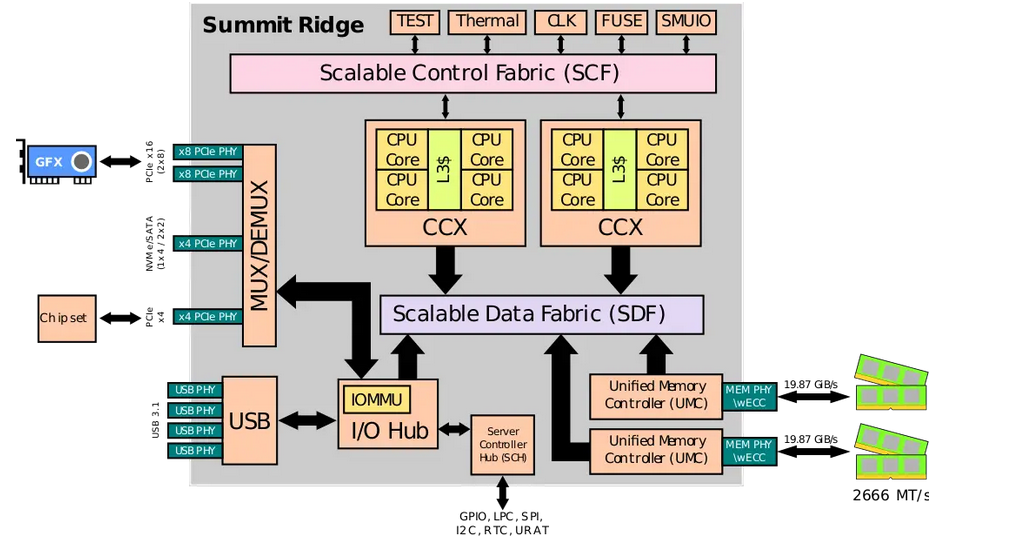

Zen架构使用chiplet技术将多核系统划分为多个die互联封装的架构,单核整体还是一个SoC,包含4个CPU core(core complex,即CCX),南桥模块组(IO)和北桥模块组(DDR)。

- 发布时间:2017年3月2日

- 制成工艺:GF 14 nm

参考链接:wikichip:Zen

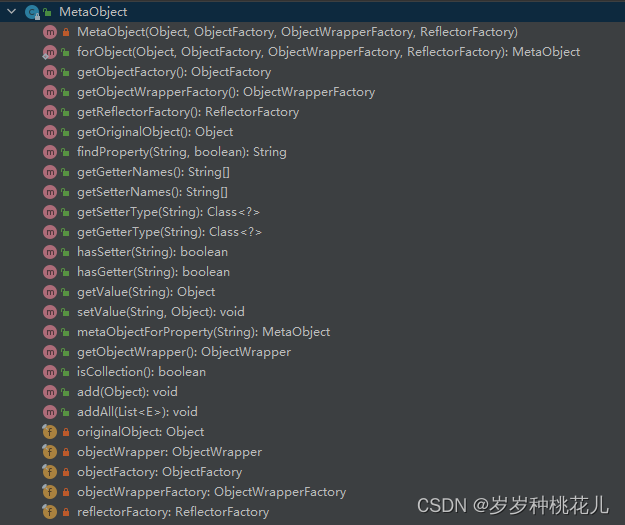

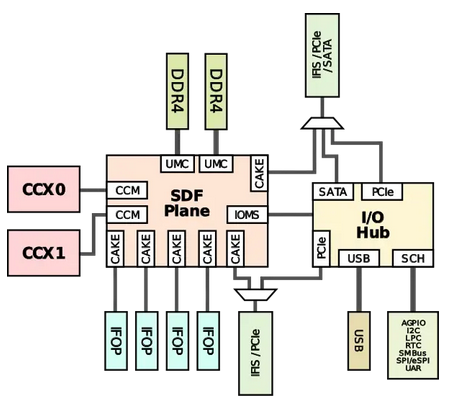

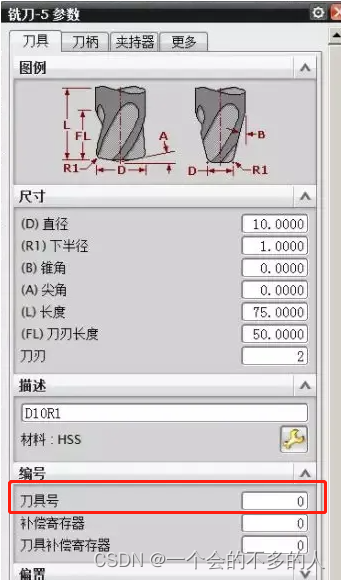

SoC架构如图所示:

单die架构:

单die架构应用于Summit Ridge系列,即高端桌面应用场景。

- CCX

CPU complex,每个CCX包含4个CPU core,CCX间可以通过Infinity Fabric通信(SCF+SDF)

CCX间任务的分配由cache-corherent non-uniform memory access(ccNUMA-aware)实现,确保线程不会从一个CCX迁移到另一个是很重要的,由于CCX间数据通信需要额外的延迟,线程的搬移会引起不必要的性能损耗。

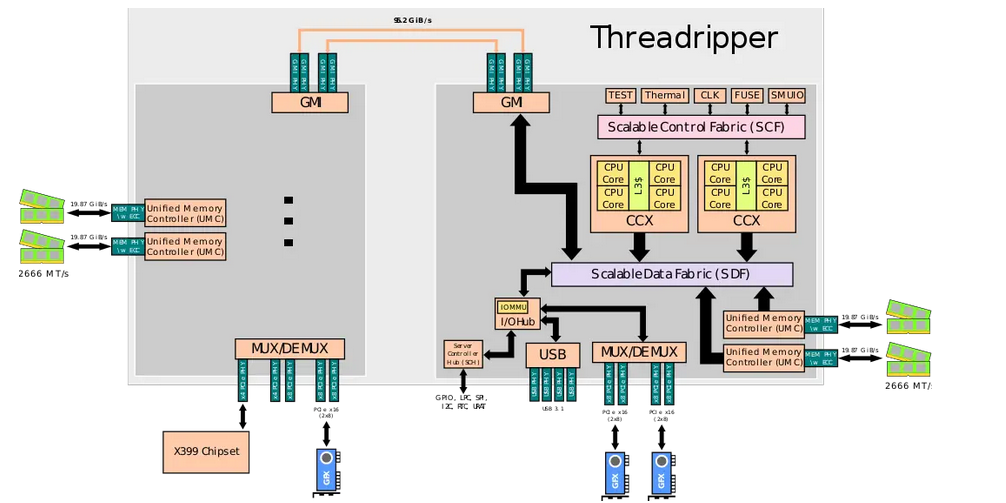

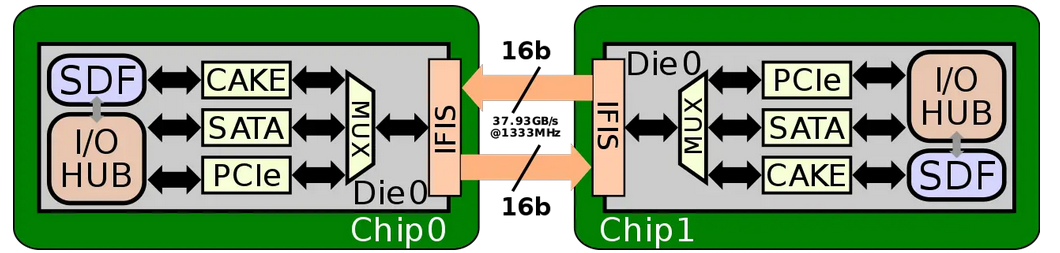

双die架构:

双Die架构应用于Ryzen Threadripper系列,即高性能桌面或工作站场景。

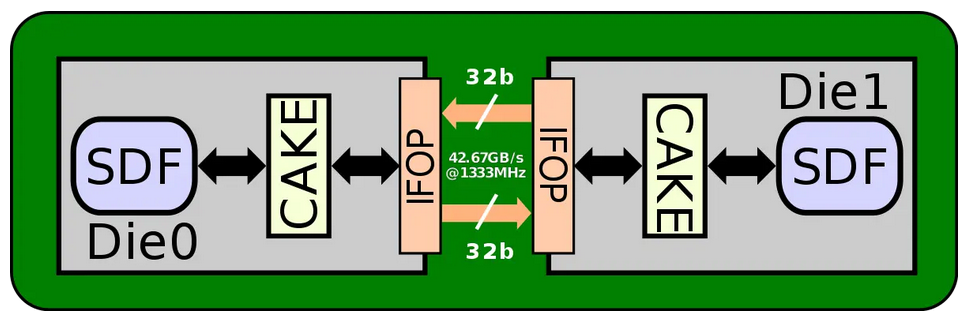

两个die通过Infinity Fabric协议处理,并经GMI(global memory interconnect)接口相连

- GMI接口

die-to-die的IFOP接口,每个时钟cycle传输16B read + 16B write。

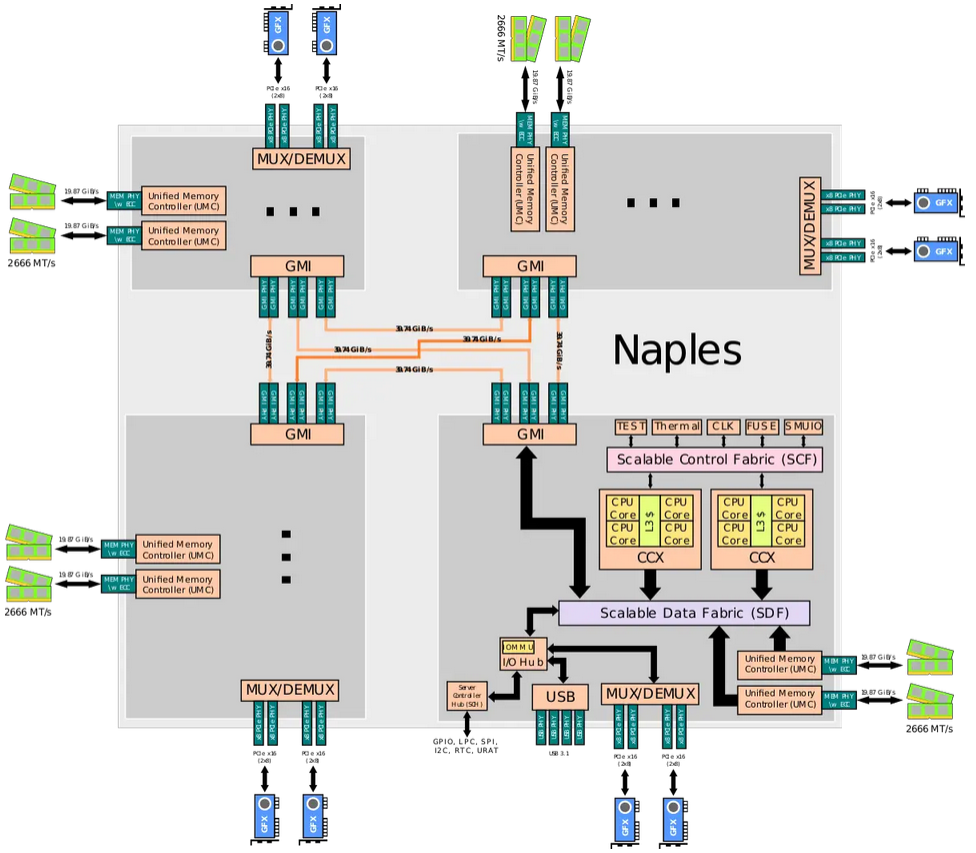

四die架构

四die用于EPYC系列,即服务器场景。EPYC系列的die和Threadripper系列相同。

-

每个die有四组GMI接口,但只有和其他die最近的三组接口被使用

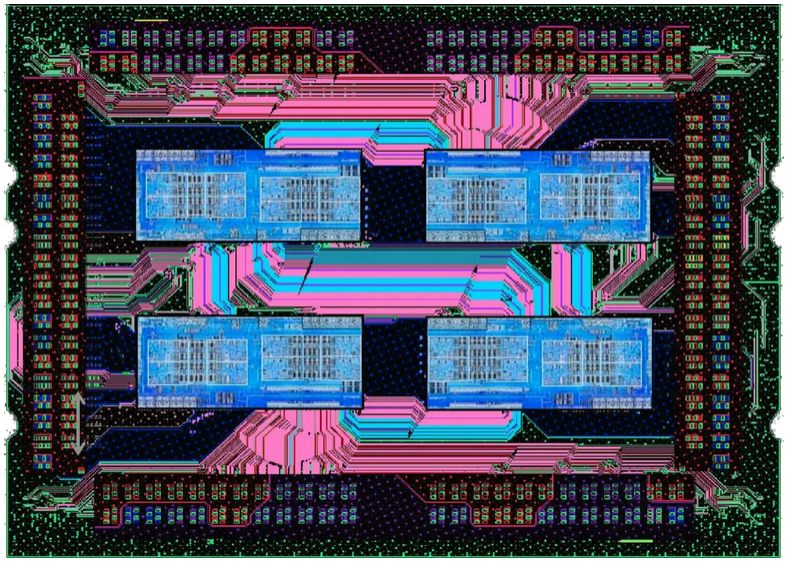

如图是EPYC系列die互连某层的布局布线图,视图上方和下方的粉色布线是die的UMC出来的接口,视图中间的粉色和蓝色布线是双向的GMI链路,左下和右上die的连接被隐藏了,左上芯片和右上芯片摆放位置相同,下面的芯片摆放旋转180度。 -

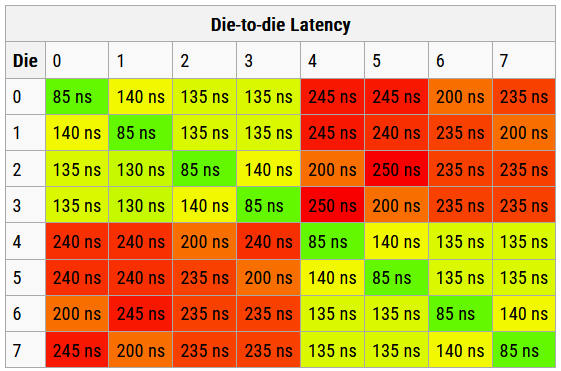

die间延迟如图所示

die0-3和die4-7分别为两路CPU。

Zen+

Zen2

Zen2架构同样是多die结构,但基于Zen架构将IO和memory controller剥离出来单独成die,CPU core单独成die。因此每个core访问ddr的延迟均一样。注意PCIe并没有放在IO die中,而是在CCD中,每个CCD都有各自PCIe控制器,因此该架构的PCIe lane数量可以有很多。

将IO分离的另一个好处是,AMD可以通过先进制程将CPU做的更小,而物理接口并不会因为制程的提升导致性能很大的改进,这将极大的减小成本。

- 发布时间:2019年

- CPU die: TSMC 7nm

- IO die: GF 14nm (server) ; GF 12nm (client)

CCD

CPU die即为core complex die(CCD),每个CCD有两个CCX,一个SMU 和一个GMI2接口模块。

- SMU

system management unit,系统管理单元,读取温度、电压、电流数据,并调整CPU主频和电压,限制IO die的fast local closed loop和global loop。CCD和IO die间SMU的通信通过单lane的IFOP接口。 - GMI2

global memory interconnect version 2,GMI2在GMI的基础上扩展了CCD和IO die连接的数据接口,即32 lane的双向IFOP接口;同时传输带宽增加到每个时钟cycle传输32B read + 16B write。

IO die

- 8个DDR通道

1.2 服务器芯片

Rome

基于Zen2架构构建的服务器微处理器,总共有9个die,分别为1个IO die和8个CCD(core complex die)

二、CPU Core架构

三、互联方式

3.1 Die间互联

3.2 Die内互联

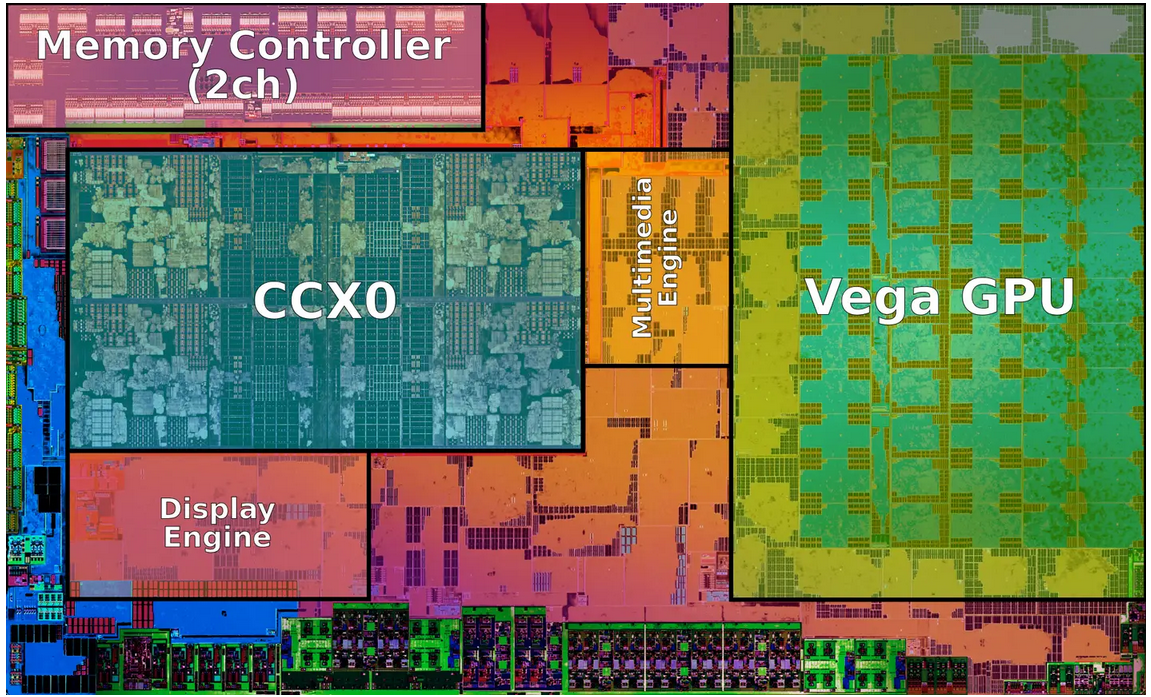

ONION (Fusion Compute Link)

GPU和CPU互联的一致性总线,用于cache snooping

GARLIC (Radeon Memory Bus)

GPU和Memory controller连接的非一致性总线,

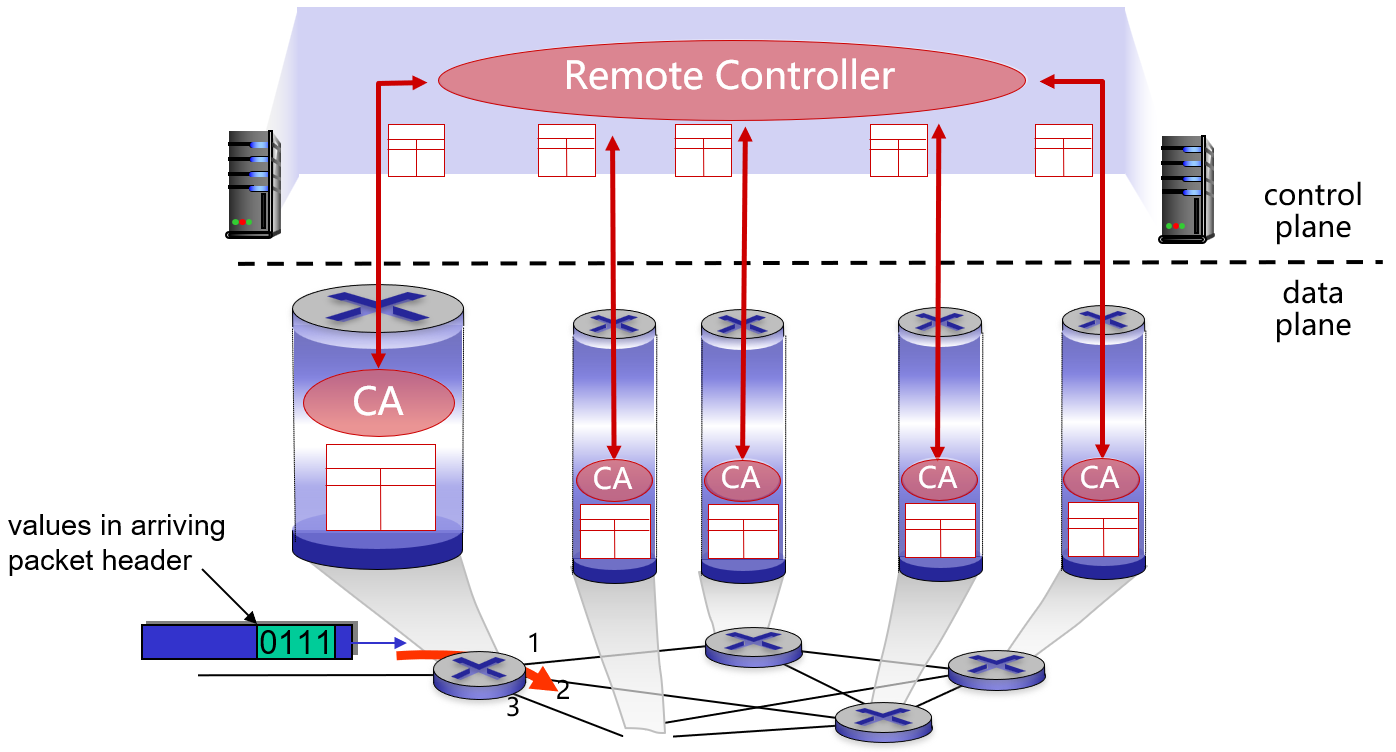

3.3 通用互联总线

Infinity Fabric协议

参考链接:wikichip:Infinity Fabric

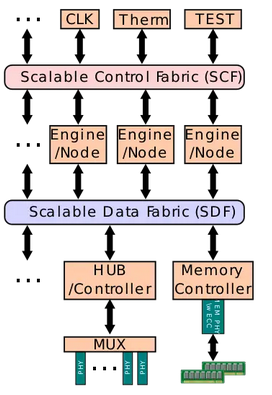

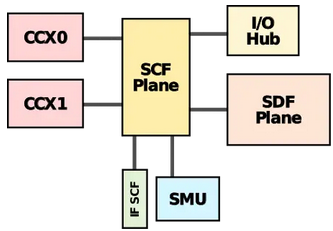

定义了AMD片间互联和片内互联的模块架构和互联关系,模块包括SDF (Scalable Data Fabric) 和SCF (Scalable Control Fabric),总线接口包括IFOP(infinity fabric on-package)和IFIS(infinity fabric intersocket)

连接模块

SDF用于各个子系统间业务数据流的通信,包括NUMA节点间、各子系统PHY间等,可以保证数据的一致性。

SCF用于处理各子系统控制信号,包括热管理、功耗管理、测试、安全等

通过这两种模块,AMD可以任意扩展基础计算模块。

(1)SDF

SDF可以保证数据的一致性,因此通过SDF的互联不会局限于在单Die内连接,也可以扩展到多个Die;总线拓扑既可以是点对点连接,也可以是中心岛结构

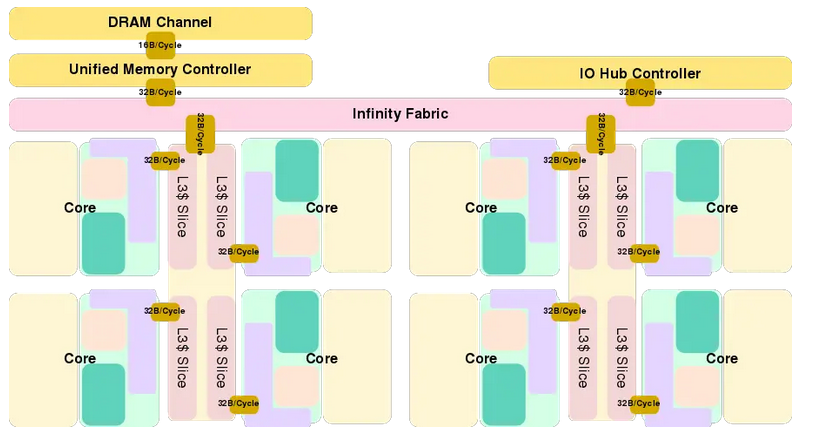

如图所示是一个点对点结构和中心岛结果混合的单die架构:

- 两个CCX通过CCM (Cache-Coherent Master)连接到SDF平台,CCM提供core数据一致性访问维护机制;

- IO Hub模块通过IOMS (I/O Master/Slave)接口和SDF相连。

- DDR4通过UMC (Unified Memory Controller)与SDF相连,时钟频率和DRAM memclk相同

- serdes接口通过CAKE (coherent AMD socket extender)与SDF连接,CAKE负责串行编码和解码,每个cycle发送128bit串行数据,时钟频率和DRAM memclk相同,serdes接口包括IFOP和IFIS。

- 在SDF模块中,只可以通过CCM和IOMS访问DDR

(2)SCF

SCF通过单独的IFIS接口和外部的设备连接

总线接口

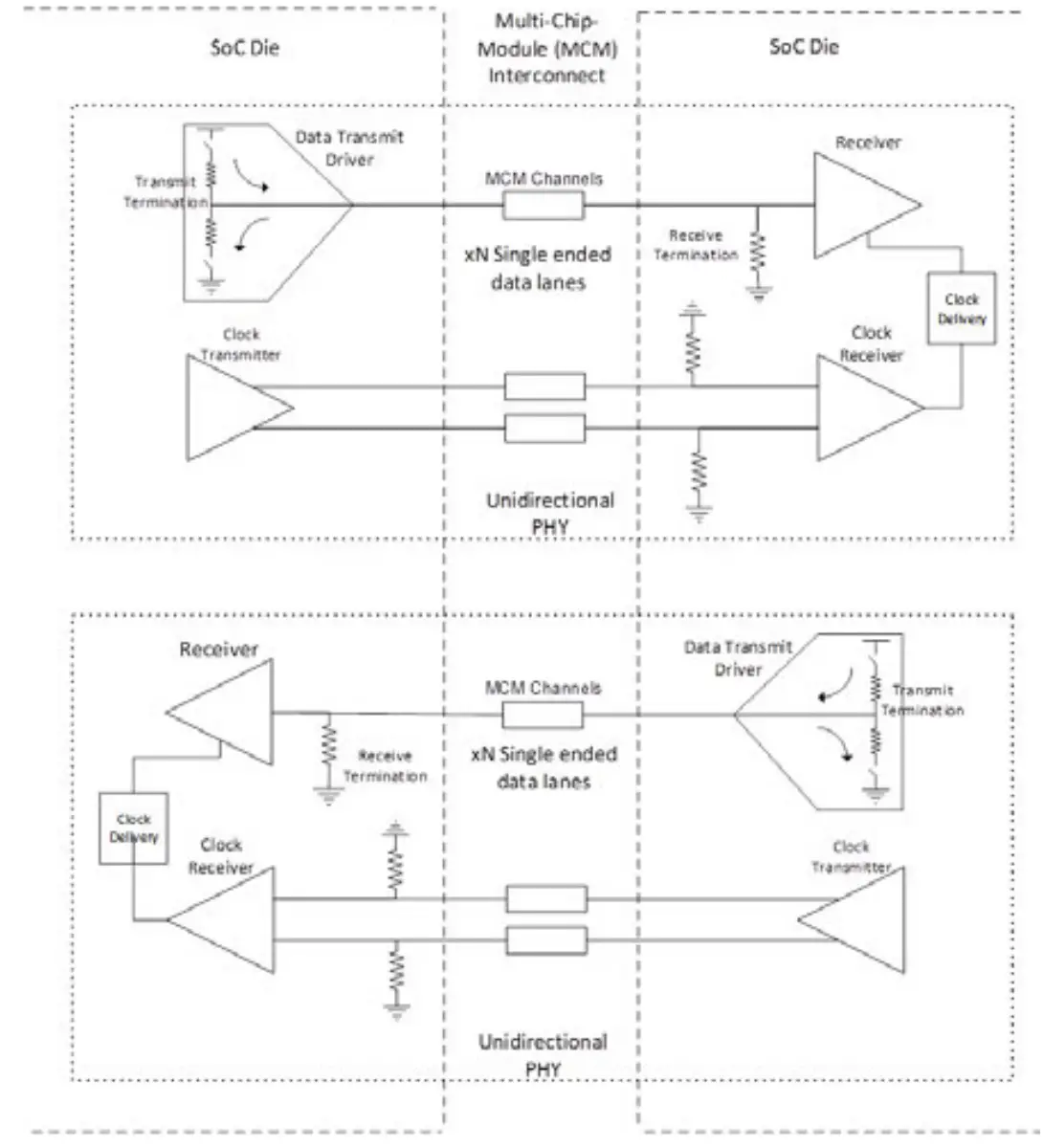

(1)IFOP

封装内die-to-die的连接,

- 32bit单端data信号

- 差分时钟

- 能耗2 pJ/b

- 串行全双工

(2)IFIS

封装与封装间的通信

- 16位差分data,每个CAKE时钟周期进行8次传输

- 无时钟信号

- 能效11pJ/b

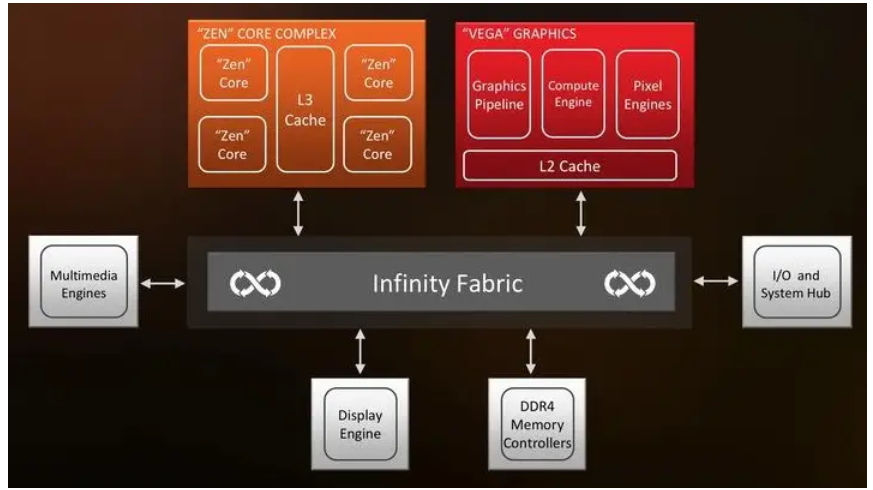

四、GPU架构

Zen-based APU

- GF 14nm

基于Zen架构的加速器处理单元是一个完整die,包括一个CCX、一个Vega计算核心和其他部件通过infinity Fabric互联组成的系统,

![栈的运用——中缀表达式[Java实现]](https://img-blog.csdnimg.cn/c10f2957019340e49a611ecf965364c9.png)