时钟同步和仲裁

在单主设备中,不需要时钟同步和仲裁。而在多设备时,多个主设备可以同时在空闲的总线上开始发送数据,这时就需要仲裁决定哪一个来控制总线并完成它的数据传输,有时候也需要时钟同步来协同设备间的工作。而这正是通过时钟同步和仲裁来完成的。

1、时钟同步

有的时候,主机的速度快于从机的速度,或者从机需要处理其他事情而不能及时地从主机接收数据或者向主机发送数据。如果从设备希望主设备降低传输速率,可以通过将SCL主动拉低,延长SCL低电平时间的方法来通知主设备。当主设备下一次传输时发现SCL电平被拉低时,就进入等待,直到从设备完成操作并释放SCL线。这就要使用时钟同步来完成。

- 时钟同步是通过连接到SCL总线的I2C接口“线与”实现。

- SCL线上的低电平时间是由时钟低电平最长的器件决定,SCL的高电平则是由高电平时间最短的期间决定。

- 时钟同步解决了I2C总线设备间的速度同步

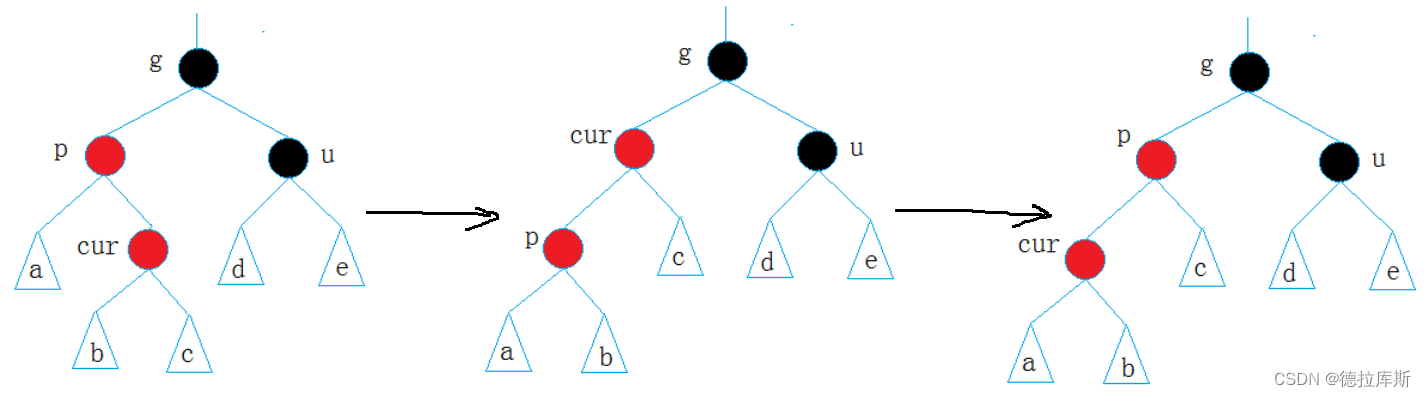

时钟同步的过程:

- 一旦主设备1的时钟拉低,就会把SCL总线拉低。当SCL总线从高拉低时,主设备将计数主设备时钟的低电位周期。

- 主设备2检测到SCL线为低,也会立刻将CLK1拉低,不会等到CLK1的正常周期才拉低。

- 如果此时另外一个主设备的时钟仍然是低电平的,此时SCL总线也同样的保持为低。在此期间,低周期比较短的主设备1将进入高电平状态等待。如图,主设备1提前进入高电平等待,主设备2继续保持低电平。

- 当所有主设备的时钟都为高电平时,将会把SCL线拉高。也就是说时钟低电平周期较长的主设备2决定了SCL线为低的周期长度。

- 所有的主设备时钟都拉高时,将对他们的高电平时钟计数,第一个结束时钟高电平周期的主设备将会把SCL线拉低。主设备2将SCL拉低后,主设备1检测到SCL线为低时,CLK1也立刻拉低。

2、仲裁

仲裁和同步是一样的,只有在系统使用多个主设备时才需要,而从设备(slave)不参与仲裁程序。当然,只有在主线空闲的情况下,主设备才可以发起传输。两个主机可以在启动条件的最小保持时间内生成一个启动条件,从而在总线上生成一个有效的传输启动条件,然后仲裁程序决定哪一个主设备可以完成它的传输。

- 谁先在SDA线上发送低电平,谁就掌握对总线的控制权。

- I2C总线的控制权完全取决于竞争主设备发送的地址和数据,因此没有中央主设备,总线上也没有任何优先级顺序。

仲裁的步骤:

- 当两个master对同一个地址的slave进行传输时,多个master会都能进入数据周期,仲裁会单比特对单比特进行比较。

- 在SCL为高的每一个比特位期间,每个主设备检查SDA线的电平是否与它所发送的相匹配。这个过程很可能需要比对很多位。

- 如果传输的数据时完全相同的,则这个主设备可以完成地发送整个事务。

- 当主设备发送的比特位与SDA线不匹配时,例如图中DATA1在SCL线的第三个周期,此时DATA1拉高,而DATA2W为低,DATA1和DATA2在线与后SDA为低,匹配不成功。当主设备1检测到一个与自身不相符的低电平,这时会关闭主设备1的SDA传输驱动,另一个主设备2会继续完成传输。

时钟拉伸

其实我觉得时钟拉伸就是完成时钟同步中的事,将主从设备间数据传输同步。时钟拉伸是通过保持SCL信号拉低来暂停事务的,期间传输不能继续,直到SCL信号再次被拉高。时钟拉伸需要设备包含SCL驱动程序,而大多数的从设备不包含SCL驱动程序,所以他们无法拉伸时钟。

在字节传输级别,设备可能能够以较快地速度接受字节数据,但是需要更多的时间来存储接受到的字节或准备传输另一个字节。在字节发送ACK位之后,从设备可以拉低SCL总线,迫使主设备进入等待状态,直到设备准备好下一个字节的传输。

在比特级别,无论是否为I2C总线提供有限的硬件,都可以通过延长每个时钟的低周期来降低总线时钟时钟的速度。

注意:在高速模式下,这个通过拉伸时钟的握手功能只能在字节传输级别使用