目录

组合逻辑毛刺消除

1、简介

2、实验任务

3、程序设计

1、组合逻辑输出加寄存器

2、信号同步法

(1)信号延时同步法

(2)状态机控制

3、格雷码计数器

4、仿真验证

组合逻辑毛刺消除

信号在 IC/FPGA 器件中通过逻辑单元连线时,是存在延时的。延时的大小不仅和连线的长短和逻辑单元的数目有关,而且也和器件的制造工艺、工作环境等有关。因此,信号在器件中传输的时候,所需要的时间是不能精确估计的,当多路信号同时发生跳变的瞬间,就产生了“竞争冒险”。这时,往往会出现一些不正确的尖峰信号,这些尖峰信号就是“毛刺”。

1、简介

毛刺是数字电路设计中的棘手问题,它的出现会影响电路工作的稳定性、可靠性,严重时会导致整个数字系统的误动作和逻辑紊乱。

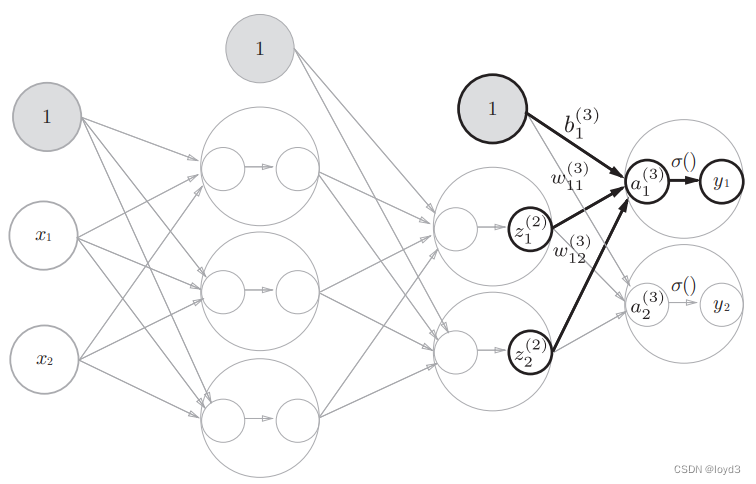

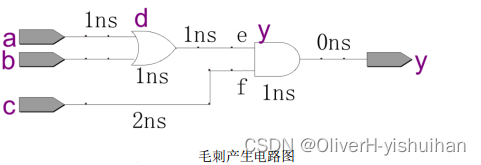

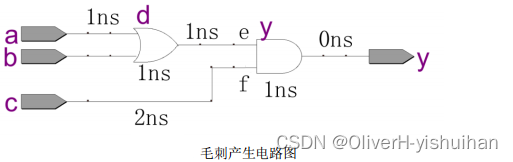

首先我们先来看下毛刺是如何产生的。下图是一个简单的组合逻辑电路,由一个或门和一个与门构成,输入信号是 a、b 和 c,输出信号是 y。

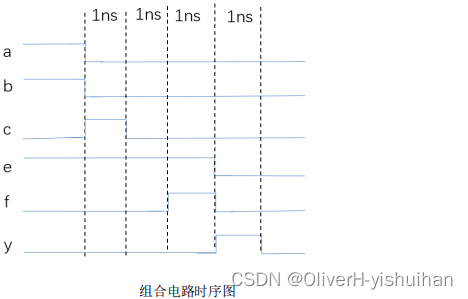

从图中,我们可以假设或门电路的延迟是 1ns,路径延迟也有时间,c 到 y 门电路的延迟是 2ns,a 到 d 门电路的延迟是 1ns,那么我们可以画出一个时序图如下:

e 点为 a 和 b 信号相或后到达 y 门输入端的信号,总共延迟为 3ns,f 点为 c 信号到达 y 门输入端的信号,总共传输延迟为 2ns,然后 f 信号和 e 信号做与逻辑处理,得到 y 信号。y 信号最终由一个 1ns 的脉冲信号,这个信号就是路径延迟导致的一个毛刺信号。假设不考虑门电路延迟和信号传输延迟,y 应该是一直为低电平的。这个就是组合逻辑的毛刺信号产生的由来。

2、实验任务

思考组合逻辑毛刺去除有哪些方法。

3、程序设计

组合逻辑毛刺去除主要有以下几种方法:

1、组合逻辑输出加寄存器

这是一种比较常用的去除毛刺的方法。去毛刺原理就是用一个寄存器去读带毛刺的信号,利用寄存器对输入信号的毛刺不敏感的特点(寄存器一般只在时钟跳变沿对输入信号敏感),去除信号中的毛刺。在实际电路中,对于简单的逻辑电路,尤其是对信号中发生在非时钟跳变沿的毛刺信号,去除效果非常的明显。但是如果毛刺信号发生在时钟信号的跳变沿,寄存器的效果就没有那么明显了(加寄存器以后的输出端,仍含有毛刺)。另外,寄存器的使用还会给系统带来一定的延时,特别是在系统级数较多的情况下,延时也将变大,因此在使用寄存器去除毛刺的时候,也要视情况而定,并不是所有的毛刺都可以用寄存器来消除。

2、信号同步法

设计数字电路的时候采用同步电路设计可以大大减少毛刺。由于大多数毛刺都比较短(大概几个纳秒),只要毛刺不出现在时钟跳变沿,毛刺信号就不会对系统造成危害了。因此一般认为,只要在整个系统中使用同一个时钟就可以实现系统同步。但是,时钟信号在 FPGA 器件中传递时是有延时的,我们无法预知时钟跳变沿的精确位置。也就是说我们无法保证在某个时钟的跳变沿读取的数据是一个稳定的数据,尤其是在多级设计中,这个问题就更加突出。因此,做到真正的“同步”就是去除毛刺信号的关键。所以,同步的关键就是保证在时钟的跳变沿读取的数据是稳定的数据而不是毛刺数据。

下面介绍两种具体的信号同步方法。

(1)信号延时同步法

信号延时法,它的原理就是在两级信号传递的过程中加一个延时环节,从而保证在下一个模块中读取到的数据是稳定后的数据,即不包含毛刺信号。这里所指的信号延时可以是数据信号的延时,也可以是时钟信号的延时。

举个例子,比如还是下面的这个毛刺产生电路,如果把 c 到 f 的延迟增加 1ns,就是 c 到 f 的延迟总共 3ns,和 a 到 e 的延迟一致,那么此时 y 的输出就不会有毛刺产生。

(2)状态机控制

使用状态机也可以实现信号的同步和消除毛刺的目的。在数据传递比较复杂的多模块系统中,由状态机在特定的时刻分别发出控制特定模块的时钟信号或者模块使能信号,状态机的循环控制就可以使得整个系统协调运作,同时减少毛刺信号。那么只要我们在状态机的触发时间上加以处理,就可以避免竞争冒险,从而抑制毛刺的产生。

3、格雷码计数器

对于一般的二进制或十进制计数器,在计数时,将有多位信号同时跳变。例如一个 4bit 二进制计数器,由 “1111” 转换为 “0000” 时,就会产生毛刺。此时,使用格雷码计数器将避免毛刺的出现,因为格雷码计数器的输出每次只有一位跳变。

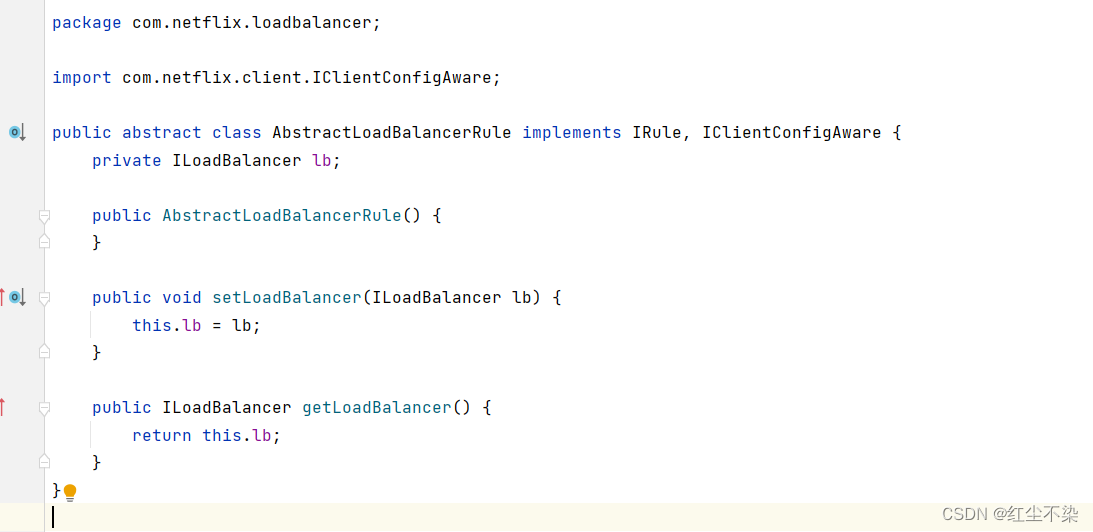

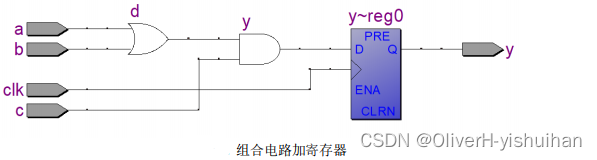

我们选择组合逻辑加寄存器去毛刺方法来解决间距中的毛刺信号,我们先画出加寄存器后的电路图。

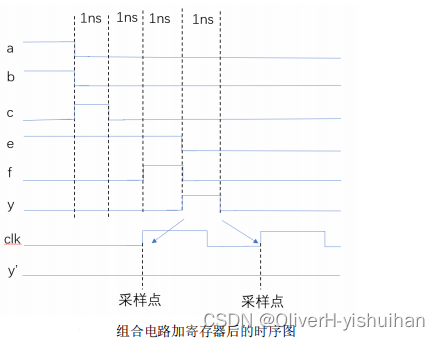

然后后面再画出这个电路对应的时序图,

从图中可以看出,加了一级寄存器后,毛刺信号不会被寄存器采样到,因为寄存器只在时钟的跳变沿变化,毛刺信号是组合逻辑产生的,实际电路里面组合逻辑的信号变化一般也是由寄存器变化引起的信号变化,所以一般发生在时钟跳变之后,而寄存器只在时钟的跳变沿对输入信号采样,所以毛刺信号一般不会被采样到,这种加寄存器过滤毛刺的方法就是基于这一点设计的。

4、仿真验证

本节不需要进行仿真。