晶振电路设计

晶振中负性阻抗的原理

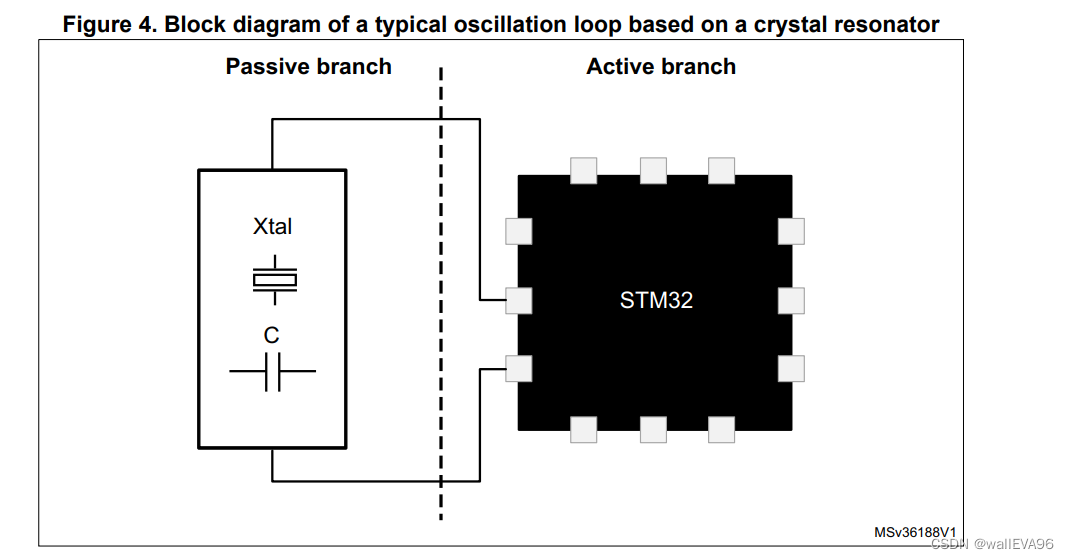

- 晶振的回路主要由两部分组成, 一部分是激活分支, 用于提供能量给晶振启动直至达到稳定的相位,另一部分是被动分支, 主要由电阻, 两个外部负载电容以及所有的寄生电容, 如下图:

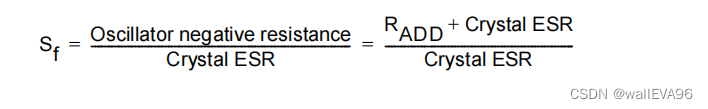

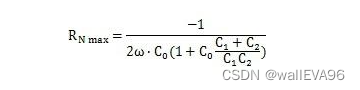

为了确保晶振启动及稳定地工作, 需要确保晶振回路中的负性阻抗是晶振最大等效串联电阻ESR的3倍以上, 如果是高速晶振,需要确保是5倍以上。 - 晶振的安全系数公式如下:

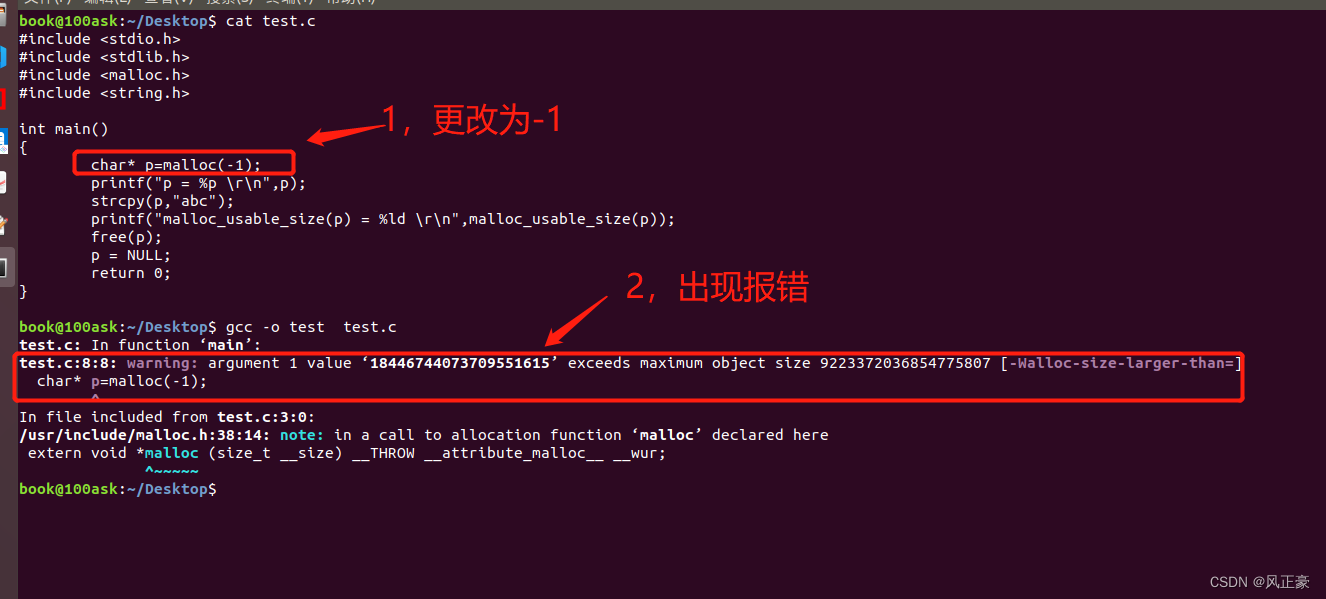

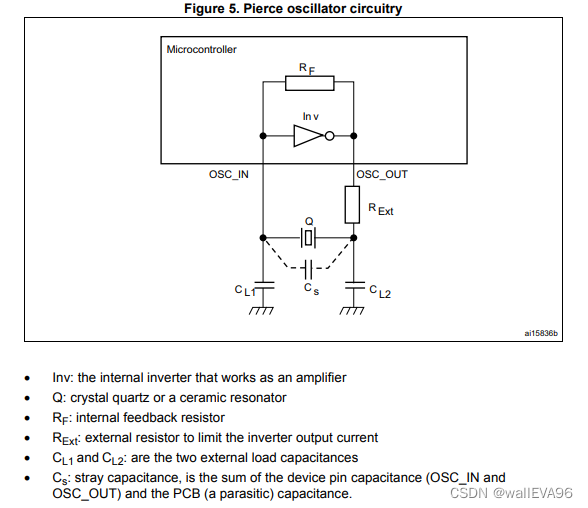

- 如何测量晶振的负性阻抗, 通过如下的电路图,缓慢增大

R(ADD)电阻,观察晶振的工作状态, 直到晶振无法正常启动, 此时R(ADD)的电阻值就是电路中的负性阻抗。

电路设计

本文主要参考st的晶振设计指导手册:oscillator-design-guide-for-stm8af-al-s-stm32-mcus-and-mpus-stmicroelectronics.pdf

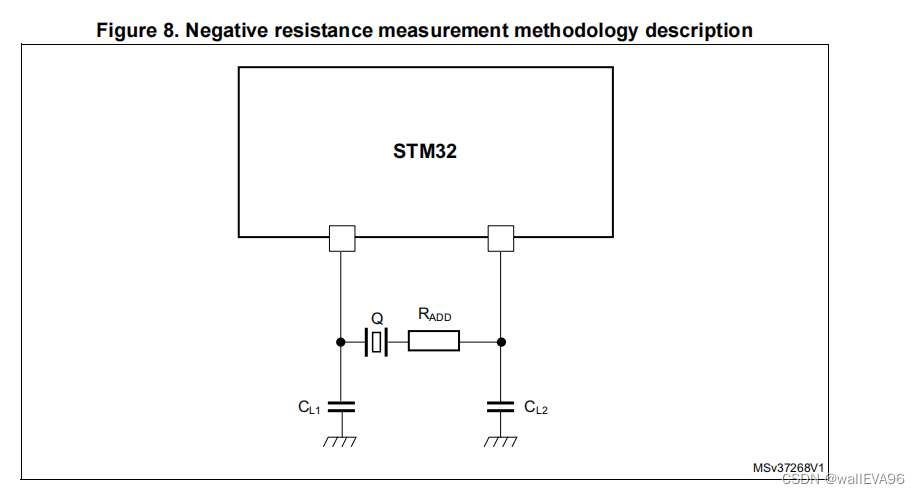

以下是经典的皮尔斯晶振电路:

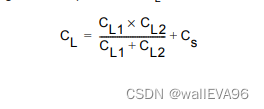

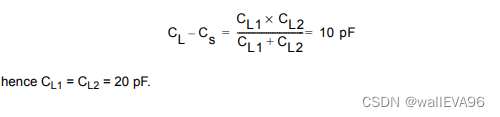

关于晶振负载电容的计算公式:

比如说:晶振的负载电容CL为15pf, 杂散电容 Cs为5pf,

那么晶振的外部负载电容如下计算:

晶振的跨导

- 跨导类似于电导,电导是电阻的倒数,跨导也可以定义为微分电导, 表达式为 ∆I / ∆v。

- 为了确保晶振稳定启动和运行,芯片的共振器一定要提供足够的能量。 有两种办法可以确认st芯片的振荡器是否与电路匹配。

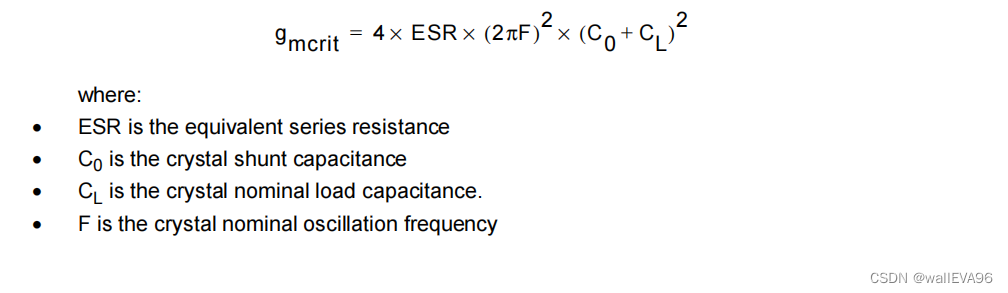

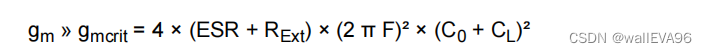

- 需要计算晶振回路中的临界跨导,

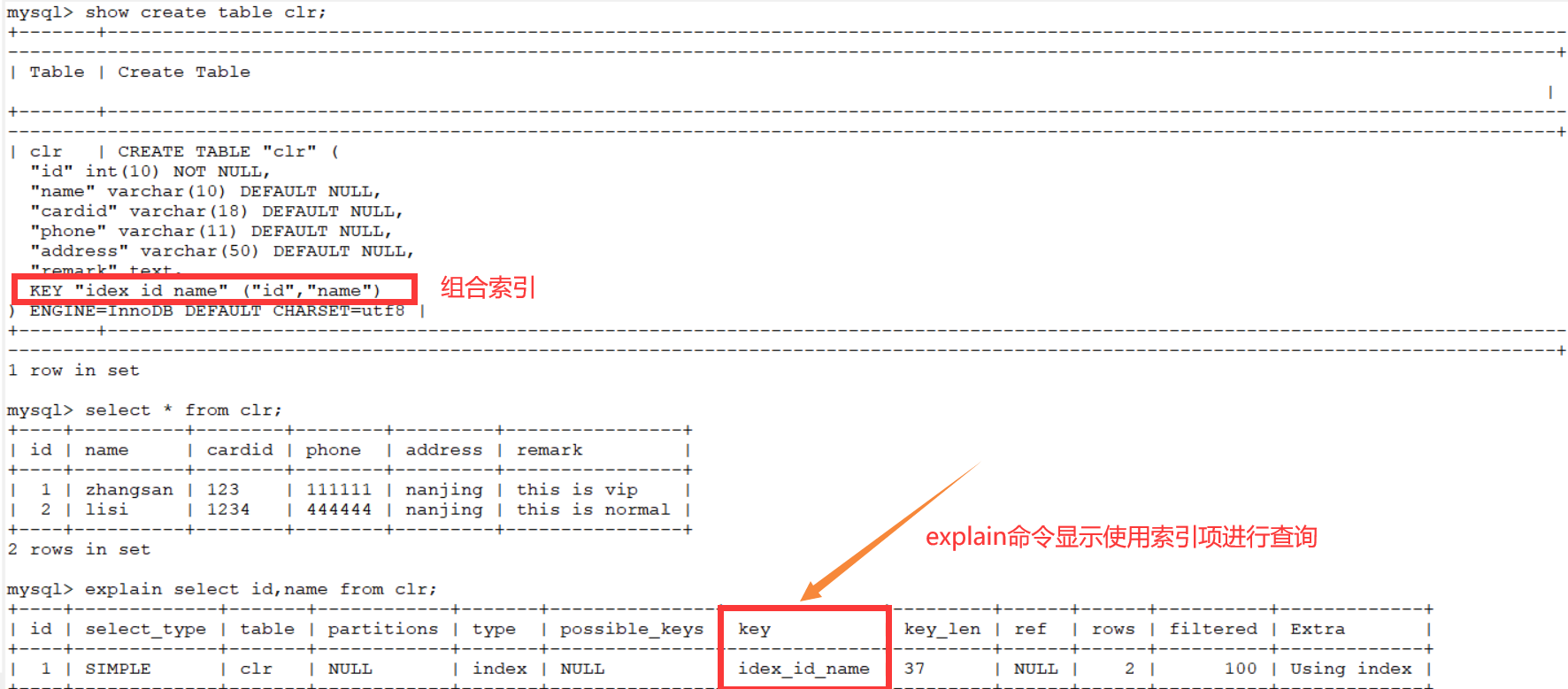

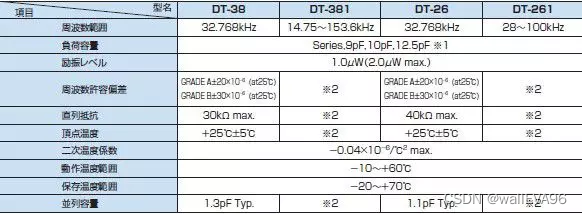

DT-26晶振的数据参数:

DT-26晶振的数据参数:

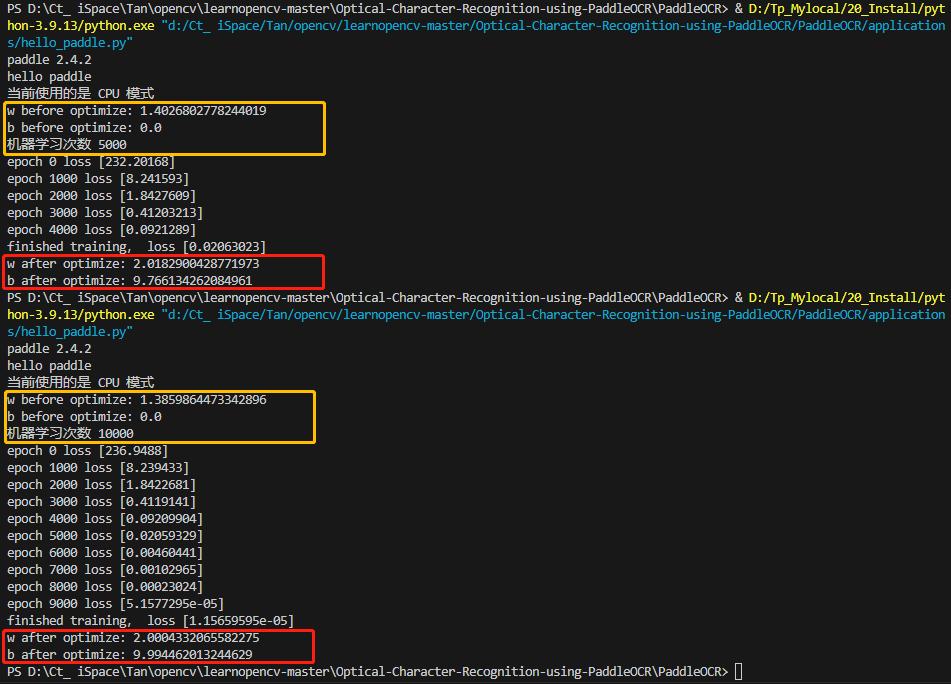

为此我们需要从晶振的手册里面获取等效串联电阻ESR的大小, 也就是40k欧姆, 我们假设寄生电容C0为1.1pf,晶振的额定负载电容CL为12.5pf,则计算如下, 也即是为1.253ua/v.,注意: 一般高速晶振的临界跨导为ma/v, 低速晶振的临界跨导为ua/v。

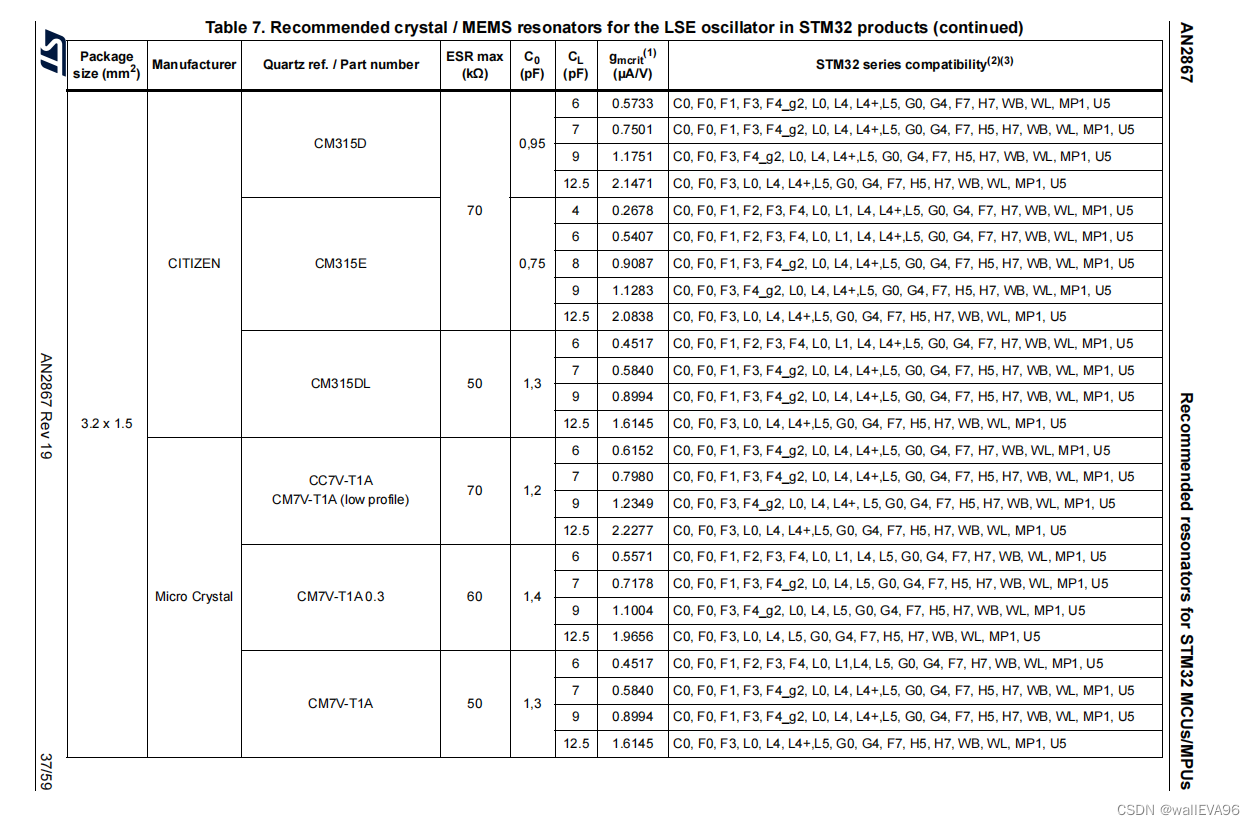

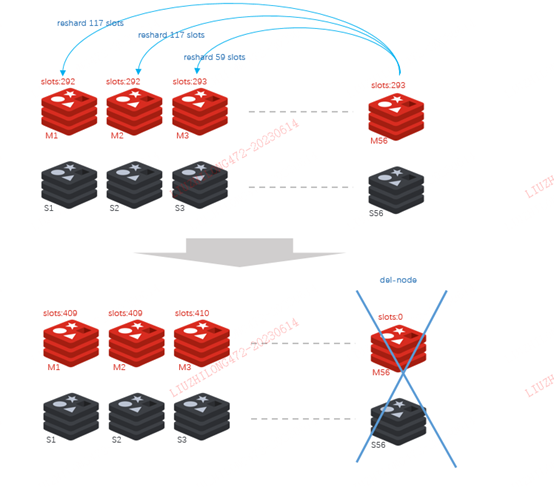

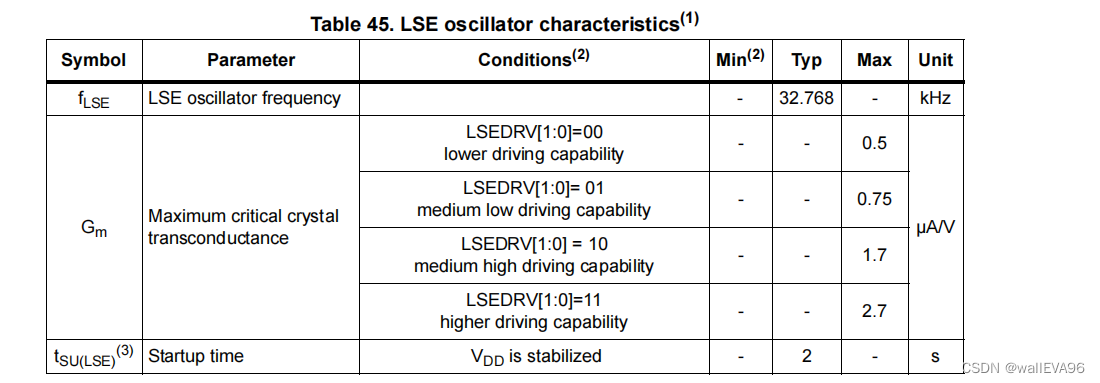

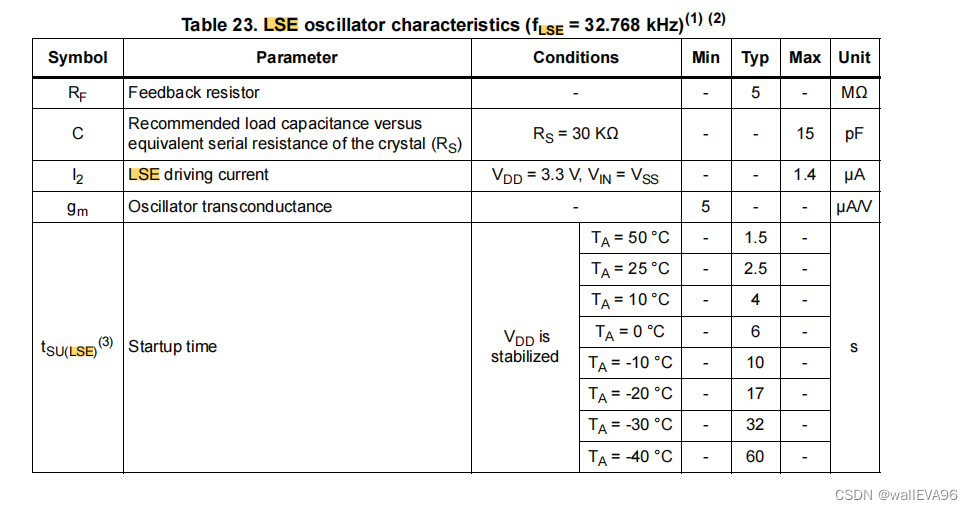

2. 在stm32的产品中,有的产品会指出晶振回路中能提供的最大临界跨导G(m_crit_max)。 我们可以通过LSEDRV来配置不同的驱动等级,以此来获得不同的驱动能力,而我们需要做的就是计算回路中晶振的临界跨导g(mcrit),并通过配置LSEDRV来保证G(m_crit_max)大于g(mcrit)。 如上计算, 在该例子当中,我们就需要选择LSEDRV[1:0] = 10驱动等级,也就是芯片的最大临界跨导为1.7ua/v。

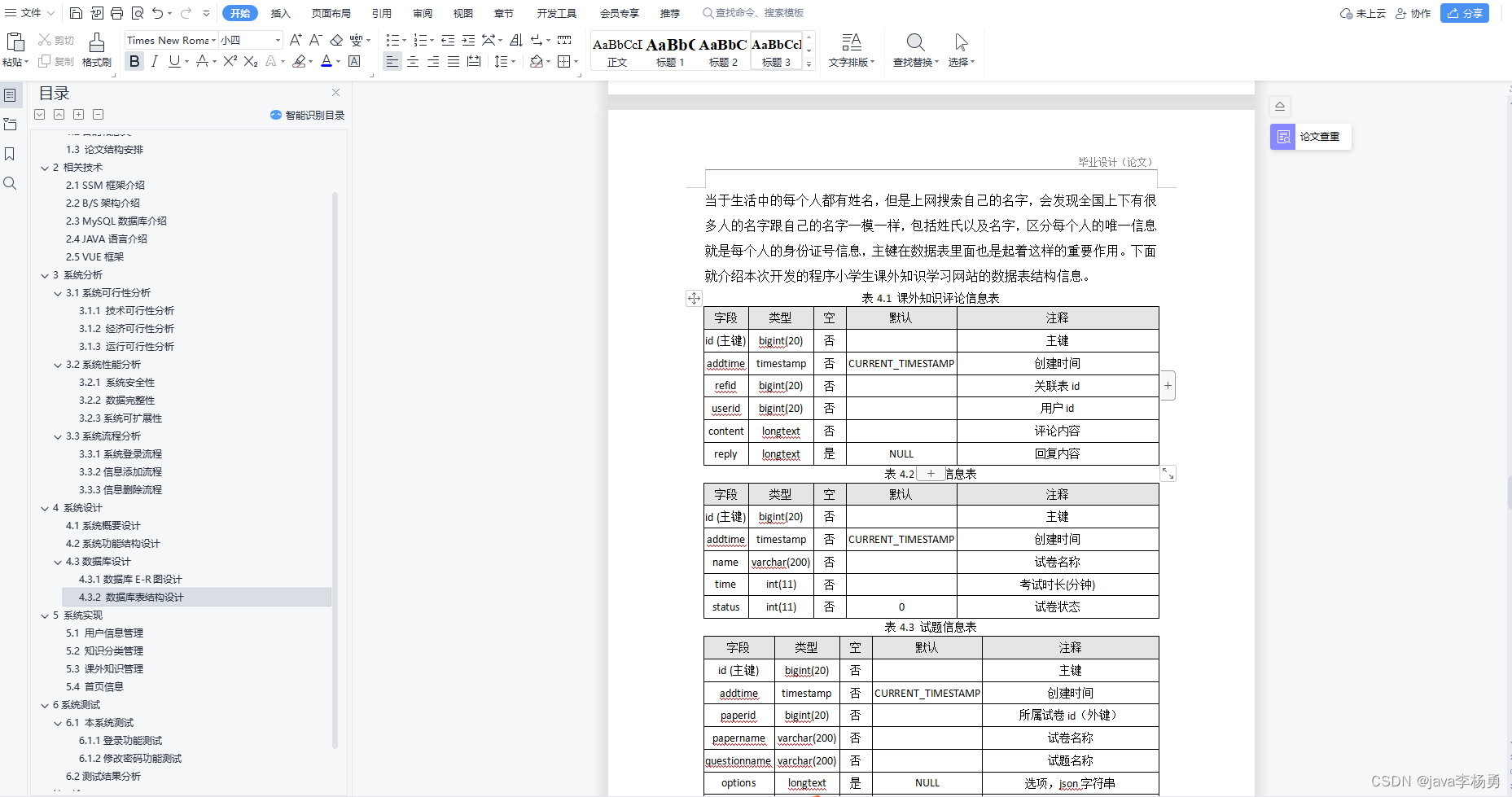

stm32 LSE晶振的不同驱动水平的参数特性:

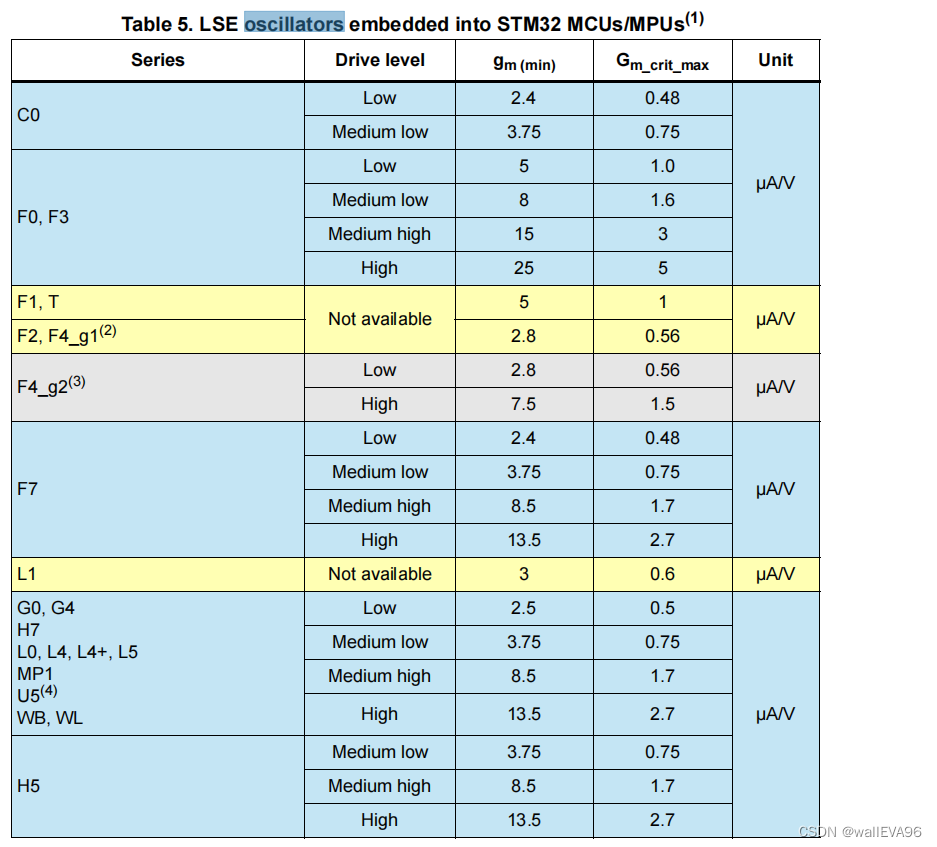

STM32中各个系列内嵌的振荡器, 其对应的参数指标:

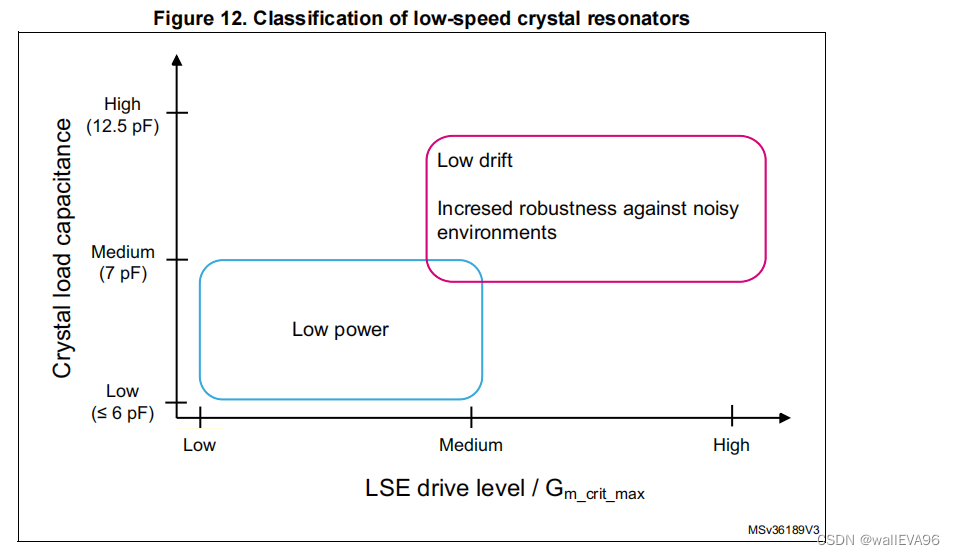

不同的驱动水平对应的不同的晶振负载图, 没有功率节约需求的话, 一般建议使用大负载晶振的, 以此来降低牵引度。

- 需要计算晶振回路中的临界跨导,

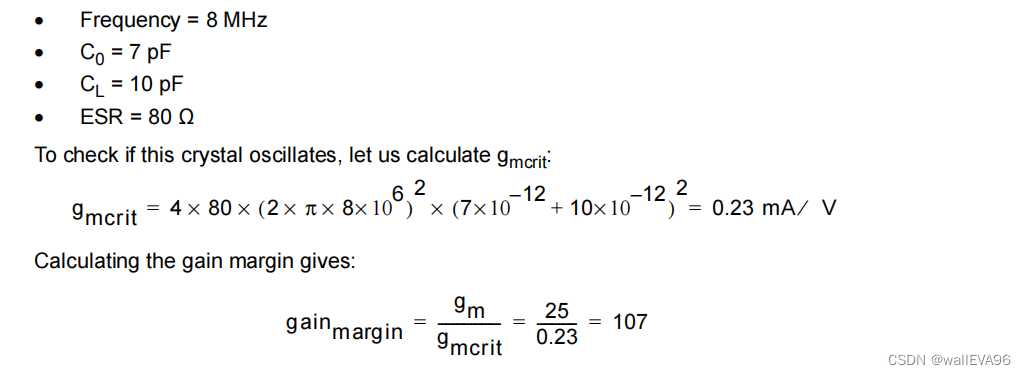

- 在st的一部分产品中,如F103,会在手册中指明芯片支持的固定的晶振跨导

g(m), 而我们需要做的就是计算晶振的临界跨导g(mcrit),然后, 计算极限增益gain = g(m)/g(mcrit), 要确保该增益大于5倍, 晶振才能够稳定运行, 计算如下:

如何使晶振的功耗更低

- 选择负载电阻更小的晶振, 搭配相对应的负载电容也更小, 整体的功耗就能降低, 但是低负载电阻的晶振的价格更贵一些。

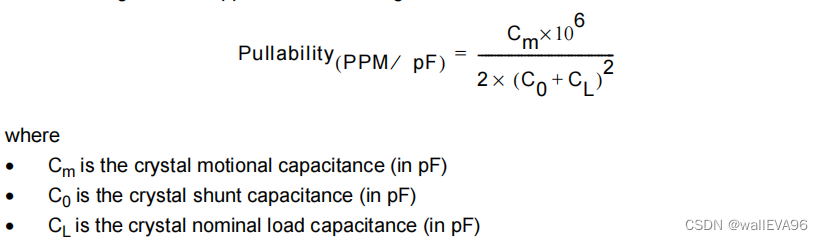

- 电容的大小同时也会影响晶振的频率精度。

如何选择一个STM32兼容的晶振

-

选择支持fundamental mode的晶振, 而不是支持overtone modes。

-

确定芯片支持的晶振跨导或者芯片的最大临界跨导。

-

计算晶振的外部负载电容。

-

计算晶振的负性阻抗以及安全系数。 有些晶振厂商会配对好, 如果配对好的话, 就可以跳过2和3步骤。

如果负性阻抗不满足条件的话, 更换ESR较小的晶振,以减小RL 或者 适当减小Ci(Cg)和增加Co(Cd),以减小RL。以下公式有待进一步考证, 来源于

High-Performance Crystal Oscillator Circuits: Theory and Application这篇论文。

-

计算激励功率,使其小于晶振的最大额定功率,避免晶振损坏。

-

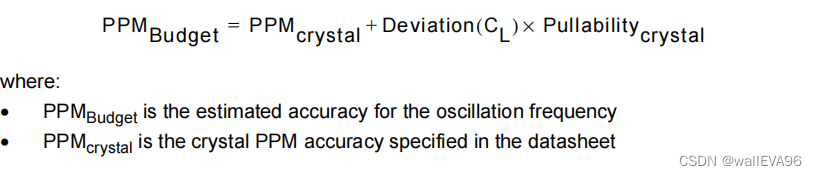

计算晶振的PPM精度范围, 具体公式如下:

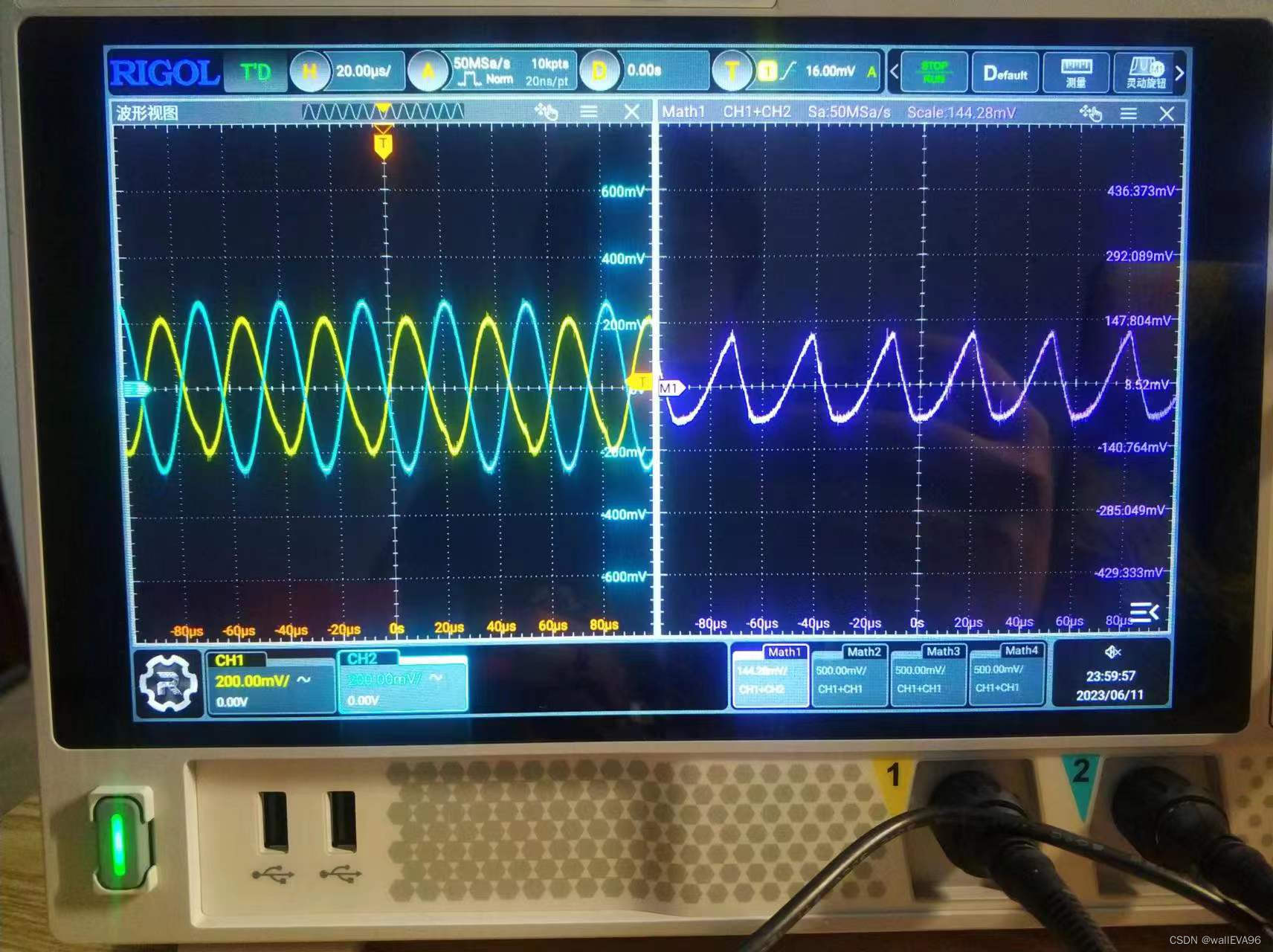

如何用示波器测量波形

无源晶振内部核心部件为石英晶片,通过电极连接至晶振管脚,石英晶片没有极性,因此晶振两端的信号一样,频率相等,波型为正弦波。如果上电实测无源晶振两端信号存在差异,如频率或波形不完全等同,属于正常现象,可归因于所测引脚可能受到内部放大电路或周边杂散电容影响所致。

由于晶振对电容负载较为敏感,示波器探头如果设置在x1档位,电容较大。因此,我们需要对示波器的探头进行配置。将探头调整到x10档位, 此时探头的电容会更小,对信号敏感的电路, 影响也较小。

- 如果测量的是晶振波形, 要将探头的耦合方式选择

交流模式。 - 将探头配置为x10档位,示波器有 x1和x10两种档位,其中x1为不衰减状态,x10为衰减10倍状态。如果选择了x10档位,示波器上的刻度值需要乘以10才能得到真实的电压值。例如,如果示波器上显示的是2V刻度,实际测量值则为20V。

- 对探头进行电容补偿, 此时需要使用电容补偿棒调节探头的补偿电容值,补偿大致如下:

如何保证芯片输出功率不会损伤晶振

驱动水平DL是在晶体中耗散的功率, 因此必须要做限制, 否则石英晶体会工作失败,因为过度的机械振动。 正常来说, 厂商会对该值进行说明, 如DT-26这个型号, 其激励功率就是1uw, 最大2uw, 如果超出这个值就会导致晶振毁坏或者老化加剧。

有两种办法可以用来计算晶振的激励功率:

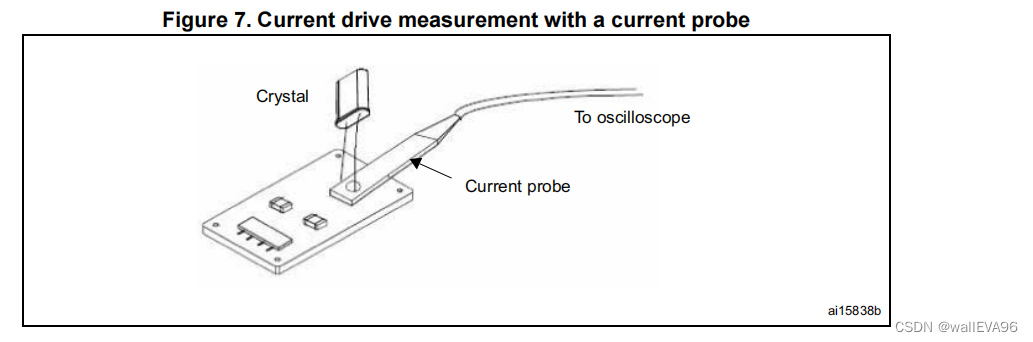

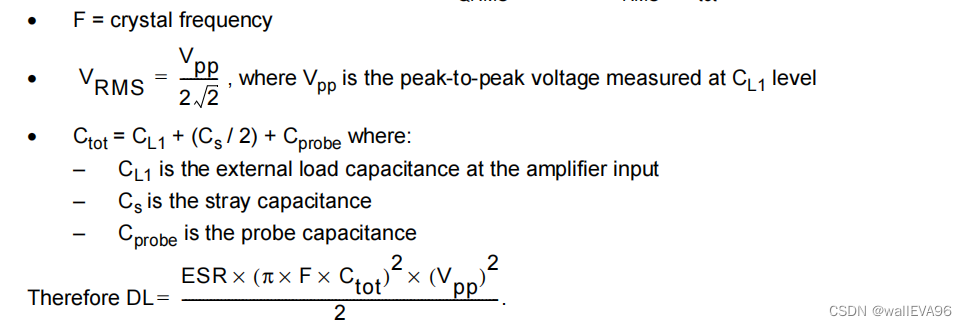

DL = ESR x (IQ)^2,IQ表示通过晶振电流的有效值, 通过示波器如下测量电流 ,如果过大的话, 则需要增加Rext电阻进行限流,测量电流的话,晶振引脚空间小,不好操作。

- 因为

IQ(RMS) = 2 π F x VRMS x Ctot, 所以,计算激励功率的办法也可以通过电压来计算,我们需要通过示波器测量晶振引脚的电压, 并获取到电压的峰峰值, 还需要知道示波器探头的电容Cprobe, 以及晶振的外部负载电容CL1, 公式如下:

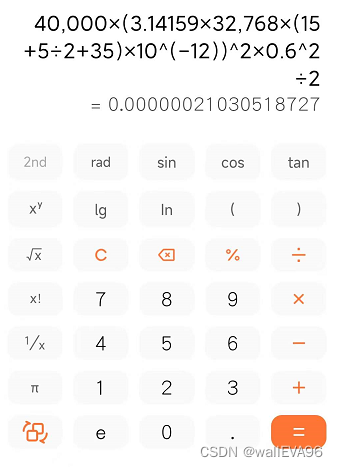

我们假设CL1为15pf,Cs为5pf,Cprobe为 10pf(补偿范围是 10pf到25pf), 假设Cprobe最差为35pf,晶振的等效电阻为40K欧姆,Vpp为0.6v, 带入上述公式可得如下, 激励功率为DL = 0.21uw, 从厂商的手册可知, DT-26的晶振的额定功率为1uw, 因此,该功率不会损伤晶振。

关于晶振PCB设计建议

- 外部杂散电容和电感要控制在一个尽可能小的范围内,从而避免晶振进入非正常工作模式或 引起起振不正常等问题。另外,振荡器电路旁边要避免有高频信号经过。

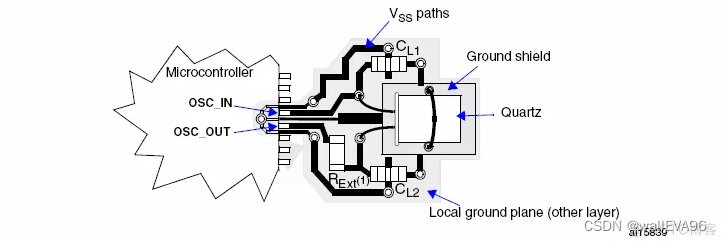

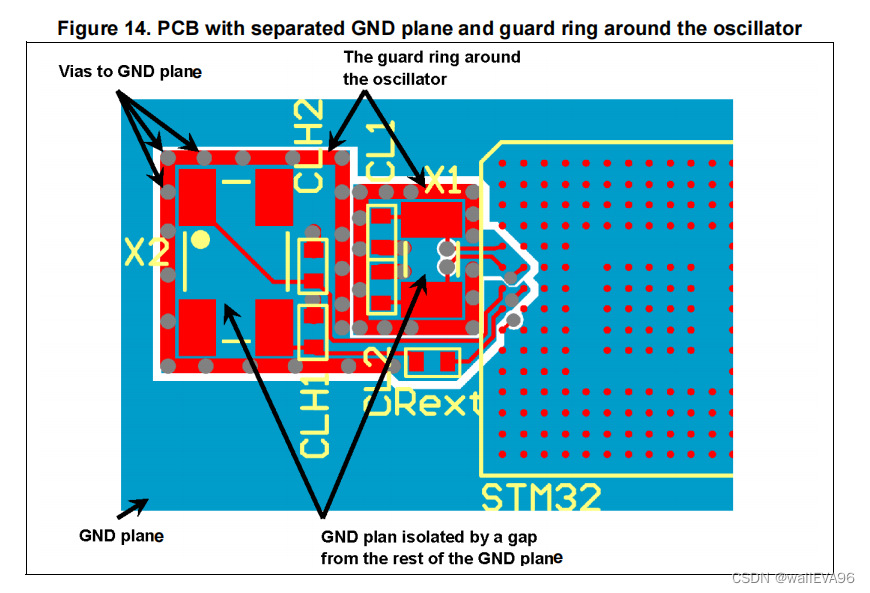

- 晶振的走线长度越短越好, 长度相等更好, 晶振的引脚尽可能靠近芯片,

- 接地平面用于信号隔离和减少噪声。例如:在晶振的保护环(译注:(Guard ring),指器件或 走线外围成一圈用于屏蔽干扰的导线环,一般要求理论上没有电流从该导线环上经过)下直 接敷地有助于将晶振和来自其他PCB层的噪声隔离开来。要注意接地平面要紧临晶振但只限 于晶振下面,而不要将此接地平面敷满整个PCB板。

- 像图7所示来布地线是一个好的作法。这种布线方法将振荡器的输入与输出隔离开来,同时 也将振荡器和临近的电路隔离开来。所有的VSS过孔不是直接连到地平面上(除晶振焊盘之 外),就是连接到终端在CL1和CL2下方的地线上。

- 在每一对VDD与VSS端口上连接去藕电容来平滑噪声。

ST芯片公司可供参考的晶振选型

st的芯片设计手册中都会提供对应的晶振型号以供用户参考。