提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

- 💡一、填空题(每空1分,共20分)

- 💡二、单项选择题(每小题2分,共20分)

- 💡三、作图题、化简题(每小题5分,共15分)

- 💡四、设计题(共30分)

- 💡五、分析题(共15分)

- 💡 一、填空题(每空1分,共20分)

- 💡 二、单项选择题(每小题2分,共20分)

- 💡三、作图题、化简题(每小题5分,共20分)

- 💡 四、设计题(每小题10分,共30分)

- 💡写在最后

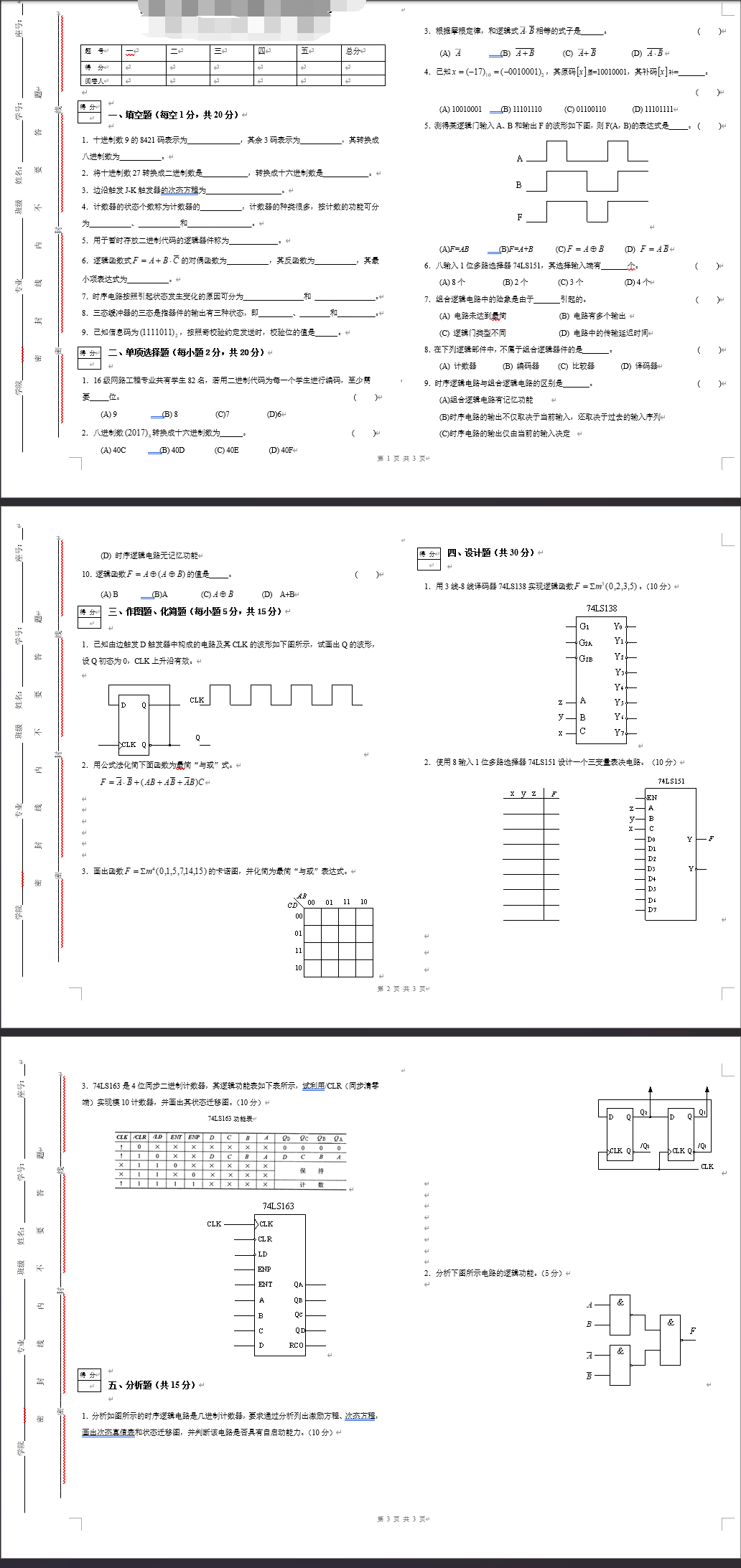

💡一、填空题(每空1分,共20分)

1.十进制数9的8421码表示为______________,其余3码表示为___________,其转换成八进制数为___________。

2.将十进制数27转换成二进制数是____________,转换成十六进制数是____________。

3.边沿触发J-K触发器的次态方程为____________________。

4.计数器的状态个数称为计数器的___________,计数器的种类很多,按计数的功能可分为___________、和______。

5.用于暂时存放二进制代码的逻辑器件称为 。

6.逻辑函数式 的对偶函数为 ,其反函数为___________,其最小项表达式为___________。

7.时序电路按照引起状态发生变化的原因可分为________________和 _____。

8.三态缓冲器的三态是指器件的输出有三种状态,即、和。

9.已知信息码为 ,按照奇校验约定发送时,校验位的值是 。

得 分

💡二、单项选择题(每小题2分,共20分)

1.16级网路工程专业共有学生82名,若用二进制代码为每一个学生进行编码,至少需

要_____位。 ( )

(A) 9 (B) 8 ©7 (D)6

2.八进制数 转换成十六进制数为______。 ( )

(A) 40C (B) 40D © 40E (D) 40F

3.根据摩根定律,和逻辑式 相等的式子是______。 ( )

(A) (B) © (D)

4.已知 ,其原码 原=10010001,其补码 补=_______。 ( )

(A) 10010001 (B) 11101110 © 01100110 (D) 11101111

5.测得某逻辑门输入A、B和输出F的波形如下图,则F(A,B)的表达式是_____。 ( )

(A)F=AB (B)F=A+B © (D)

6.八输入1位多路选择器74LS151,其选择输入端有 个。 ( )

(A) 8个 (B) 2个 © 3个 (D) 4个

7.组合逻辑电路中的险象是由于 引起的。 ( )

(A) 电路未达到最简 (B) 电路有多个输出

© 逻辑门类型不同 (D) 电路中的传输延迟时间

8.在下列逻辑部件中,不属于组合逻辑器件的是 。 ( )

(A) 计数器 (B) 编码器 © 比较器 (D) 译码器

9.时序逻辑电路与组合逻辑电路的区别是 。 ( )

(A)组合逻辑电路有记忆功能

(B)时序电路的输出不仅取决于当前输入,还取决于过去的输入序列

©时序电路的输出仅由当前的输入决定

(D) 时序逻辑电路无记忆功能

10.逻辑函数 的值是_____。 ( )

(A) B (B)A © (D) A+B

得 分

💡三、作图题、化简题(每小题5分,共15分)

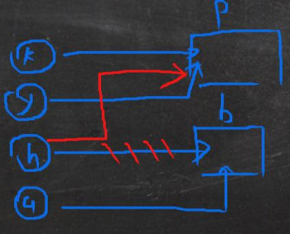

1.已知由边触发D触发器中构成的电路及其CLK的波形如下图所示,试画出Q的波形,设Q初态为0,CLK上升沿有效。

2.用公式法化简下面函数为最简“与或”式。

3.画出函数 的卡诺图,并化简为最简“与或”表达式。

得 分

💡四、设计题(共30分)

1.用3线-8线译码器74LS138实现逻辑函数 。(10分)

2.使用8输入1位多路选择器74LS151设计一个三变量表决电路。(10分)

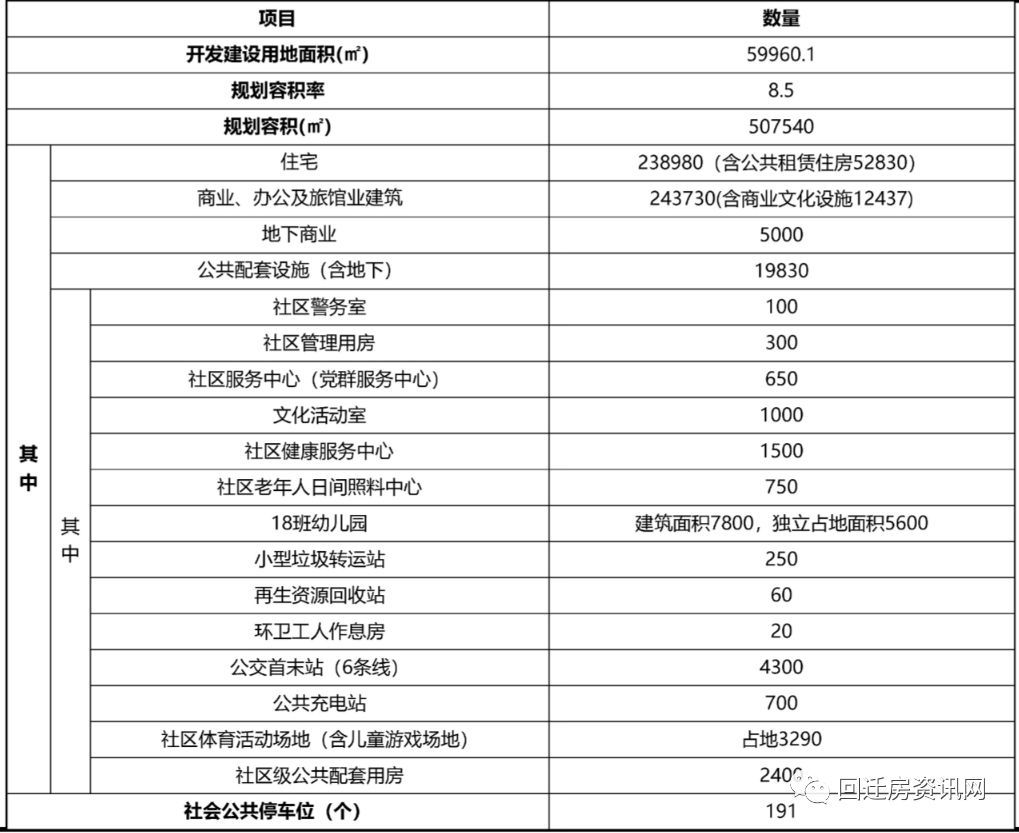

3.74LS163是4位同步二进制计数器,其逻辑功能表如下表所示,试利用/CLR(同步清零端)实现模10计数器,并画出其状态迁移图。(10分)

74LS163功能表

得 分

💡五、分析题(共15分)

1.分析如图所示的时序逻辑电路是几进制计数器,要求通过分析列出激励方程、次态方程,画出次态真值表和状态迁移图,并判断该电路是否具有自启动能力。(10分)

2.分析下图所示电路的逻辑功能。(5分)

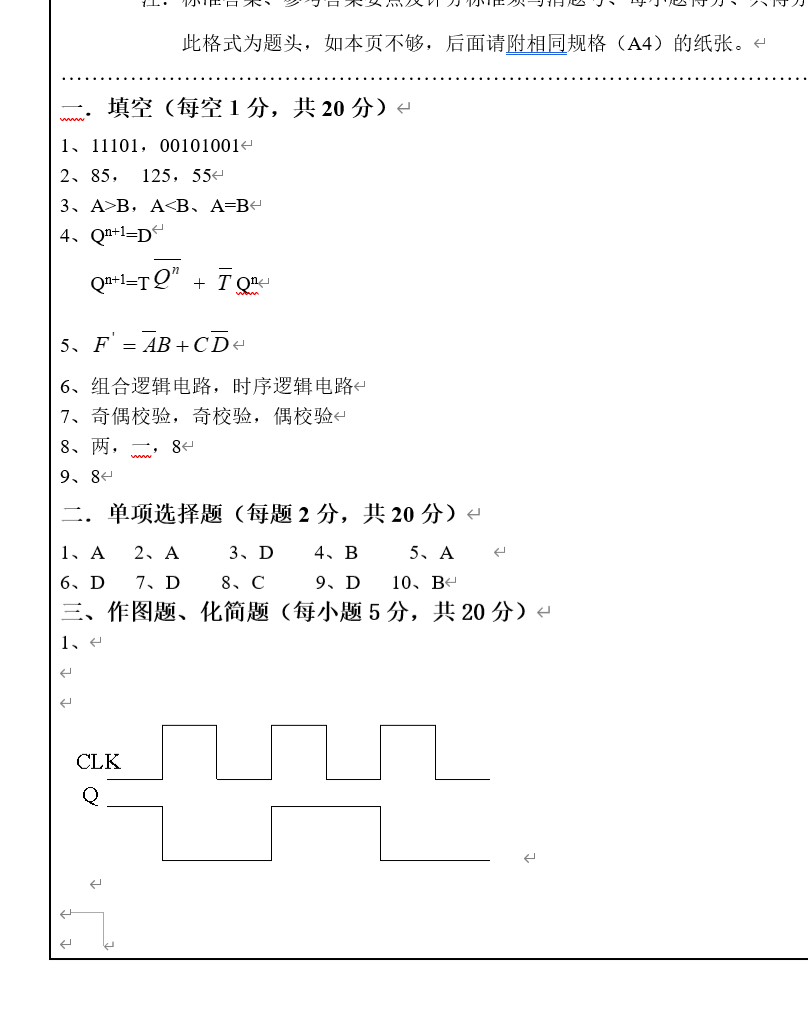

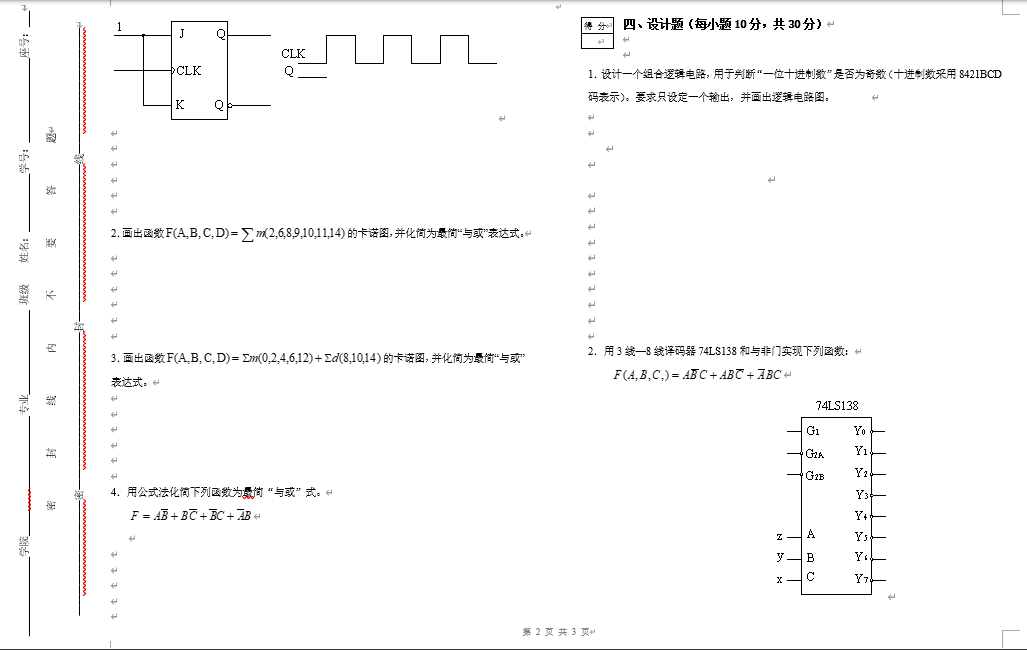

💡 一、填空题(每空1分,共20分)

1.十进制数29对应的二进制数为 ,其对应的8421BCD码为 。

2.二进制数1010101对应的十进制数为 ,八进制数为 ,十六进制数为 。

3.数据比较器的逻辑功能是对输入的的两个数据进行比较,它有 、 和 三

个输出端。

4.D触发器的特征方程为 ,T触发器的特征方程为 。

5.逻辑函数 的对偶函数 = 。

6.逻辑电路可分成两大类型:和。

7.为了检测数据传输中出现的错误,常用 方法。可以使用 校验,也可以使用 校验。

8.触发器有 个稳态,它可记录 位二进制码,存储8位二进制信息需要 个触发器。

9.八位移位寄存器,串行输入时经 个CLK脉冲后,8位二进制数码全部移入寄存器中。

得 分

💡 二、单项选择题(每小题2分,共20分)

1.下列等式成立的是_____。 ( )

(A)A⊕0=A (B)A⊙0=A © ( D)

2.下面逻辑式中,正确的是:。 ( )

(A) (B)

© ( D)

3.设 ,则它的反函数为。 ( )

(A) (B)

© ( D)

4.十六路数据分配器,其地址选择输入端为_____个。 ( )

(A)2 (B)4 ©8 ( D)16

5.在下列逻辑电路中,不是组合逻辑电路的有_____。 ( )

(A)寄存器 (B)译码器 ©全加器 ( D)编码器

6.对于十六选一数据选择器,应有 个选择输入端, 个数据输入端。 ( )

(A)8 ,3 (B)3 ,8 ©16 ,8 ( D)4 ,16

7.欲使一路数据分配到多路装置应选用带使能端的:。 ( )

(A)编码器 (B)比较器 ©选择器 ( D) 译码器

8.JK触发器在CP脉冲作用下,欲使Qn+1=0,则必须使:。 ( )

(A)J=1,K=0 (B)J=0,K=0 ©J=0,K=1 ( D)J=1,K=1

9.用n个触发器构成计数器,可得到的最大计数长度(即计数模)为_____。 ( )

(A)n (B)2n © ( D)

10.同步时序电路和异步时序电路比较,其差异在于后者_______。 ( )

(A)没有稳定状态 (B)没有统一的时钟脉冲控制

©没有触发器 ( D) 输出只与内部状态有关

得 分

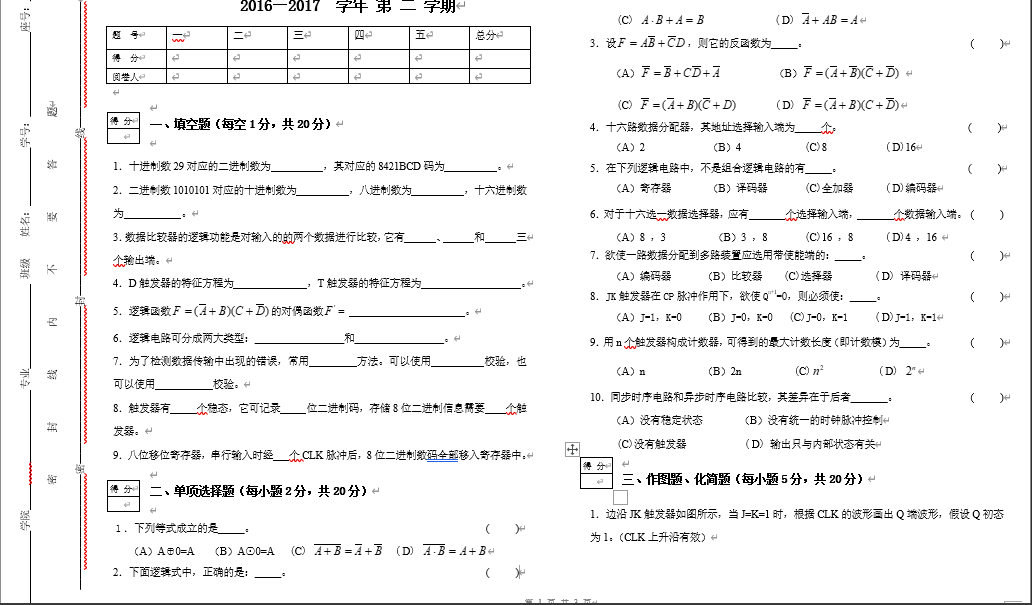

💡三、作图题、化简题(每小题5分,共20分)

1.边沿JK触发器如图所示,当J=K=1时,根据CLK的波形画出Q端波形,假设Q初态为1。(CLK上升沿有效)

2.画出函数 的卡诺图,并化简为最简“与或”表达式。

3.画出函数 的卡诺图,并化简为最简“与或”表达式。

4.用公式法化简下列函数为最简“与或”式。

得 分

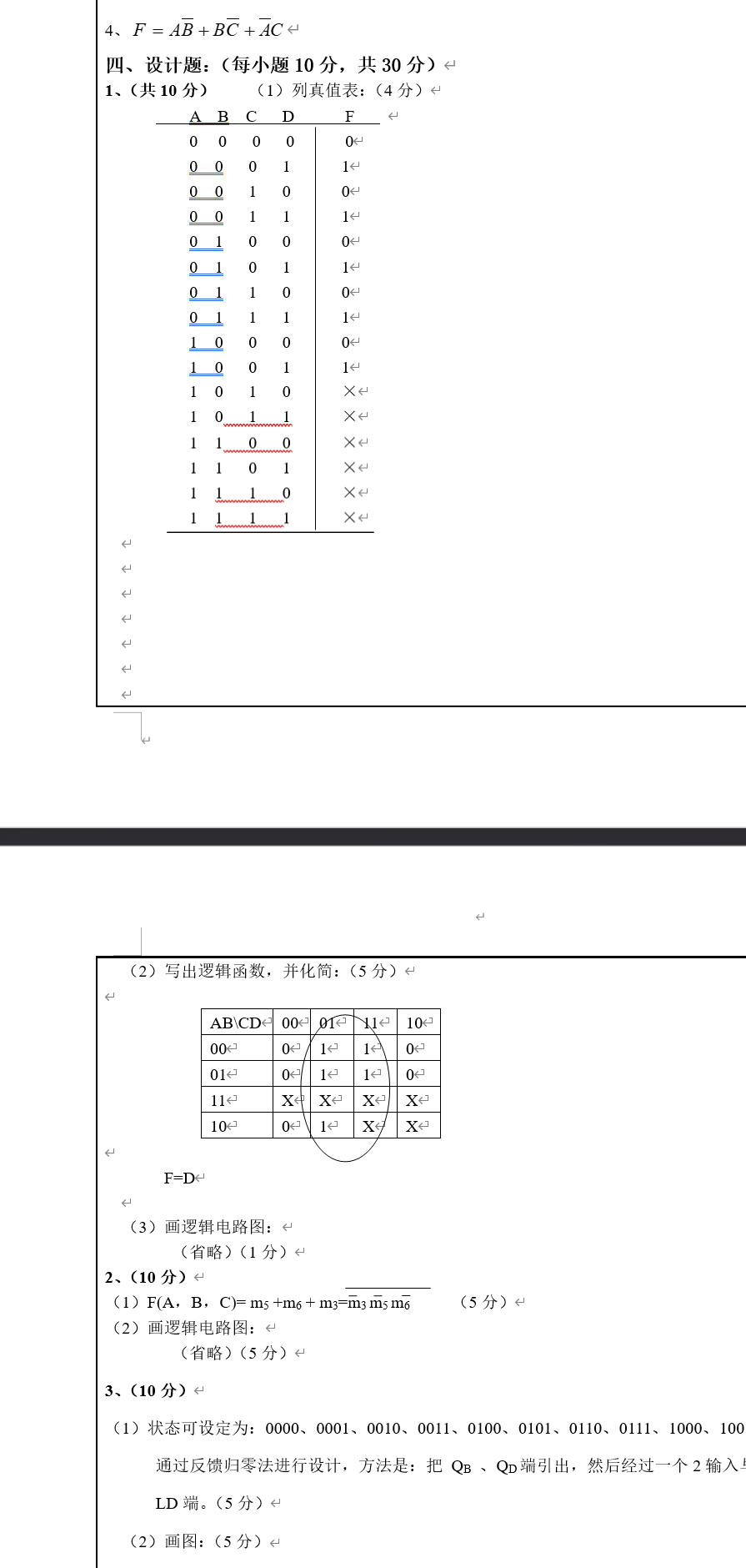

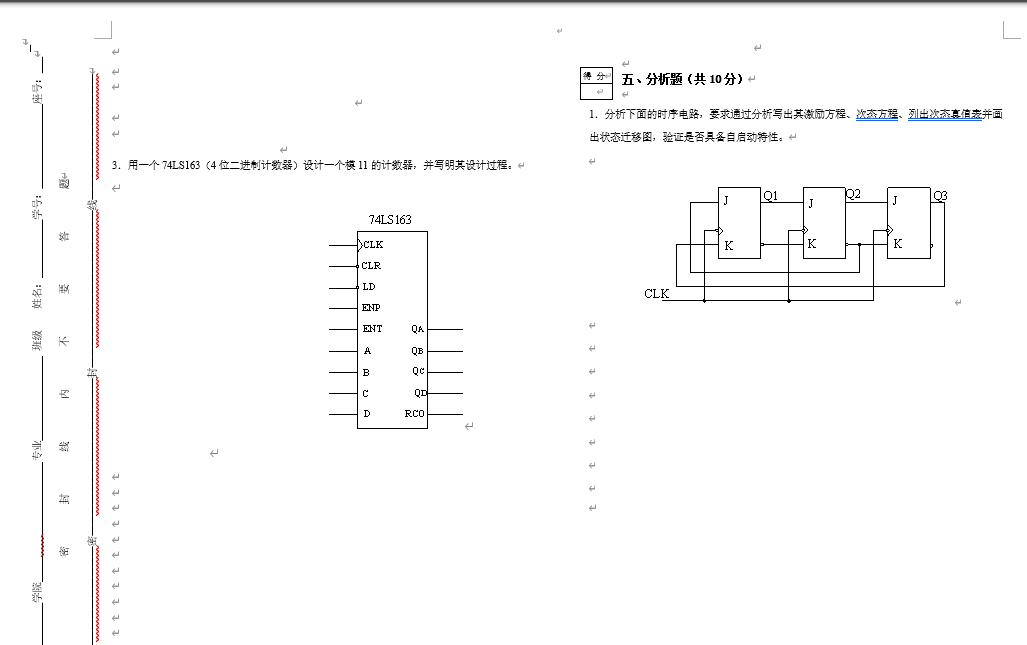

💡 四、设计题(每小题10分,共30分)

1.设计一个组合逻辑电路,用于判断“一位十进制数”是否为奇数(十进制数采用8421BCD码表示)。要求只设定一个输出,并画出逻辑电路图。

2.用3线—8线译码器74LS138和与非门实现下列函数:

3.用一个74LS163(4位二进制计数器)设计一个模11的计数器,并写明其设计过程。

得 分

五、分析题(共10分)

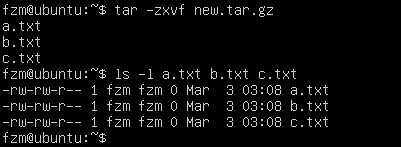

1.分析下面的时序电路,要求通过分析写出其激励方程、次态方程、列出次态真值表并画出状态迁移图,验证是否具备自启动特性。

答案可以私信我要哦

💡写在最后

数字逻辑,我希望我能考到八十分保佑我。