在CPU中跟踪指令后继地址的寄存器是___。

A 主存地址寄存器

B 程序计数器 (我的答案)

C 指令寄存器

D 状态条件寄存器

下面描述的RISC机器基本概念中,正确的表述是 __。

A. RISC机器不一定是流水CPU.

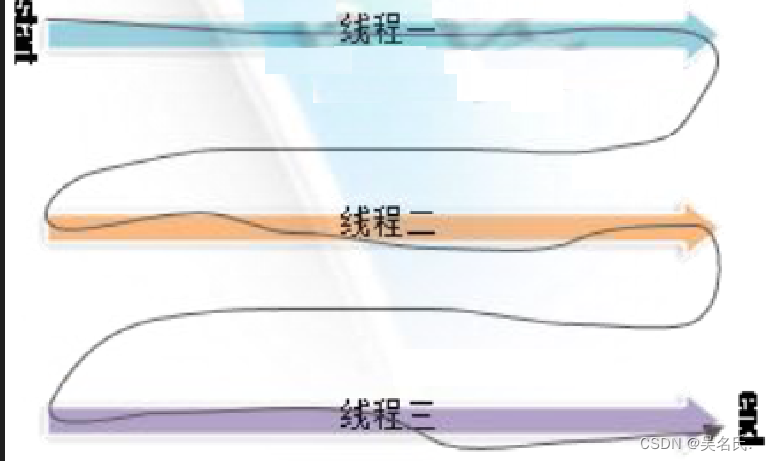

B. RISC机器一定是流水CPU. (我的答案)

C. RISC机器有复杂的指令系统.

D. CPU配备很少的通用寄存器.

目前现代CPU内主要含有 ___。

A. 运算器

B. 控制器

C. 运算器,控制器和cache (我的答案)

D. 运算器,控制器和主存储器

某计算机的控制器采用微程序控制器方式,微指令中的操作控制字段采用直接表示法,共有33个微命令,这33个微命令分为5个互斥的类,每类中分别包含7,3,12,5和6个微命令,若采用编码表示则需要操作控制字段有___。

A. 5位

B. 6位

C. 15位 (我的答案)

D. 33位

下列给出的指令系统中,有利于实现指令流水线的是___。

①指令格式规整且长度一致②指令和数据按照边界对齐存放③只有Load/Store 指令才能对操作数进行存储器访问

A.仅①和②

B. 仅②、③

C.仅①和③

D.①,② ,③ (我的答案)

某计算机字长32位,在执行指令的顺序寻址时,PC为32位,PC增量值为___。

A.1

B.2

C.4 (我的答案)

D.8

存储器是计算机系统的记忆设备,它主要用来____。

A. 存放数据 B. 存放程序 C. 存放数据和程序 D. 存放微程序

某计算机存储器按照字节编址,主存地址空间大小为64MB,用4M*8的RAM扩展成为32MB的主存储器,请问存储器地址寄存器(AR或MAR)是_____

A. 22位

B. 23位

C. 25位

D.26位 (我的答案)

一个容量为4K×16位的存储器,其地址线和数据线的总和是_

A 20

B. 24

C. 28 (我的答案)

D. 30

一个具有24位地址和8位字长的存储器,若存储器由4M×1位的RAM芯片组成,需要片_。

A. 48

B. 24

C. 8

D. 32 (我的答案)

需要可以用作Cache的存储器芯片是 _。

A RAM

B DDR

C SRAM (我的答案)

D.SDRM

假设主存按照字节编址,cache共有64行,采用直接映射方式,主存块的大小为32字节,所有编号都从0开始,问2593号单元所在的主存块与Cache对应行(块)是:_

A 1

B 17 (我的答案)

C 34

D 63

以下叙述中,错误的是 _

A TLB就是快表,即转换后援缓冲器

B快表中存放着当前进程中常用页表项

C 快表命中时,在L1 cache 中一定会命中 (我的答案)

D 快表也是一种页表项的高速缓存,一定在CPU中

假设某系统总线在一个总线周期中并行传输4字节信息,一个总线周期占用2个时钟周期,总线时钟频率为10MHz,则总线带宽约为 ______ 。

A.10 MB/s

B.20 MB/s (我的答案)

C.40 MB/s

D.80 MB/s

假设计算机系统中软盘以中断方式与CPU进行数据交换,主频为50MHz,传输单位为16位,软盘的数据传输率为50KB/s。若每次数据传输的开销(包括中断响应和中断处理)为100个时钟周期,则软盘工作时CPU用于软盘数据传输的时间占整个CPU时间的百 分比是______。

A.0%

B.5% (我的答案)

C.1.5%

D.15%

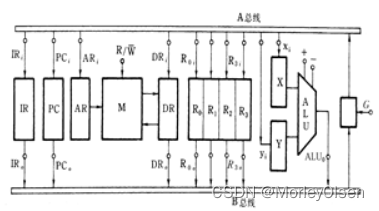

1.根据下面双总线结构模型计算机的数据通路,(1)写出指令“SUB R1,R3”指令周期流程图(2)设计水平微指令格式中的操作控制字段。

已知,“SUB R1,R3”此指令功能为R3-R1®R1. M为主存,DR为数据缓冲器,IR指令寄存器,PC程序计数器,AR为地址寄存器,X,Y为暂存寄存器,与ALU直接相连。ALU完成加或减操作由+、-信号 控制,通路上每个部件都有控制信号。

2 (1)某直接映射的高速缓存为128B, 每块(行)为4个字,即4*32位(16B),主存容量4096B,写出缓存地址和主存地址构成。

(2)什么是程序的局部性原理?

3 某外传送信息的最高频率为40K次/秒,而相应的中断处理程序的执行时间为40ms,问该外设是否可以采用中断方式工作?为什么?