一、什么是 cache,有什么用

cache是一种内存,叫高速缓存。

从容量来说:CPU < 寄存器 < cache < DDR

从速度来说:CPU > 寄存器 > cache > DDR

cache 的存在,是因为寄存器和 ddr 之间速度差异太大,ddr 的速度远不能满足寄存器的需要(不能满足 cpu 的需要,所以没有 cache 会拉低整个系统的整体速度)。

整个系统中 CPU 的供应链由:寄存器 + cache + DDR + 硬盘/flash 四阶组成,这是综合考虑了性能、成本后得到的妥协的结果。

210内部有 32KB icache和 32kb dcache。icache 是用来缓存指令的;dcache是用来缓存数据的。

cache 的意义:指令平时是放在 硬盘/flash 中的,运行时读取到 DDR 中,再从 DDR 中读给寄存器,再由寄存器送给 cpu 。但是 DDR 的速度和寄存器(代表的就是 CPU)相差太大,如果 CPU 运行完一句再去 DDR 读取下一句,那么 CPU 的速度完全就被 DDR 给拖慢了。解决方案就是 icache。

icache 工作时,会把我们 CPU 正在运行的指令的旁边几句指令事先给读取到 icache 中( CPU 设计有一个基本原理:代码执行时,下一句执行当前一句代码旁边代码的可能性要大很多)。当下一句 CPU 要指令时,cache 首先检查自己事先准备的缓存指令中有没这句,如果有就直接拿给 CPU,如果没有则需要从 DDR 中重新去读取拿给 CPU,并同时做一系列的动作:清缓存、重新缓存。

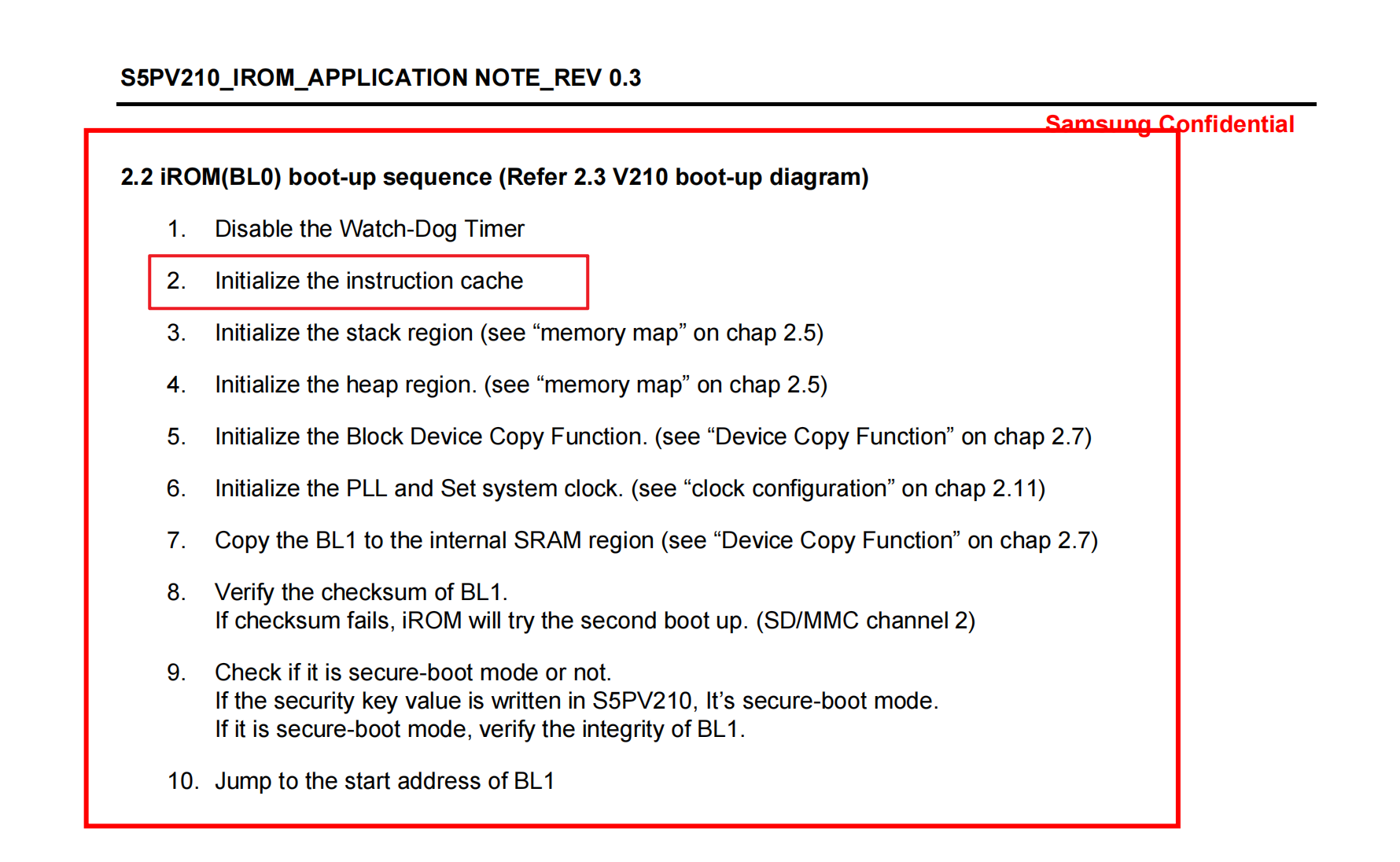

二、iROM 中BL0 对 cache的操作

首先,icache 的一切动作都是自动的,不需人为干预。我们所需要做的就是打开/关闭 icache。

其次,在 210 的 iROM 中 BL0 已经打开了 icache。所以之前看到的现象都是 icache 打开时的现象。

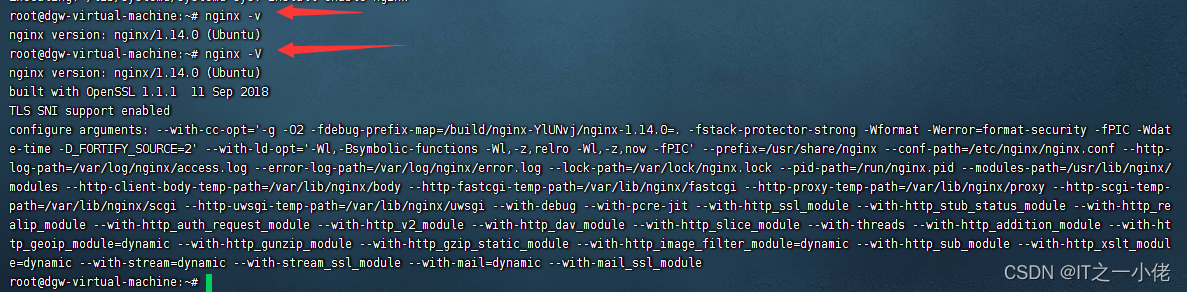

三、汇编代码读写 cp15 以开关 icache

mrc p15,0,r0,c1,c0,0; // 读出cp15的c1到r0中

bic r0, r0, #(1<<12) // bit12 置0 关icache

orr r0, r0, #(1<<12) // bit12 置1 开icache

mcr p15,0,r0,c1,c0,0;

实验验证

我们来看三种情况下的实验现象:

1 直接使用 BL0 中对 icache 的操作

2 关 icache

3 开 icache

实验结果分析:

结论1:irom 中确实是打开了 icache 的。

结论2:icache 关闭确实比 icache 打开时 led 闪烁变慢,说明指令执行速度变慢。

源自朱有鹏老师.

![[附源码]计算机毕业设计基于springboot的小区宠物管理系统](https://img-blog.csdnimg.cn/5fd465a2ba824d229b3123c84c3aa17d.png)