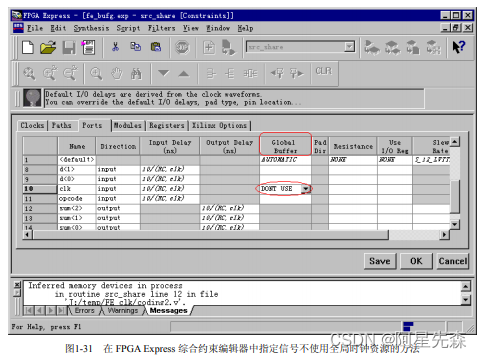

在FPGA Express/FPGA Compiler II中,用鼠标右键单击编译后的芯片图标, 在弹出的命令对话框中选择“Edit Constraints”命令编辑综合约束文件(扩展 名为CTL),选择端口(Ports)选项卡,指定所需信号的全局时钟域为 “DONT USE”。图22所示为在FPGA Express综合约束编辑器中指定信号不 使用全局时钟资源的方法。

也可以在FPGA Express/FPGA Compiler IⅡ综合约束文件(扩展名为CTL)中 直接使用“port clk global_buffer "DONT USE";”命令指定输入端口信号 “clk”不使用全局时钟资源。

Xilinx Virtex-ll和Virtex-ll Pro器件族生成DCM的方法

对于Xilinx Virtex-II和Virtex-II Pro器件族,除了按照上面介绍的 DLL或 DCM的使用方法,用代码或者原理图调用DLL.或DCM外,还可以使用ISE 5.1 以及其后版本附加的辅助设计工具—Architecture Wizard(设计结构向 导)完成 DCM的生成。Architecture Wizard的使用非常简单,不论从界面风 格还是使用方法上都与Core Generator十分相似.图23-27到简单的示例了 DCM模块的生成方法:

如图23所示,选择器件族为Virtex-II或Virtex-II Pro.