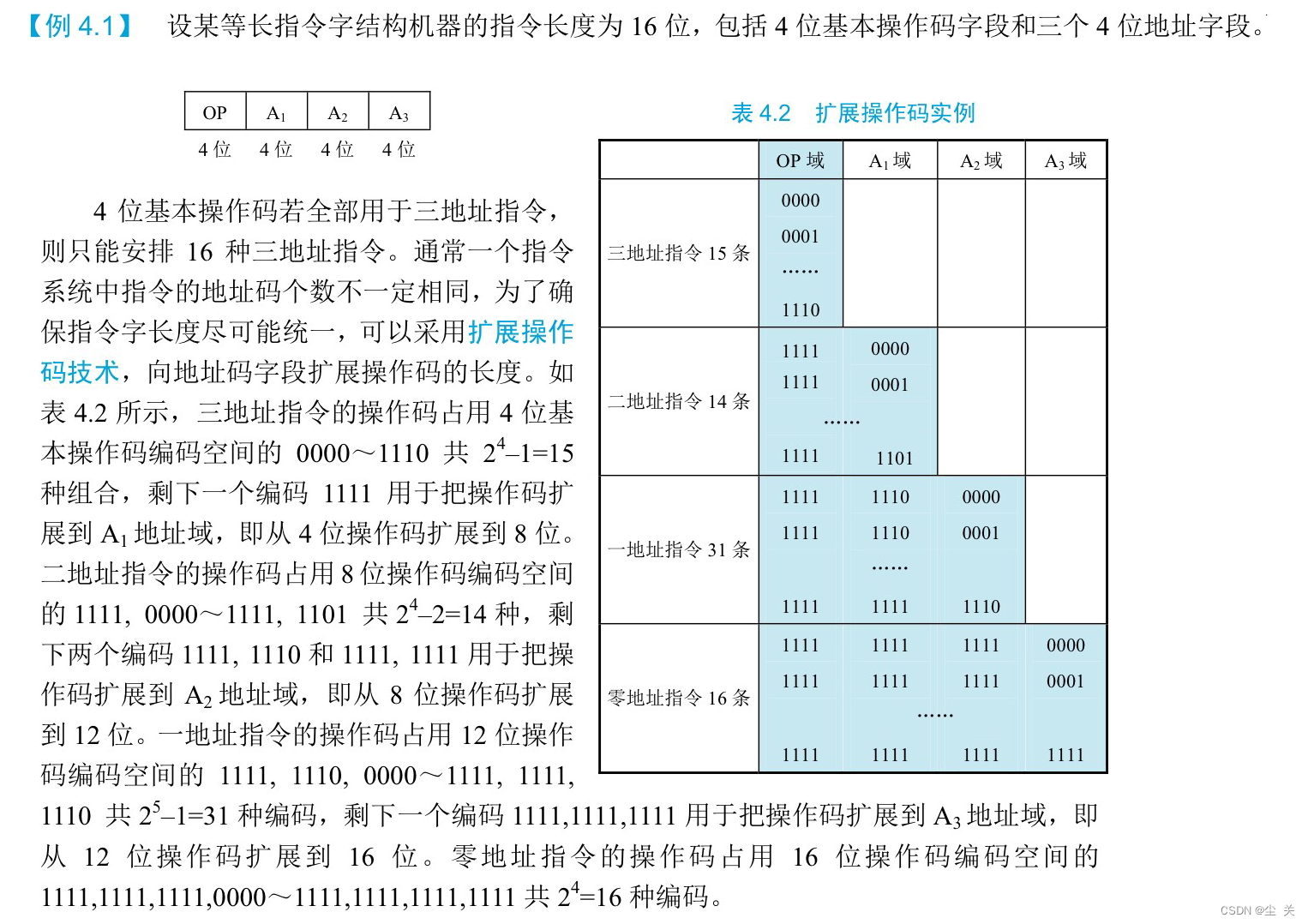

(一)课内例题

4.1

4.2

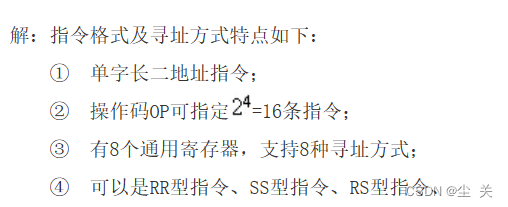

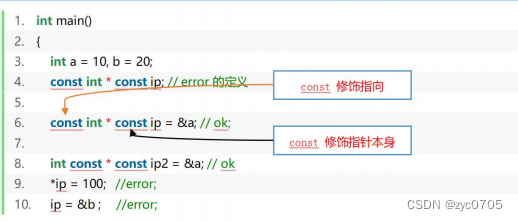

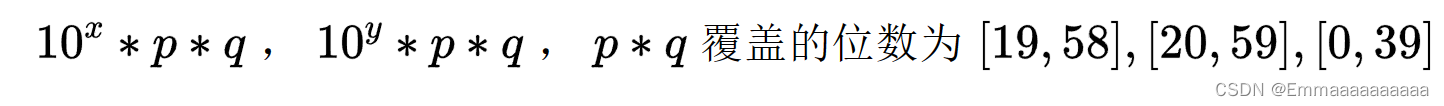

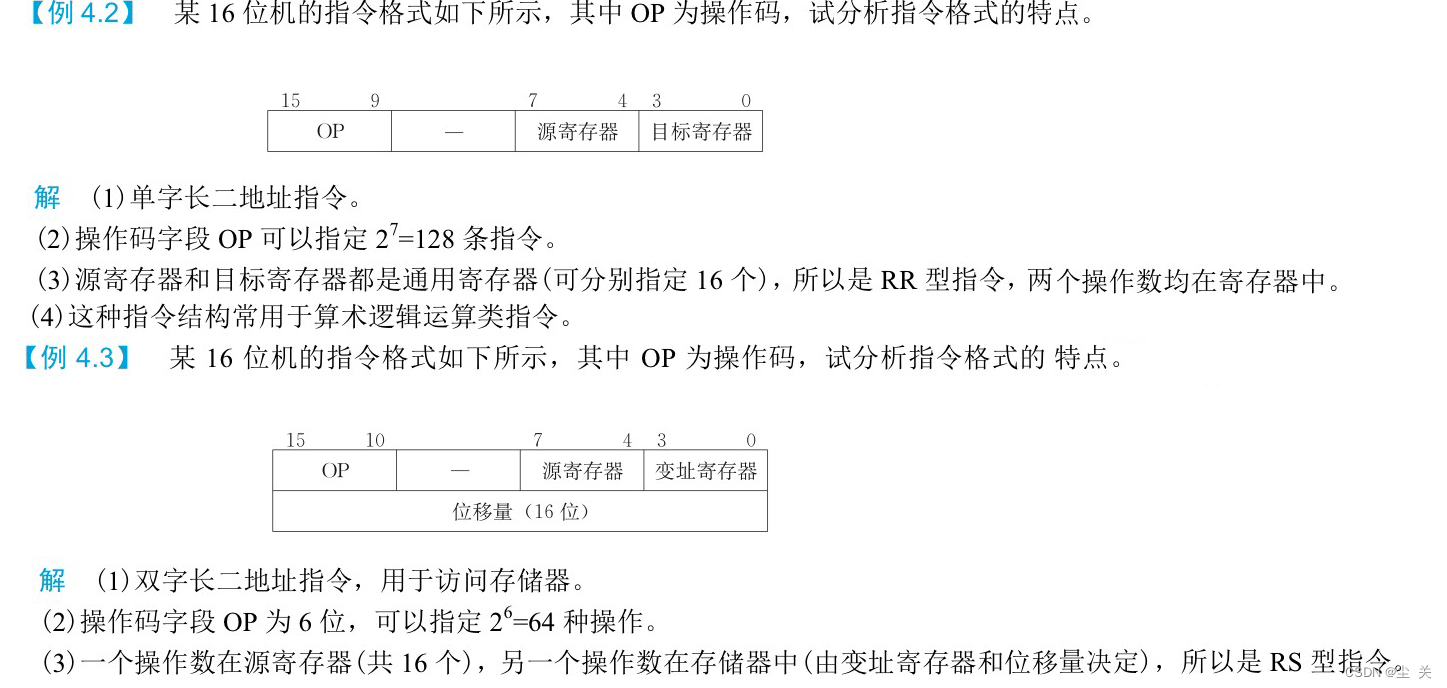

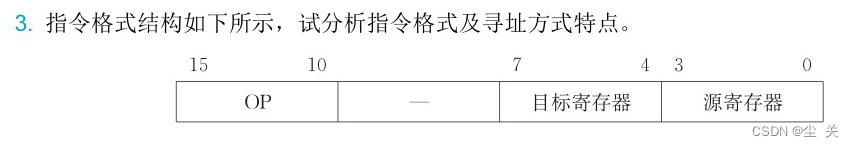

具体分析,4.2 中, 因为只有一行:单字长 二地址:源寄存器、目标寄存器

操作码看OP(15-9+1)

然后按操作数的物理位置来区别RR型,RS型()

常见寄存器:

- EAX:(针对操作数和结果数据的)累加器 ,返回函数结果

- EBX:(DS段中的数据指针)基址寄存器

- ECX:(字符串和循环操作数)计数器

- EDX:(I/O指针)数据寄存器

- EBP:(SS段中栈内数据指针)扩展基址指针寄存器

- ESI:(字符串操作源指针)源变址寄存器

- EDI:(字符串操作目标指针)目的变址寄存器

- ESP:(SS段中栈指针)栈指针寄存器

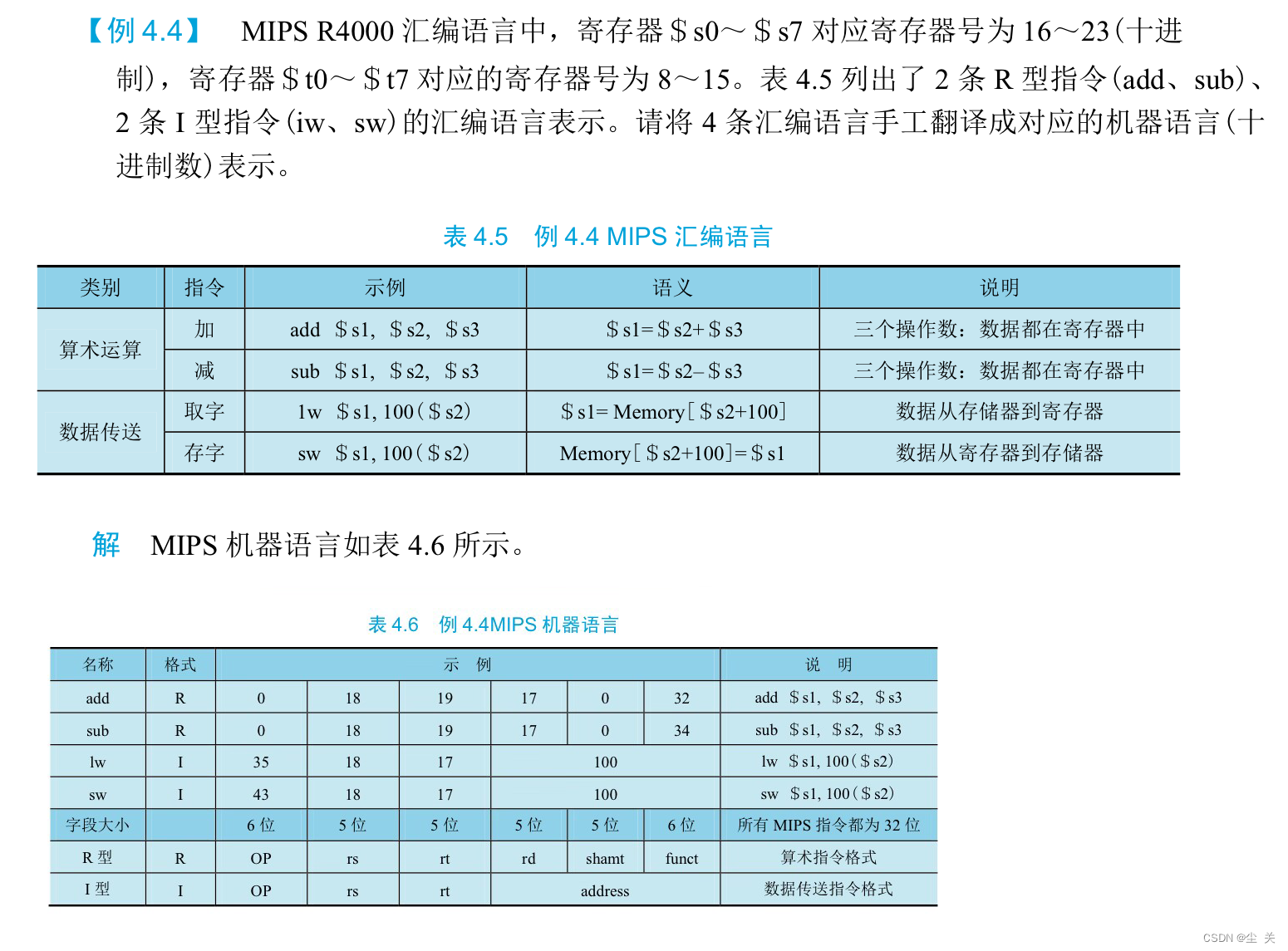

4.4

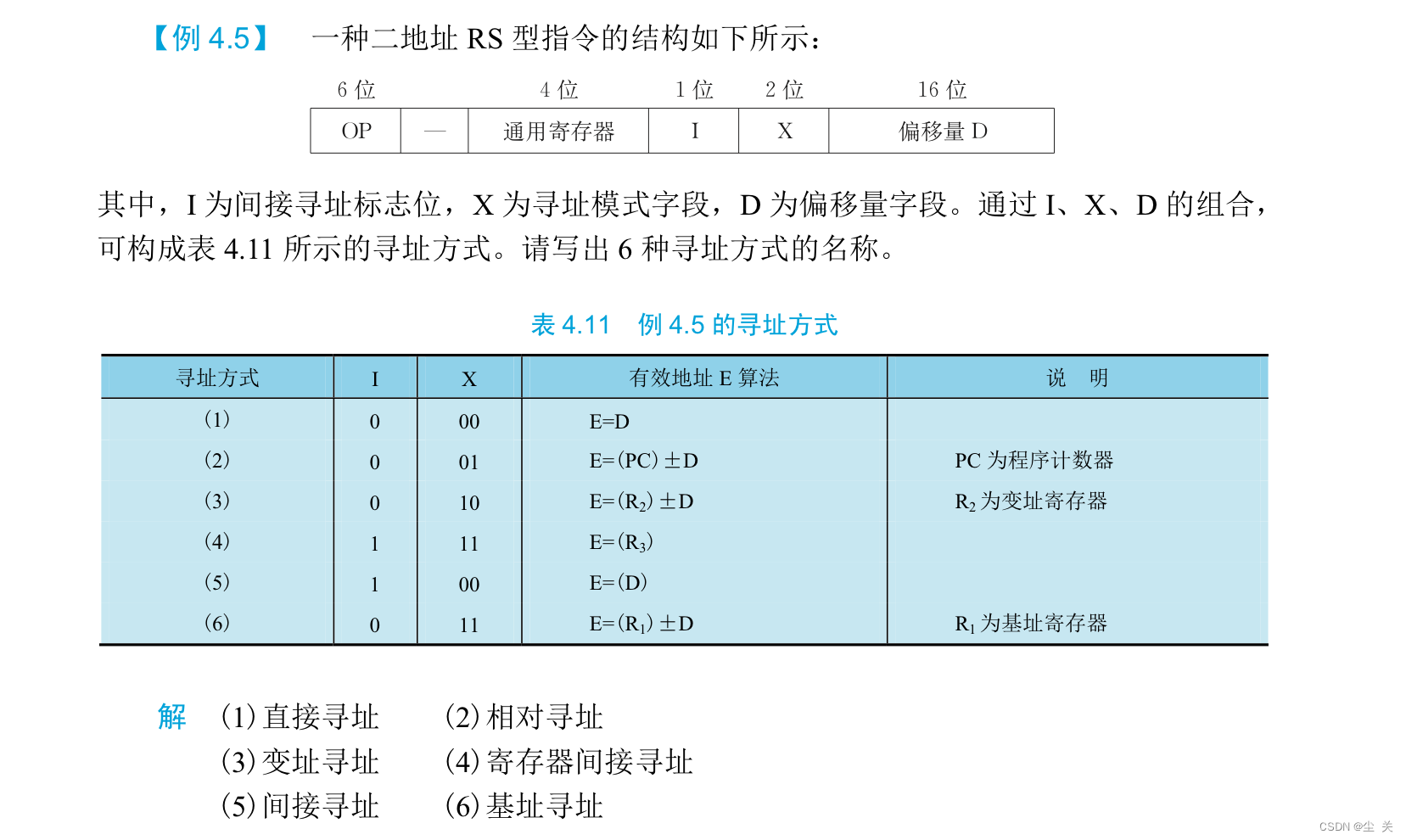

4.5

提示:

拓展:

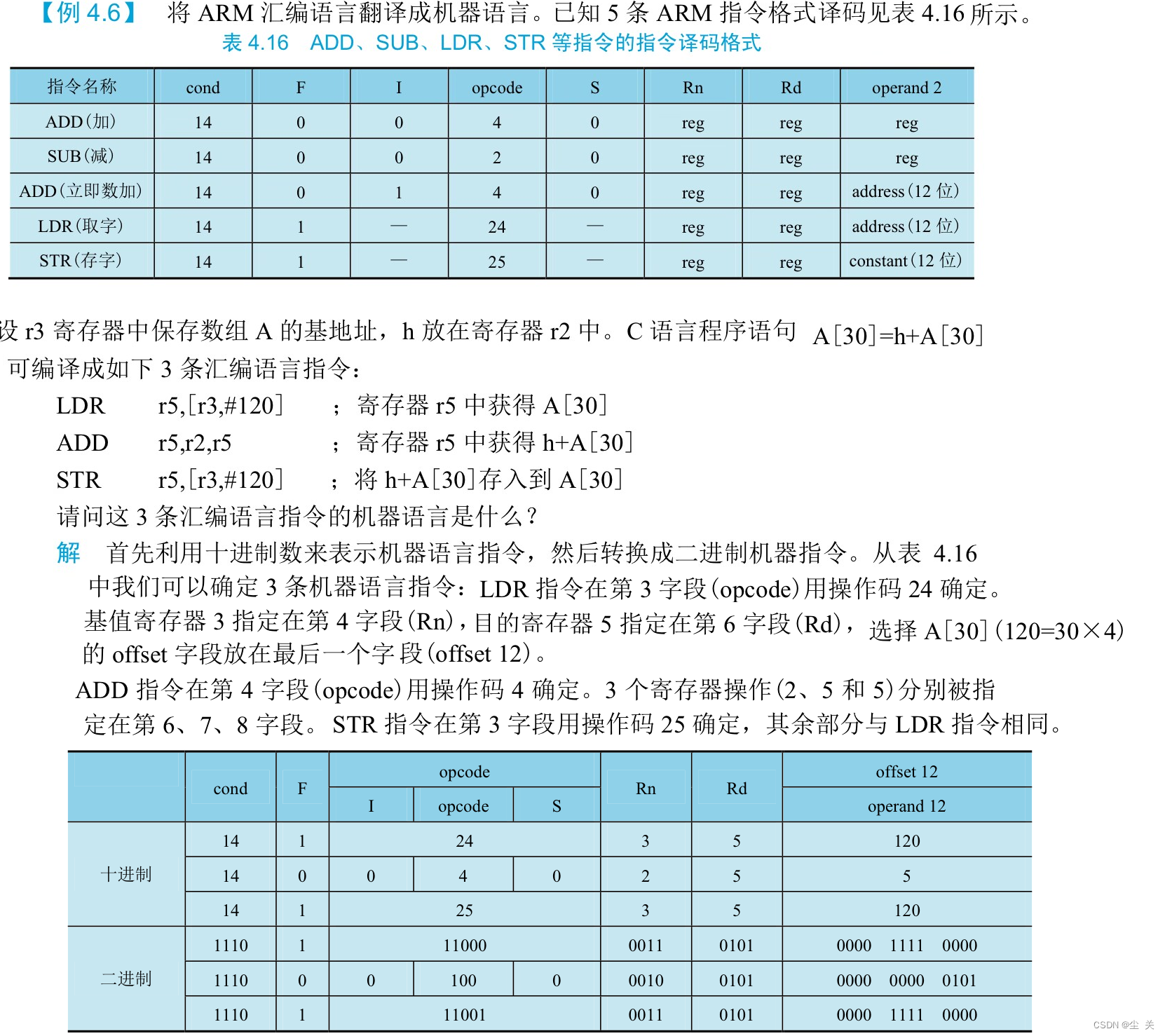

4.6

(二)课后习题

1.ASCII码是7位,如果设计主存单元字长为 32位,指令字长为12位,是否合理?为什么?

答:

版本1:

指令字长设计为12位不是很合理,主存单元字长为32位,一个存储单元可存放4个ASCII码,余下4位可作为ASCII码的校验位(某个ASCII码带一位校验位),这样设计比较合理。但是,设计指令字长为12位就不合理了,12位的指令码存放在字长为32位的主存单元中,造成19位不能用而浪费存储空间。

版本2:

答:不合理。指令最好半字长或单字长,设 16位比较合适。一个字符的 ASCII是7位,如果设计主存单元字长为32位,则一个单元可以放四个字符,这是可以的,只是在存取单个字符时,要多花些时间而已,不过,一条指令至少占一 个单元,但只占一个单元的12位,而另20位就浪费了,这样看来就不合理,因为通常单字长指令很多,浪费也就很大了。

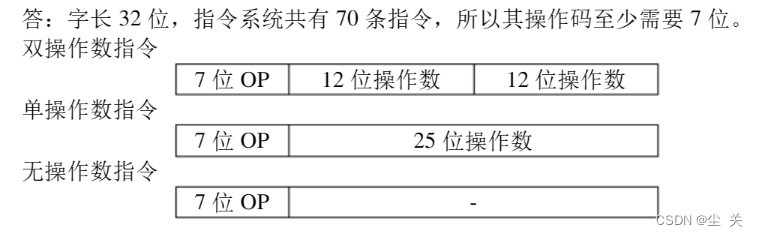

2.假设某计算机指令长度为32位,具有双操作数、单操作数、无操作数三类指令形式,指令系统共70条指令,请设计满足要求的指令格式。

答:

3. 指令格式如下所示,试分析指令格式及寻址方式特点。

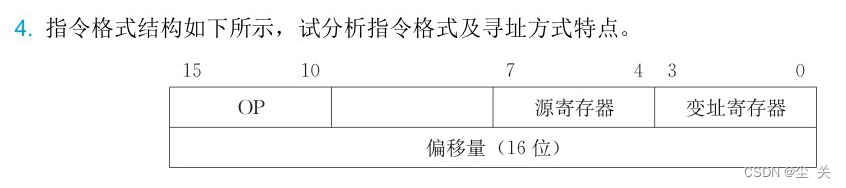

答:

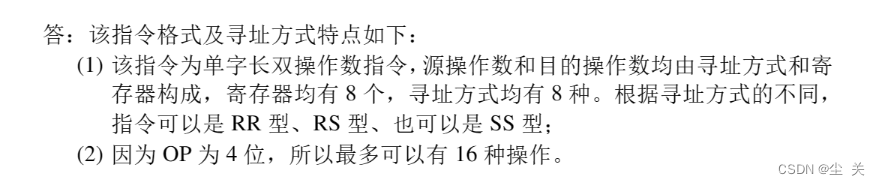

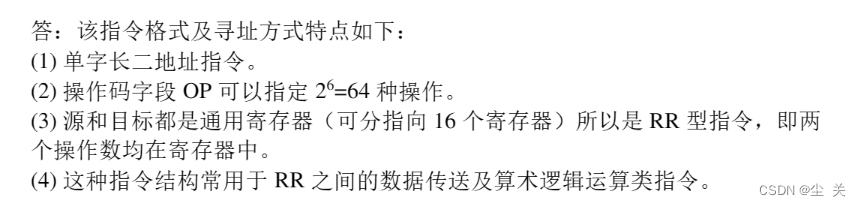

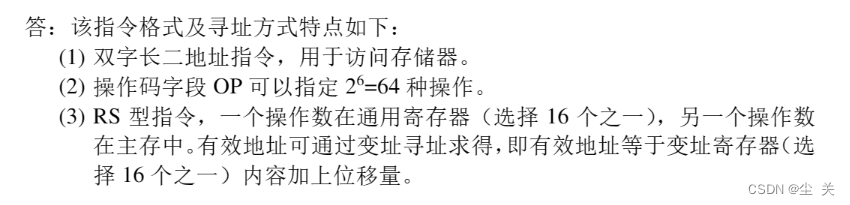

4. 指令格式如下所示,试分析指令格式及寻址方式特点。

答:

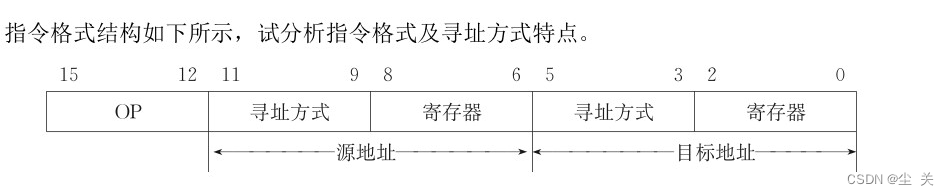

5.指令格式如下所示,试分析指令格式及寻址方式特点。

答:有两种答案,更倾向于第一版:

具体分析, 因为只有一行:单字长 二地址:源地址、目标地址

操作码看OP(15-12+1) ;寄存器(8-6+1) =3;或者(2-0+1)=3,寻址方式不定,所以操作数的物理位置也未可知。

然后按操作数的物理位置来区别RR型,RS型 ,SS型

第二版可参考:

6.一种单地址指令格式如下所示,其中I为间接特征,X为寻址模式,D为形式地址。I,X,D组成该指令的操作数有效地址E。设R为变址寄存器,R1 为基值寄存器,PC为程序计数器,请在下表中第一列位置填入适当的寻址方式名称。

答:①直接寻址 ②相对寻址 ③变址寻址 ④基址寻址 ⑤间接寻址 ⑥先基址后间接寻址

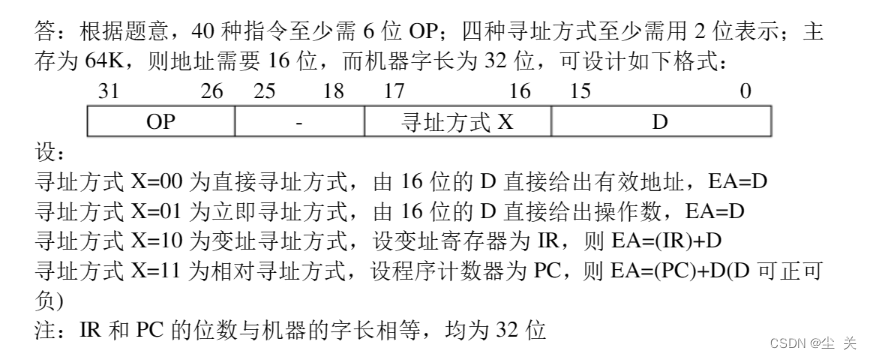

7.某计算机字长为32位,主存容量为64KB,采用单字长单地址指令,共有40 条指令。试采用直接、立即、变址、相对四种寻址方式设计指令格式。

答: 分析:主存容量为64KB,说明地址需要占16位(6+10),计算机字长为32位,IR的位数也应为32位。采用单字长单地址指令:一行+单地址;共有40 条指令:说明OP至少大于6;采用直接、立即、变址、相对四种寻址方式说明寻址方式至少需要2位表示;

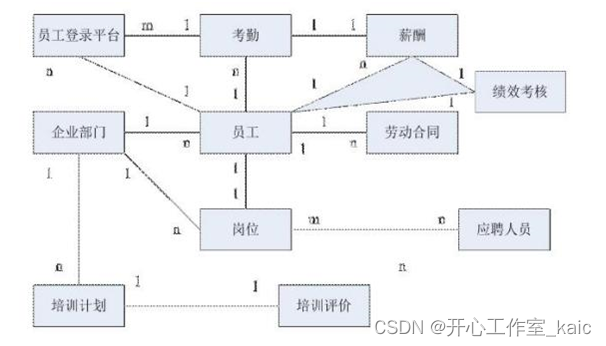

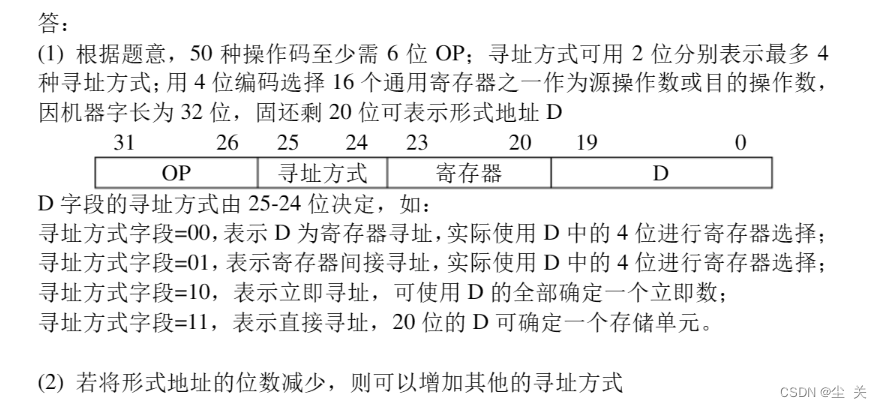

8.某机字长为32位,主存容量为1MB,单字长指令,有50种操作码,采用寄存器寻址、寄存器间接寻址、立即、直接等寻址方式。CPU中有PC、IR、AR、DR和16个通用寄存器。问:

(1)指令格式如何安排?

(2)能否增加其他寻址方式?

答:

12.根据操作数所在的位置,指出其寻址方式的名称。

1)操作数在寄存器中

2)操作数的地址在寄存器中。

3)操作数在指令中

4)操作数的地址在指令中

5)操作数地址为某一寄存器容与位移量之和(寄存器分别为基址寄存器、变址寄存器和程序计数器)

6)操作数地址的地址在指令中

7)操作数为栈顶元素

答: 1)寄存器寻址 2)寄存器间接寻址 3)立即寻址 4)间接寻址 5) 分别为基址寻址、变址寻址和相对寻址 6)存储器间接寻址 7)堆栈寻址

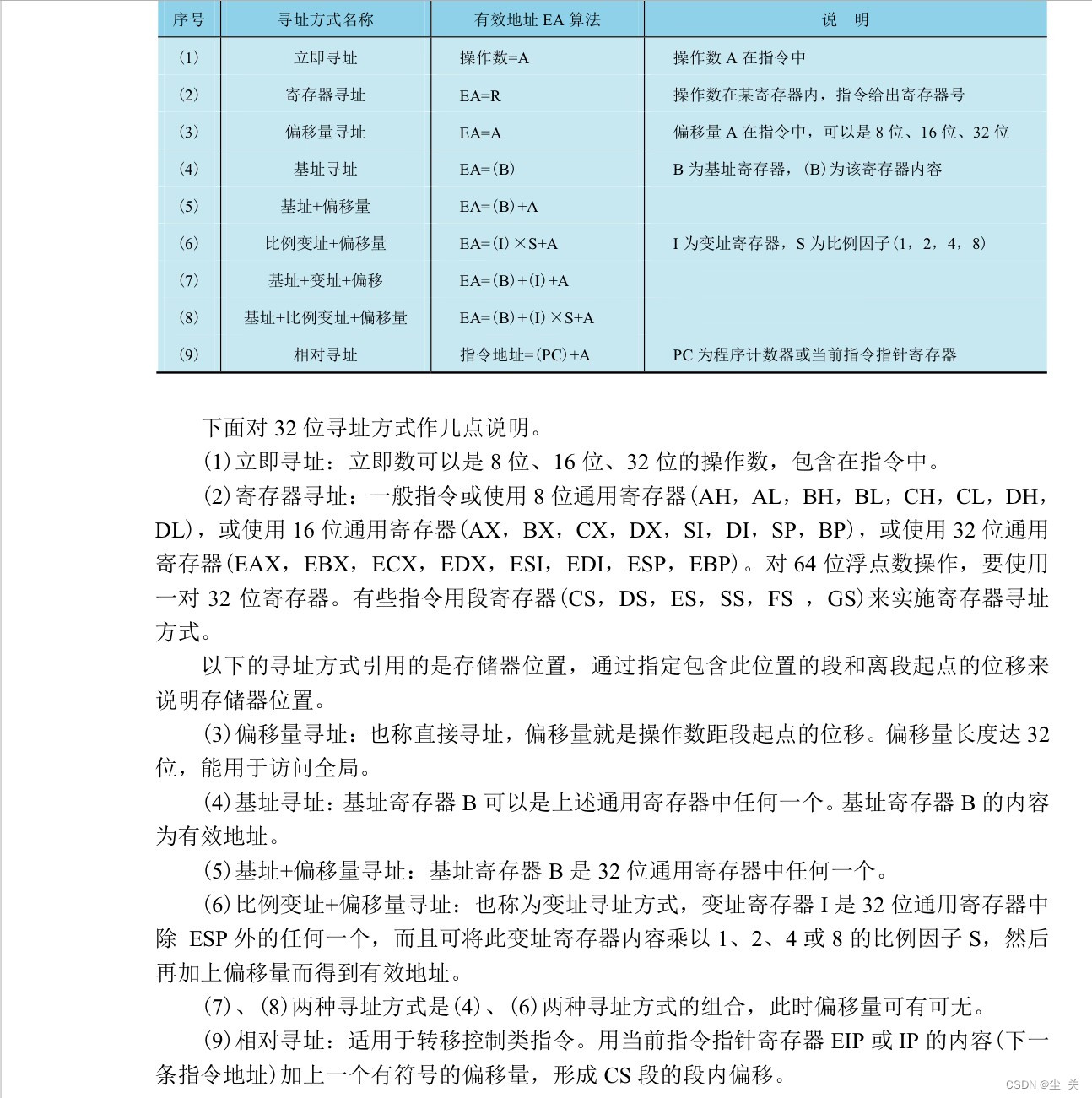

拓展:

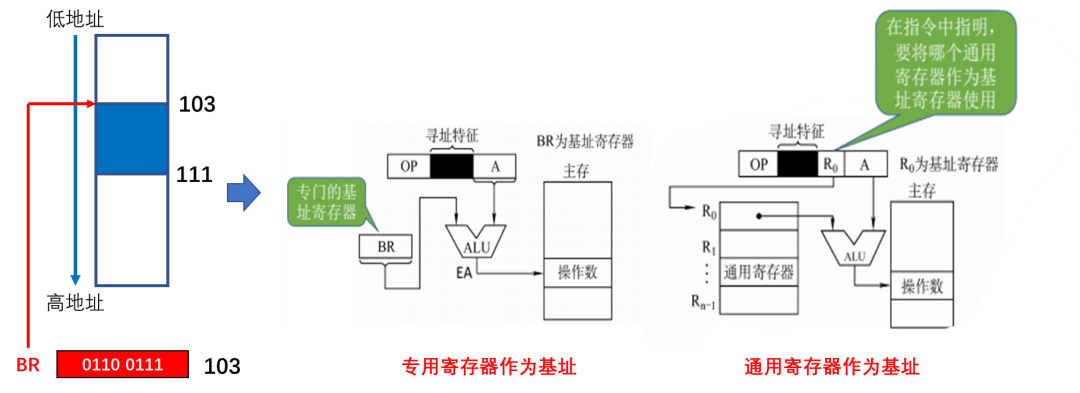

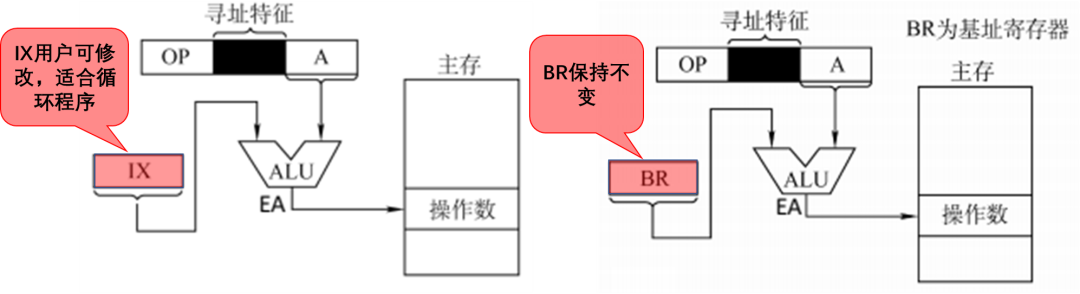

基址寻址:将 CPU 中的基址寄存器(BA)的内容加上指令格式中的形式地址 A,而形成操作数的有效地址,即为 EA=(BR)+A。

变址寻址:有效地址 EA 等于指令字中的形式地址 A 与变址寄存器 IX 的内容相加之和,即 EA=(IX)+A,其中 IX 可谓编制寄存器(专用),也可用通用寄存器作为变址寄存器。与基址寻址的方式的区别在于 IX 可以被用户修改。

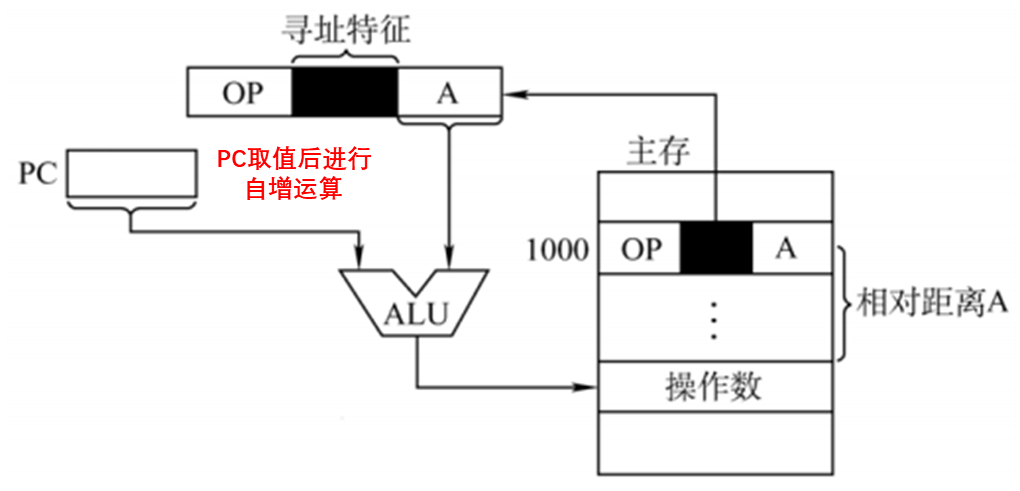

相对寻址把程序计数器 PC 的内容加上指令格式中的形式地址 A 而形成操作数的有效地址,即 EA=(PC)+A,其中 A 为相对于 PC 所指地址的位移量,可证可负,补码表示。

堆栈寻址:

基于堆栈寻址,下图所示为一个加法运算的过程:

step1: 堆栈指针 SP 指向 R0,对应数据 0001 出栈进入 ACC,SP 指向 R1;

step2:SP 对应数据 1001 出栈进入寄存器 X,SP 指向 R2;

step3:ALU 计算 ACC 与 X 的和(为 1010),送至寄存器 Y;

step4: 计算结果入栈,SP 指向 R1,将 Y(1010)送至堆栈寄存器 R1。