一 I.MX6ull 中断介绍

1 中断类型

Cortex-A7内核有8个异常中断,这8个异常中断的中断向量表如下表所示:

Cortex-A 内核 CPU 的所有外部中 断都属于这个 IRQ 中断,当任意一个外部中断发生的时候都会触发 IRQ 中断。在 IRQ 中断服 务函数里面就可以读取指定的寄存器来判断发生的具体是什么中断,进而根据具体的中断做出 相应的处理。

2 中断控制器 GIC

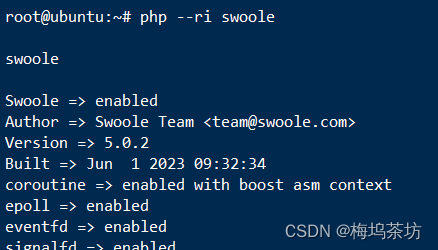

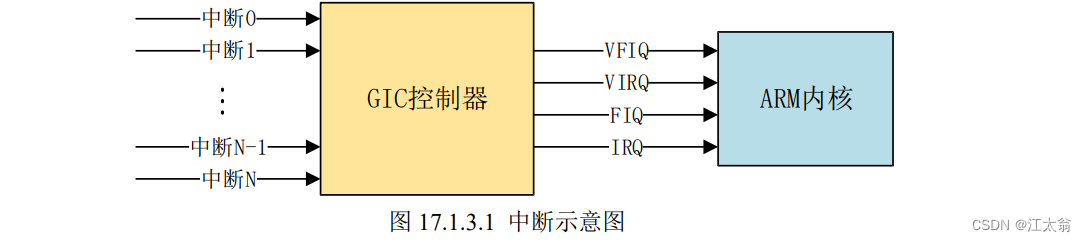

STM32(Cortex-M)的中断控制器叫做 NVIC,I.MX6U(Cortex-A)的中断控制器叫做 GIC, 关于 GIC 的详细内容请参考开发板光盘中的文档《ARM Generic Interrupt Controller(ARM GIC

控制器)V2.0.pdf》。 GIC 是 ARM 公司给 Cortex-A/R 内核提供的一个中断控制器,类似 Cortex-M 内核中的 NVIC。

当 GIC 接收到外部中断信号以后就会报给 ARM 内核,但是ARM 内核只提供了四个信号给 GIC 来汇报中断情况:VFIQ、VIRQ、FIQ 和 IRQ,他们之间的 关系如图 17.1.3.1 所示:、

GICV2 的逻辑图

每个CORE都有一个GIC控制器

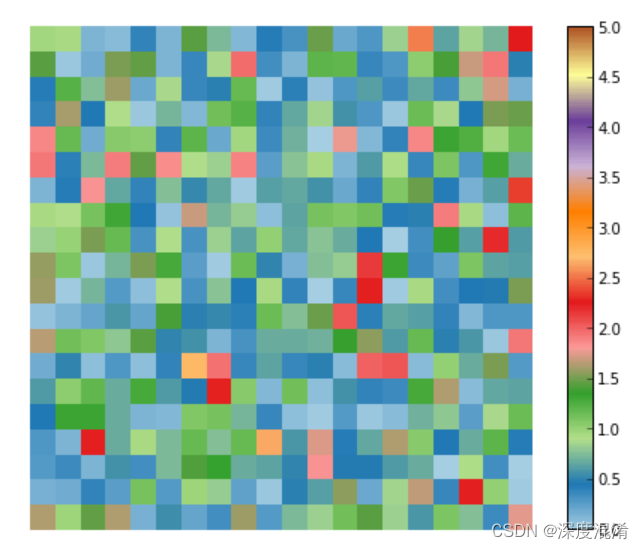

3 中断源

通过中断ID 定义中断源 (每一个 CPU 最多支持 1020 个中断 ID)

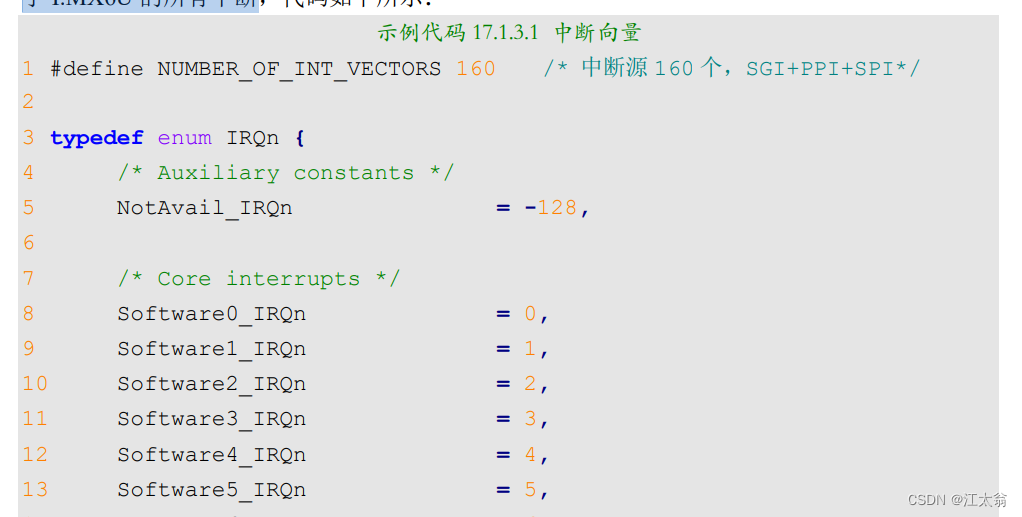

NXP 官方 SDK 中的文件 MCIMX6Y2C.h,在此文件中定义了一个枚举类型 IRQn_Type

此枚举类型就枚举出 了 I.MX6U 的所有中断 三大类

①、SPI(Shared Peripheral Interrupt),共享中断,顾名思义,所有 Core 共享的中断,这个是最 常见的,那些外部中断都属于 SPI 中断(注意!不是 SPI 总线那个中断) 。比如按键中断、串口 中断等等,这些中断所有的 Core() 都可以处理,不限定特定 Core。

②、PPI(Private Peripheral Interrupt),私有中断,我们说了 GIC 是支持多核的,每个核肯定 有自己独有的中断。这些独有的中断肯定是要指定的核心处理,因此这些中断就叫做私有中断。

③、SGI(Software-generated Interrupt),软件中断,由软件触发引起的中断,通过向寄存器

GICD_SGIR 写入数据来触发,系统会使用 SGI 中断来完成多核之间的通信。

ID0~ID15:这16个ID分配给SGI。

ID16~ID31:这16个ID分配给PPI。

ID32~ID1019:这988个ID分配给SPI,像GPIO中断、串口中断等这些外部中断 ,至于具体到某个ID对应哪个中断那就由半导体厂商根据实际情况去定义了。

比如I.MX6U的总共使用了128个中断ID,加上前面属于PPI和SGI的32个ID,I.MX6U的中断源共有128+32=160个,