CP15

CP15协处理器是ARM处理器中一门重要的协处理器,主要用来控制 cache、TCM( tiny code memory)和存储器管理。 CP15协处理器包含16个32位的寄存器,其编号为0~15,其中CP15寄存器0是预留的,所以CP15实际有15个寄存器。访问CP15寄存器的指令主要是MCR和MRC这两个指令,MRC指令将ARM处理器的寄存器中的数据传送到协处理器寄存器中,而MCR指令将协处理器寄存器中的数据传送到ARM处理器的寄存器中。

指令 MRC/MCR

MRC 就是读 CP15 寄存器, MCR 就是写 CP15 寄存器, MCR 指令格式如下:

MCR{cond} p15, <opc1>, <Rt>, <CRn>, <CRm>, <opc2>

cond: 指令执行的条件码,如果忽略的话就表示无条件执行。

opc1: 协处理器要执行的操作码。

Rt: ARM 源寄存器,要写入到 CP15 寄存器的数据就保存在此寄存器中。

CRn: CP15 协处理器的目标寄存器。

CRm: 协处理器中附加的目标寄存器或者源操作数寄存器,如果不需要附加信息就将

CRm 设置为 C0,否则结果不可预测。

opc2: 可选的协处理器特定操作码,当不需要的时候要设置为 0。

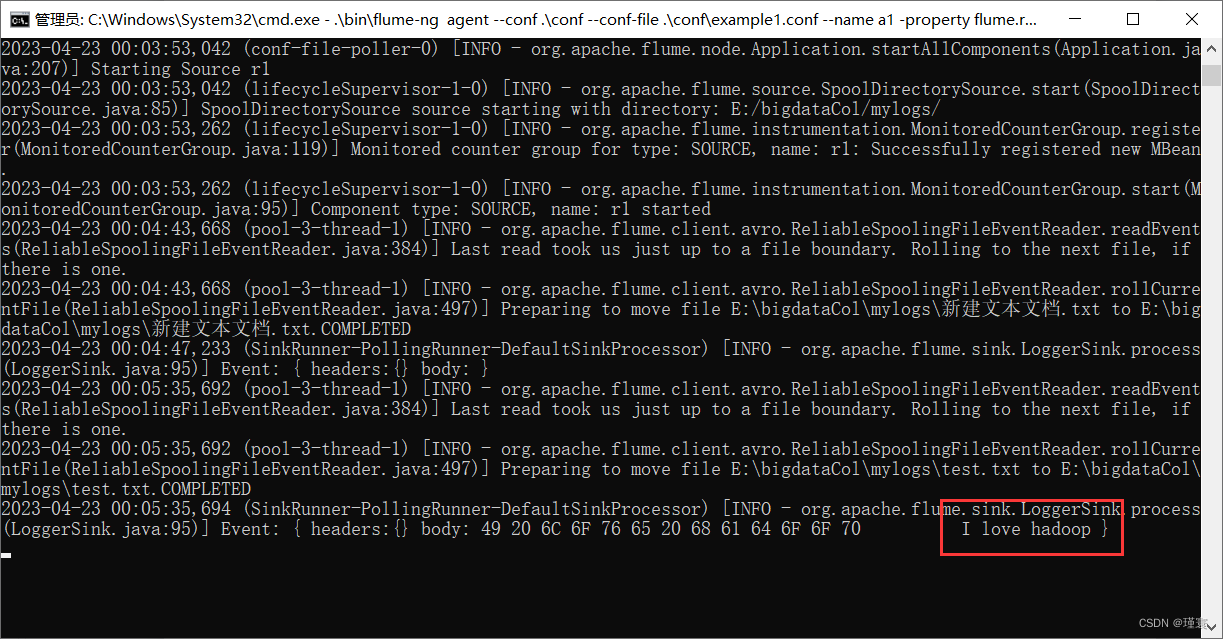

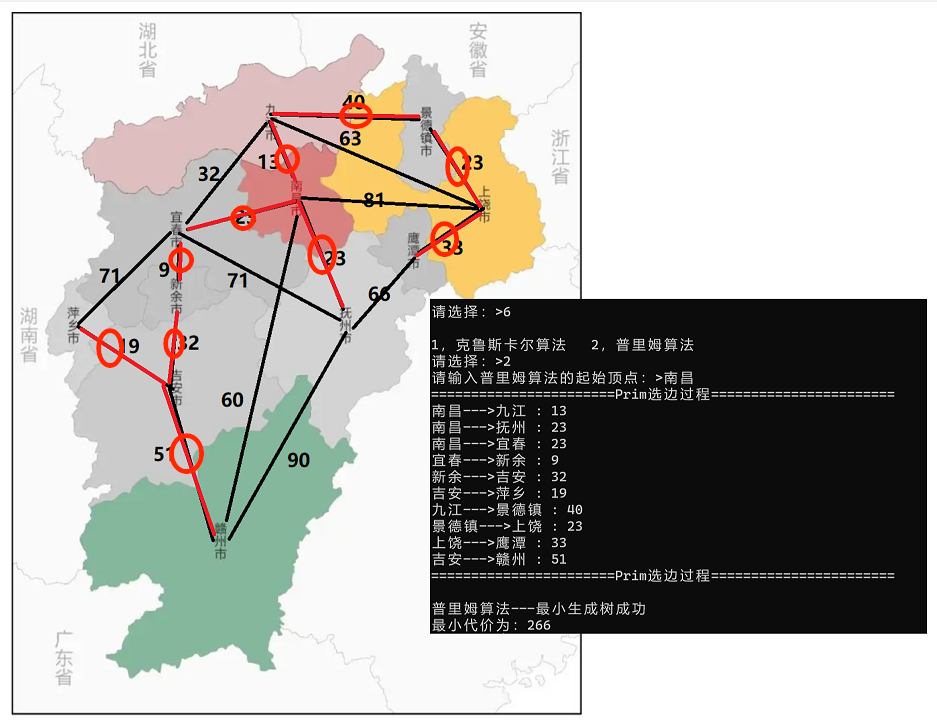

参照下图 CP15 中 C0 寄存器的值读取到 R0 寄存器中,

MRC p15, 0, r0, c0, c0, 0

MCR相反

![【PWN · ret2libc】[CISCN 2019东北]PWN2](https://img-blog.csdnimg.cn/17c7062a14264c4097ff9cc4a747dec7.png)