该文档仅为参考,如果在进行本系列虚拟项目的学习与实践,请自行完成本部分内容。 由于文档格式在之前博客中已展现,因此本文只针对关键点写一下方案。

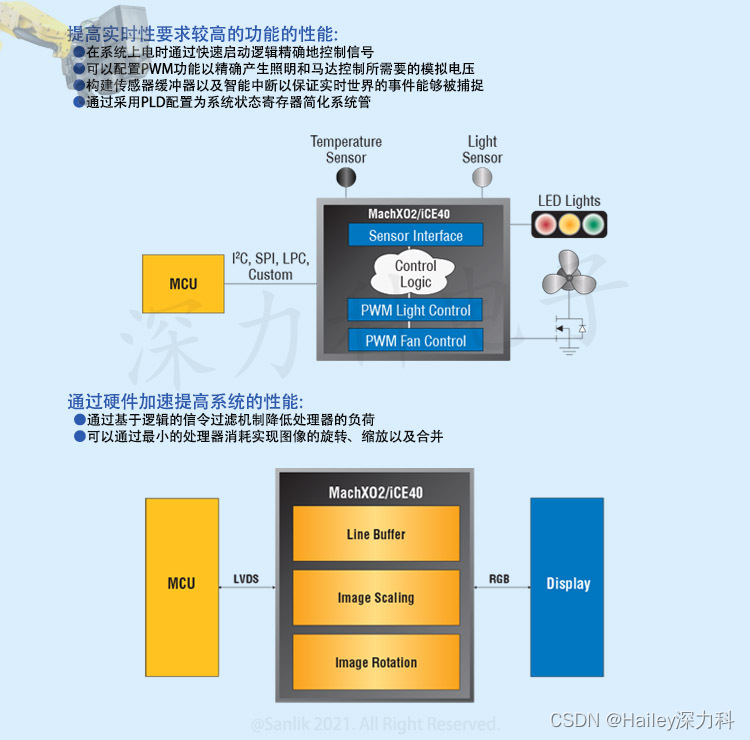

cpu_if模块概述

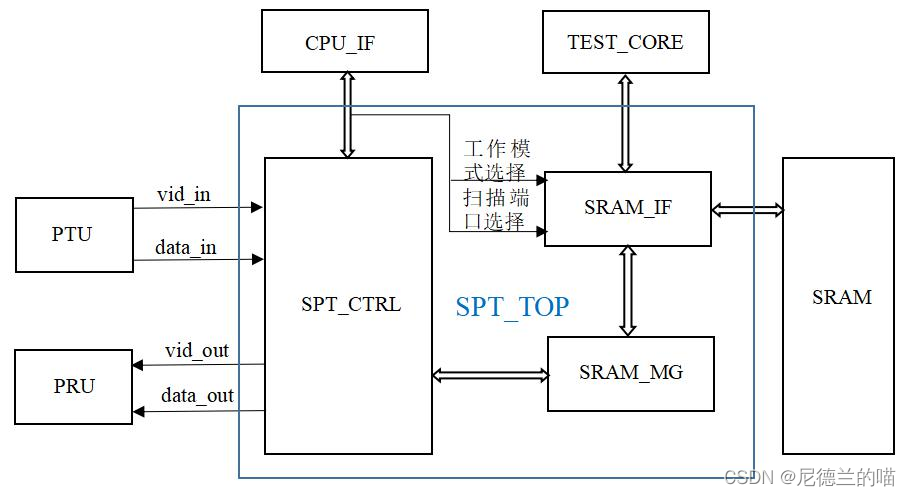

cpu_if模块主要是寄存器单元以及寄存器访问通路的处理,可以看下整体结构图:

因此我们可以概括cpu_if模块的功能点如下:

- 对cpu寄存器访问接口进行同步时序和读写响应;

- 根据属性维护寄存器并输出正确值;

- 根据内部电路反馈更新寄存器状态;

因此下面就根据这几个功能点简述一下模块设计思路。

cpu访问接口同步与响应

以cpu读为例,接口时序图如下: