目录

- 1、前言

- 2、我这里已有的UDP方案

- 3、详细设计方案

- 传统UDP网络通信方案

- 本方案详细设计说明

- DMA和BRAM

- AXIS-FIFO

- UDP模块设计

- UDP模块FIFO

- AXI 1G/2.5G Ethernet Subsystem:

- 输出

- 4、vivado工程详解

- 5、上板调试验证并演示

- 注意事项

- 6、福利:工程代码的获取

1、前言

目前网上的fpga实现udp基本生态如下:

1:verilog编写的udp收发器,但不带ping功能,这样的代码功能正常也能用,但不带ping功能基本就是废物,在实际项目中不会用这样的代码,试想,多机互联,出现了问题,你的网卡都不带ping功能,连基本的问题排查机制都不具备,这样的代码谁敢用?

2:带ping功能的udp收发器,代码优秀也好用,但基本不开源,不会提供源码给你,这样的代码也有不足,那就是出了问题不知道怎么排查,毕竟你没有源码,无可奈何;

3:使用了Xilinx的Tri Mode Ethernet MAC三速网IP实现,这样的代码也很优秀,但还是那个问题,没有源码,且三速网IP需要licence,三速网IP实现了rgmii到gmii再到axis的转换;

4:使用FPGA的GTX资源利用SFP光口实现UDP通信,这种方案不需要外接网络变压器即可完成,本方案就是此种设计;

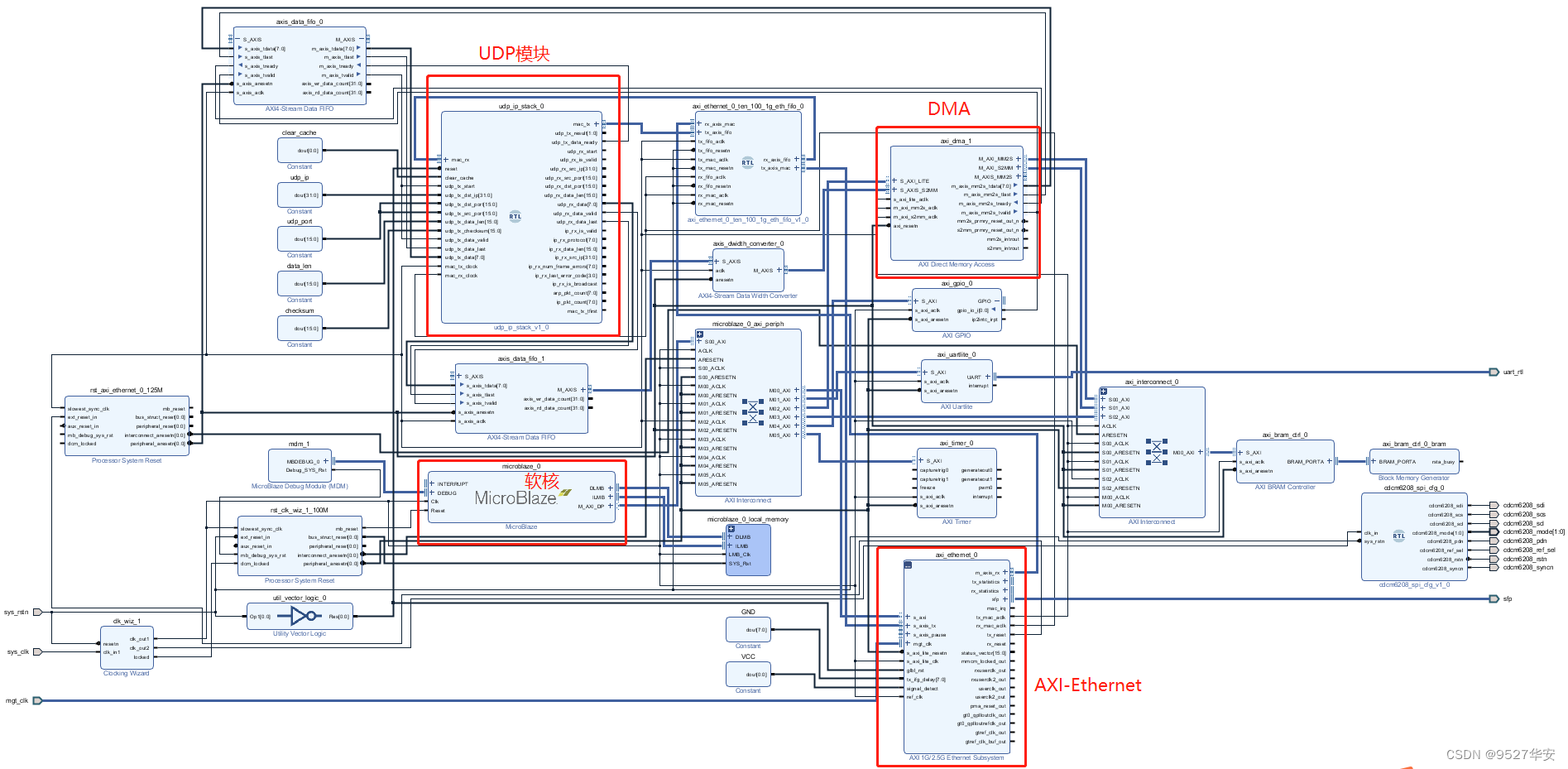

本设计调用Xilinx的AXI 1G/2.5G Ethernet Subsystem IP,使用硬件语言编写的UDP协议栈实现UDP通信的MAC层设计,调用Xilinx官方的AXI 1G/2.5G Ethernet Subsystem IP核实现了网络变压器的功能,从而实现无需外挂网络芯片即可实现UDP通信的方案;UDP协议栈已封装为FIFO接口,使得用户无需关心复杂的UDP协议而只需关心简单的用户接口时序即可操作UDP收发,非常简单;本设计调用AXI DMA和MicroBlaze,实现软核通过DMA发起UDP通信,MicroBlaze也可以用zynq代替,实现了zynq里PS软件通过调用PL端硬件资源实现1G千兆网UDP通信的功能;

本设计连接1路SFP光口,并使SFP光口的收发两端相连形成数据回环;FPGA开发板配置为UDP服务器;本设计经过反复大量测试稳定可靠,可在项目中直接移植使用,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字通信领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

2、我这里已有的UDP方案

目前我这里有如下几种UDP方案和应用实例:

我的博客主页有个FPGA以太网通信专栏,专栏是免费的,里面有很多FPGA实现的UDP应用,既有常规千兆网也有万兆网方案,对网络通信有需求的兄弟可以去看看:直接点击前往

3、详细设计方案

传统UDP网络通信方案

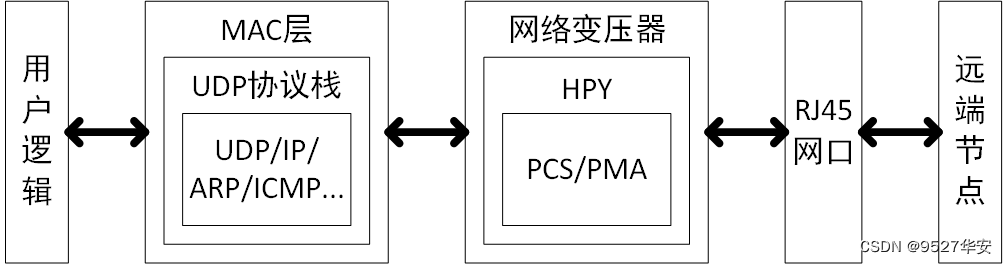

在讲述设计方案之前,我们先来看看FPGA实现UDP通信方案应具备什么条件,大体如下:

1:用户逻辑:

开发者需要收发的实际数据,可以以多种形势存在,比如自定义格式、AXIS数据流格式等等,用户逻辑的接口时序必须与MAC层的接口时序一致;

2:MAC层

主要由UDP、IP、ARP、ICMP等具体的协议逻辑组成,实现网络数据的组包与拆包,相当于做了软件里Sockte做的事儿,Sockte依赖CPU做网络数据包,而这里的MAC层直接使用硬件资源做网络数据包,解放了网络数据包对CPU的奴役,在当今时髦儿的RDMA中得以完美体现。。。本设计的MAC层采用米联客的UDP协议栈,关于这部分,请参考我之前写的文章

3:网络变压器

主要由PCS/PMA组成,PCS主要实现并行数据的编解码,比如经典的8b/10编解码,PMA主要实现并串/串并转换,输出接口是高速差分信号,可直接与SFP或者RG45网口连接;

4:RJ45网口:俗称水晶头,插网线的。。。

5:远端节点

本FPGA开发板可以理解为一个网卡,远端节点就是与之连接的另一个网卡,比如电脑主机上的网卡;

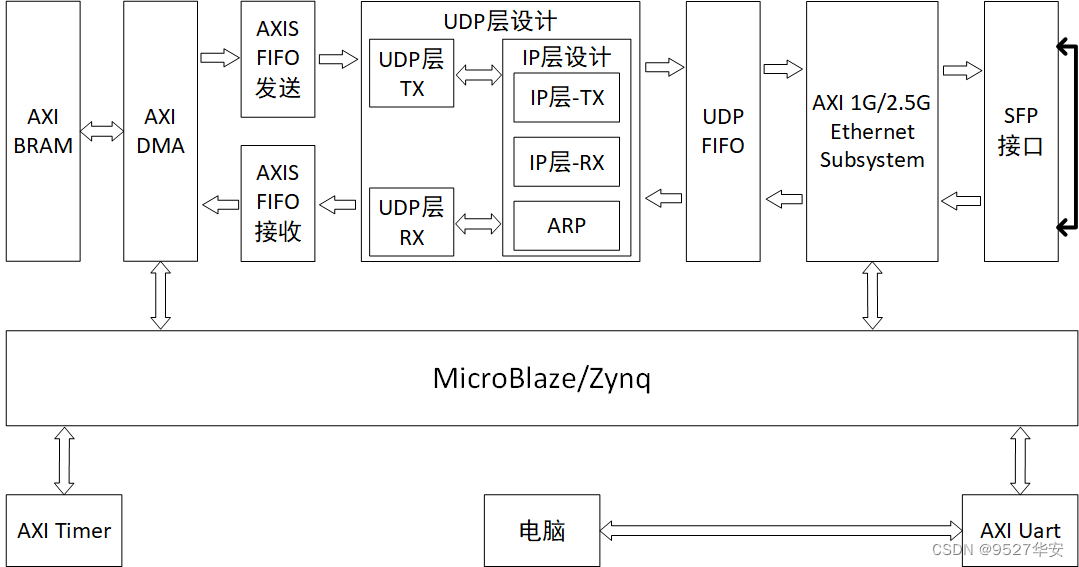

本方案详细设计说明

本设计与上述传统的FPGA实现UDP方案不同的是网络变压器部分,前面的网络变压器是真实的网络PHY芯片,比如我常用到的RTL8211、B50610、88E1518等等;本设计没有用到网络变压器,而是调用Xilinx官方的AXI 1G/2.5G Ethernet Subsystem IP核实现了网络变压器的功能,通过SFP光口输出实现UDP协议数据通信,设计框图如下:

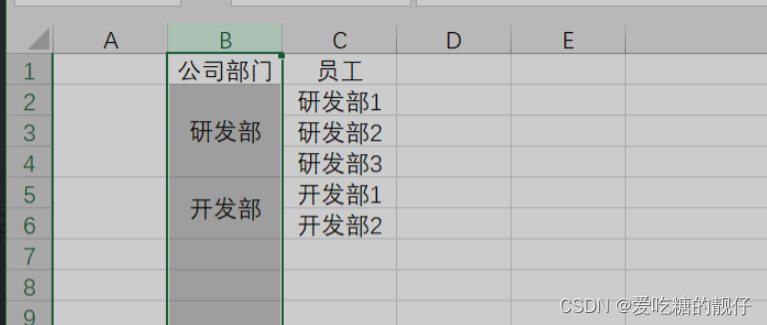

DMA和BRAM

AXI-BRAM充当存储介质,可以用DDR代替,AXI-BRAM负责存储待发送UDP模块的数据,也存储从UDP模块接收到的UDP数据,如果数据量大,则可换成DDR,将AXI-BRAM换成AXI-MIG;AXI-DMA充当软件和硬件之间的桥梁,MicroBlaze软核通过AXI-Lite接口控制DMA的数据流向,也可以将软件侧的数据通过DMA发送出去,后端的UDP模块和AXI-Ethernet等硬件资源完全无需关心;如果是zynq系列器件,则可把MicroBlaze软核替换为Zynq软核,这样就实现了PS和PL资源的交互,且PS软件可直接控制硬件UDP协议完成数据收发,在架构上属于高端架构。。。

AXIS-FIFO

AXIS-FIFO充当AXI-DMA与UDP模块的桥梁,因为AXI-DMA的用户接口为AXIS数据流,而UDP模块也已封装为FIFO接口,所以直接调用两个AXIS-FIFO轻松实现不同数据接口模块之间的屋里连接,这里调用两个AXIS-FIFO,一个作为接收,另一个作为发送;

UDP模块设计

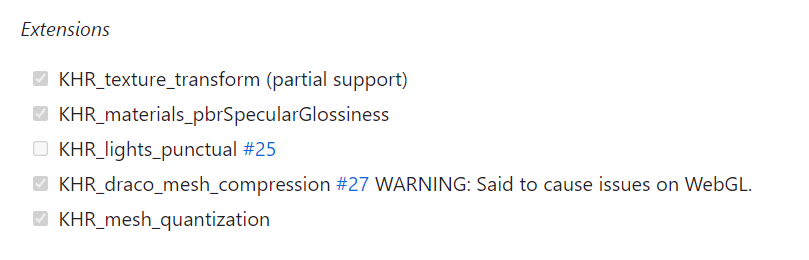

该UDP协议栈的功能和性能参数如下:原谅我装13秀一波英文。。。

FEATURES:

Implements UDP, IPv4, ARP protocols

Zero latency between UDP and MAC layer

(combinatorial transfer during user data phase)

See simulation diagram below

Allows full control of UDP src & dst ports on TX.

Provides access to UDP src & dst ports on RX (user filtering)

Couples directly to Xilinx Tri-Mode eth Mac via AXI interface

Separate building blocks to create custom stacks

Easy to tap into the IP layer directly

Supports TX and RX with IP layer broadcast address

Separate clock domains for tx & rx paths

Choice of smaller single slot ARP or multislot up to 255 slots

Tested for 1Gbit Ethernet, but applicable to 100M and 10M

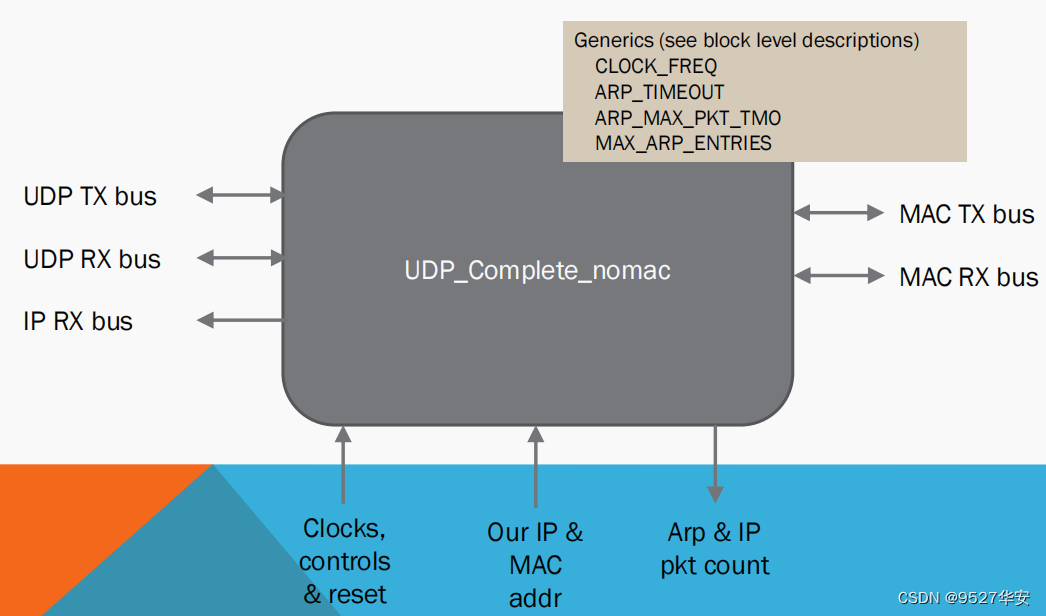

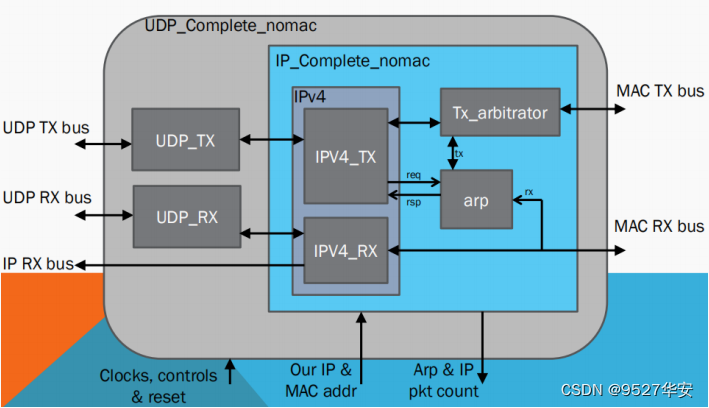

UDP协议栈 Bolck Design设计框图如下:

核心代码采用VHDL语言实现,是为了更好的时序,顶层代码采用verilog语言实现,是为了方便用户例化,UDP模块已封装为FIFO接口,使得用户无需关心复杂的UDP协议而只需关心简单的用户接口时序即可操作UDP收发,非常简单;UDP模块带动态ARP、IP仲裁等功能,但不带ping功能;具体设计框图如下:

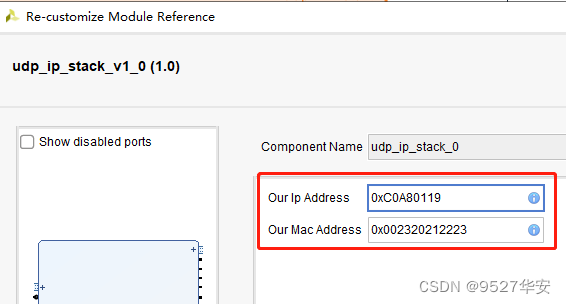

UDP层代码顶层文件直接拖入Block Design中可生成IP界面,IP界面可配置IP地址等信息,如图:

UDP模块FIFO

作用与前面说的AXIS-FIFO功能类似,充当UDP模块与AXI-Ethernet的桥梁,因为AXI-Ethernet的用户接口为AXIS数据流,而UDP模块也已封装为FIFO接口,所以手写一个UDP模块FIFO轻松实现不同数据接口模块之间的屋里连接;

AXI 1G/2.5G Ethernet Subsystem:

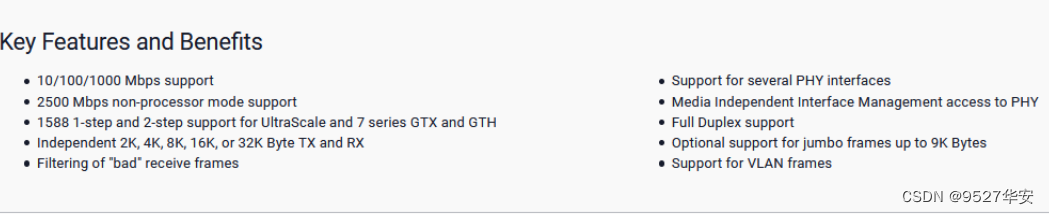

本设计使用 AXI 1G/2.5G Ethernet Subsystem IP 核实现物理层功能,IP核通过MicroBlaze软核配置;根据官方文档介绍,该IP功能如下:

更多关于该IP的细节,请自行阅读官方手册《pg138-axi-ethernet》;

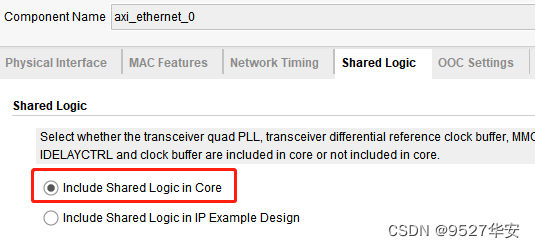

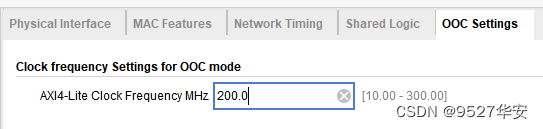

AXI 1G/2.5G Ethernet Subsystem IP 核具体配置说明如下:

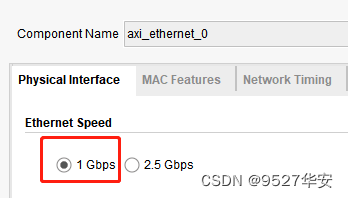

1: 配置链路速率为 1Gbps。;

2: 配置 PHY 接口类型为 1000BaseX;

3: 配置 MDIO PHY Address 为 1;

具体配置界面如图:

输出

AXI 1G/2.5G Ethernet Subsystem IP核直接输出到SFP接口,并使SFP光口的收发两端相连形成数据回环,即可完成工程的硬件连接,另外,为了与FPGA开发板通信和打印测试信息,工程还调用了一个AXI Uart IP,所以还需要一根USB转串口线连接开发板与电脑,电脑打开串口调试助手接口收到FPGA开发板打印的信息;串口波特率为115200,数据位8,无校验;

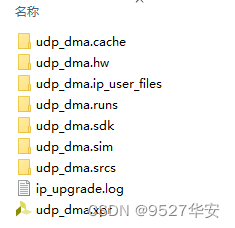

4、vivado工程详解

开发板FPGA型号:Xilinx-xc7k325tffg676-2;

开发环境:vivado2019.1;

输入/输出:SFP光口;

测试项:UDP数据回环;

工程Block Design如下:

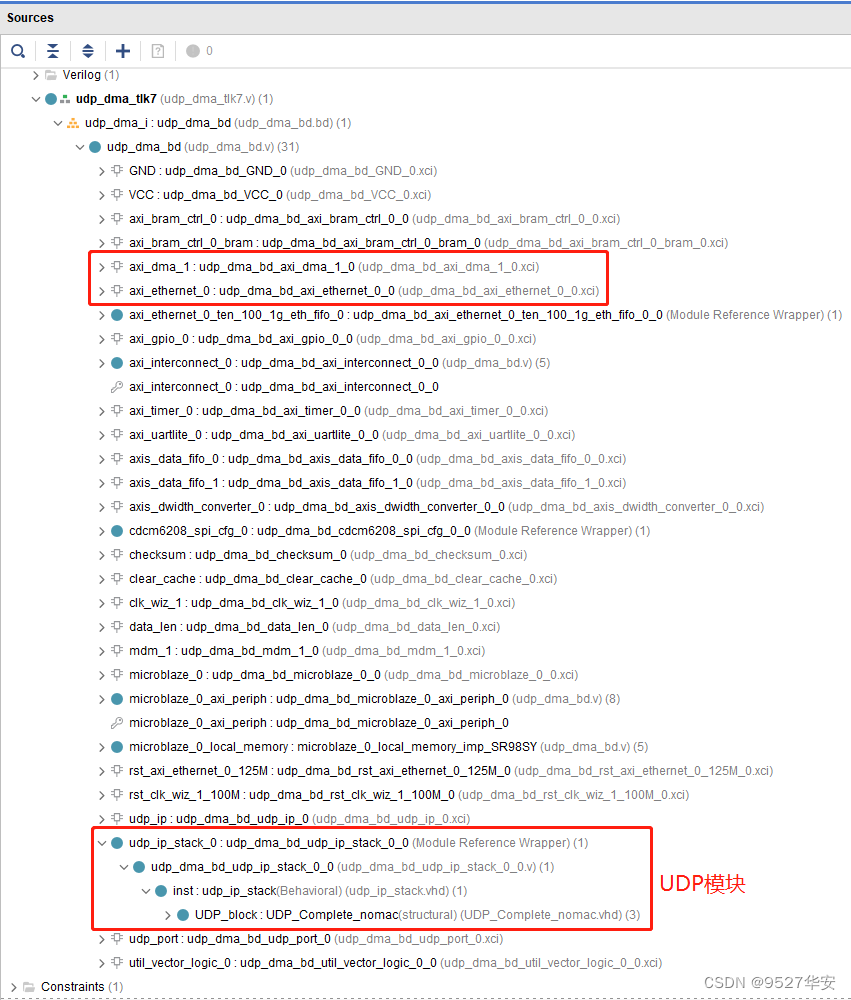

综合后的工程代码架构如下:

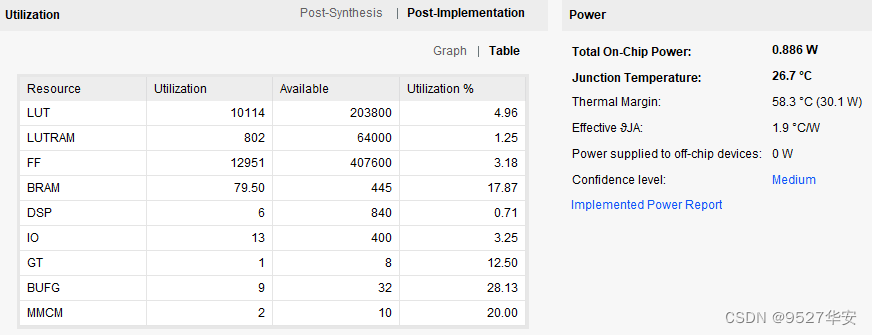

综合编译后的FPGA资源消耗和功耗预估如下:

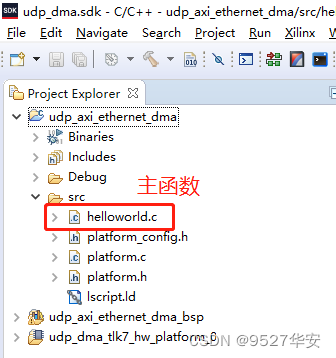

SDK代码架构如下:

5、上板调试验证并演示

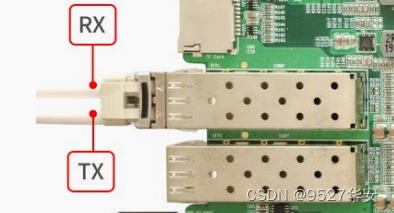

本设计连接1路SFP光口,并使SFP光口的收发两端相连形成数据回环,如下:

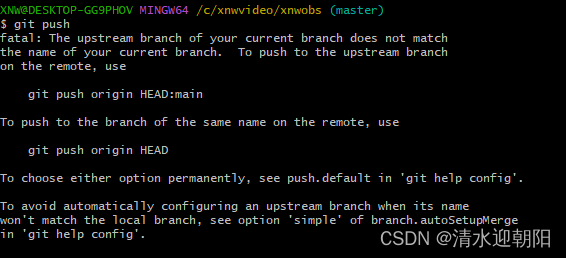

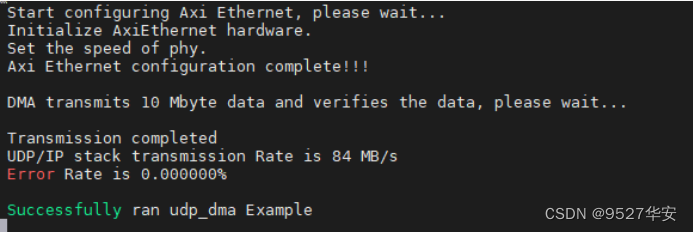

打开vivado工程,编译后导出bit,运行SDK,然后通过SDK下载程序运行,打开电脑的串口调试助手,你会看到如下打印即可看到串口调试终端打印 SFP+光口外部回环的数据传输测试信息。

本案例的 GTX 带宽配置为 1Gbps,即 125MB/s。如下:

可从上图得到如下信息:

SFP+光口外部回环的数据传输速率为 84MB/s;

SFP+光口外部回环的数据传输误码率为 0;

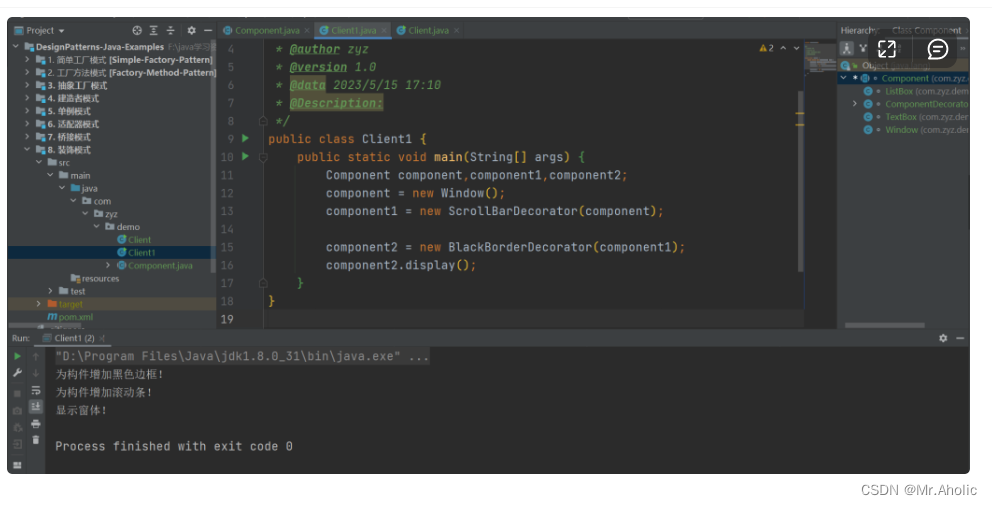

SDK软件代码主要完成如下功能:

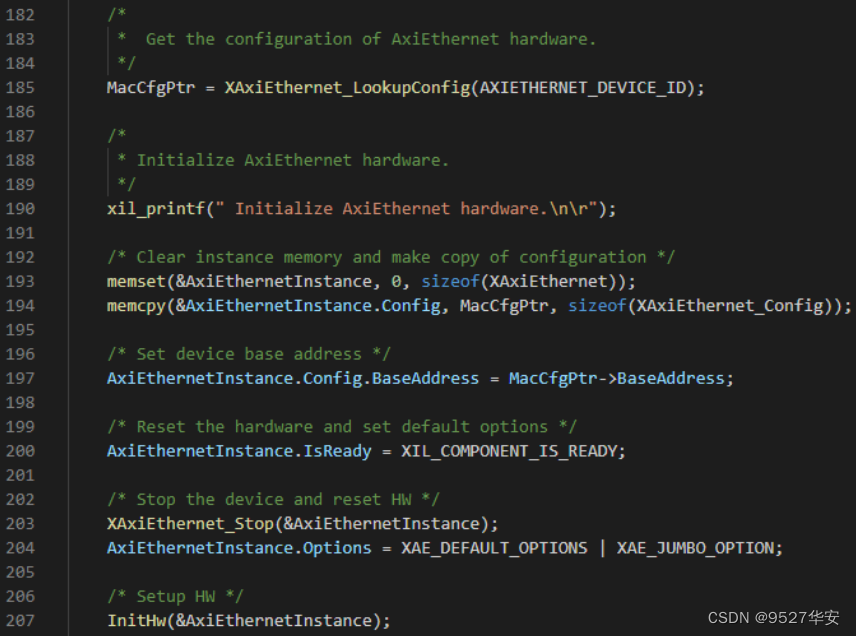

1:初始化 AXI Ethernet 驱动程序,如下:

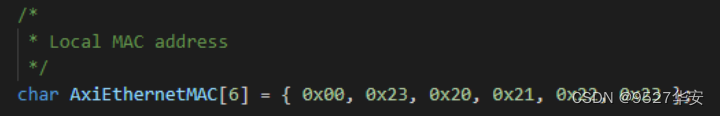

2:设置 MAC 地址,需与UDP模块所设置的 MAC 地址一致,如下:

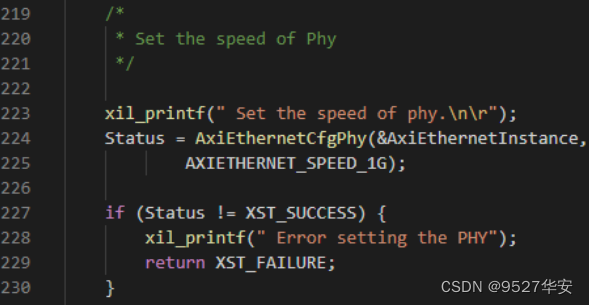

3:设置 PHY 参数,如链路速率等,如图:

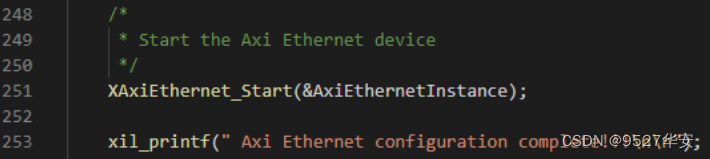

4:启动 AXI Ethernet 设备,如下:

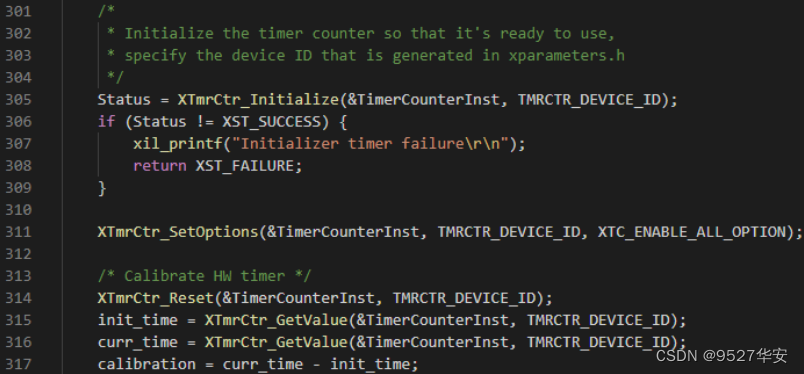

5:初始化并校准定时器,如下:

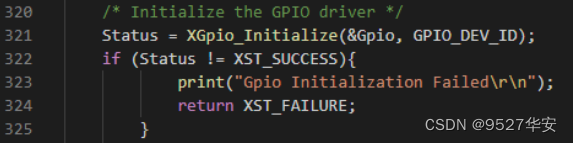

6:初始化 GPIO 驱动程序,用于监测 DMA AXIS MM2S Tvalid 信号;

由于本案例使用的 UDP 协议栈所支持的标准 UDP 包的数据长度小于 AXI DMA IP核内置 FIFO,当 AXI DMA 传输完成后,DMA 内部状态寄存器不会发生改变,因此无法通过检测 DMA 内部状态寄存器判断是否传输完成。故需增加 AXI GPIO IP 核来监测 AXI DMA的 Stream 端的 MM2S Tvalid 信号,从而判断 DMA 是否传输完成。如下:

7:初始化 DMA 设备,使用轮询模式,关闭 DMA 中断,构建每次传输所要发送的数据包,分别往 DMA 设备写入源地址、目的地址以及数据量,并启动 DMA 传输。启动DMA 传输后,使用 Timer 进行计时,等待 DMA 传输完成后计算数据传输速率;每次传输完成后,对传输数据进行校验;计算数据传输平均速率与误码率;这部分代码太多,就不截图了;

注意事项

AXI 1G/2.5G Ethernet Subsystem IP核需要Licence才能编译生成比特流,请到官方申请Licence

6、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

![[比赛简介]ICR - Identifying Age-Related Conditions](https://img-blog.csdnimg.cn/5b2e3e4152e646979669babb6095055e.png)