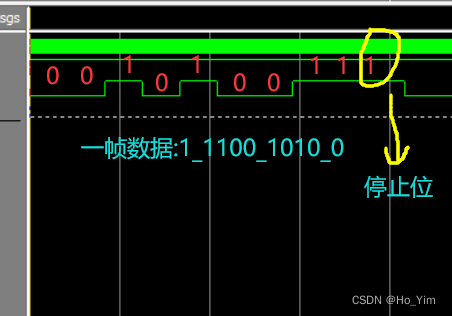

module Uart(

input clk, //H3

input rst, //F10

output reg TX //串口发送脚M12

);

reg[9:0] buffer = 10'b1_1100_1010_0; //接收方:0XCA

parameter SND_T = 5208; //9600bps

reg [15:0] cnt = 0;

//数据宽度计数

always @(posedge clk or negedge rst) begin

if(!rst) begin

TX <= 1'b0; //空闲态

end

else if(cnt < SND_T) begin

cnt <= cnt + 1;

end

else begin

cnt <= 0;

TX <= {buffer[0],buffer[9:1]};

buffer <= {buffer[0],buffer[9:1]};

end

end

endmodule

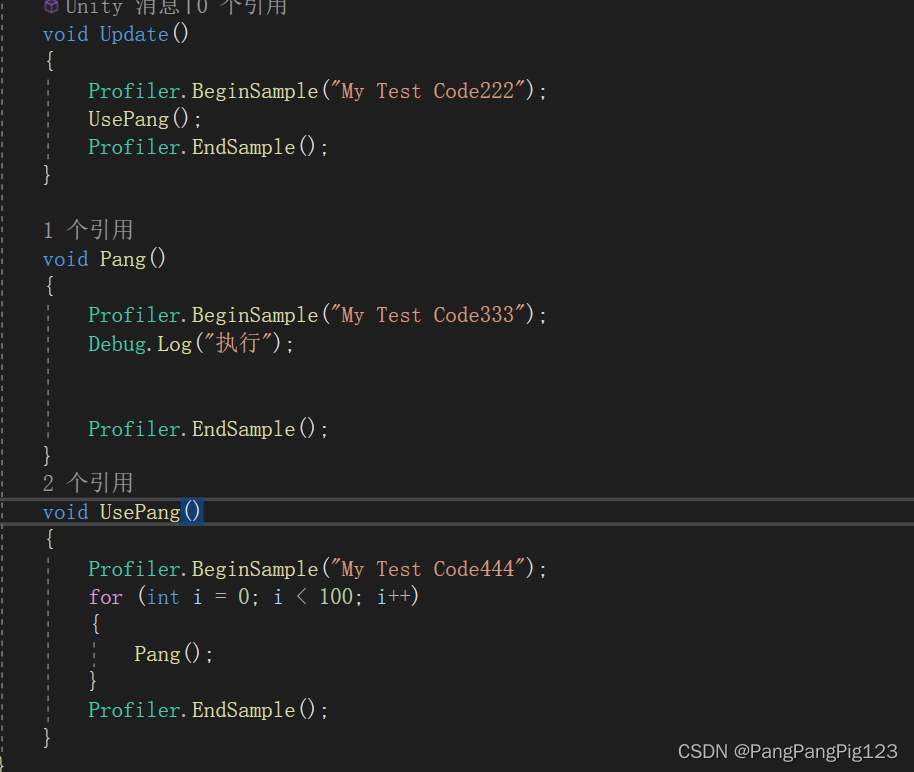

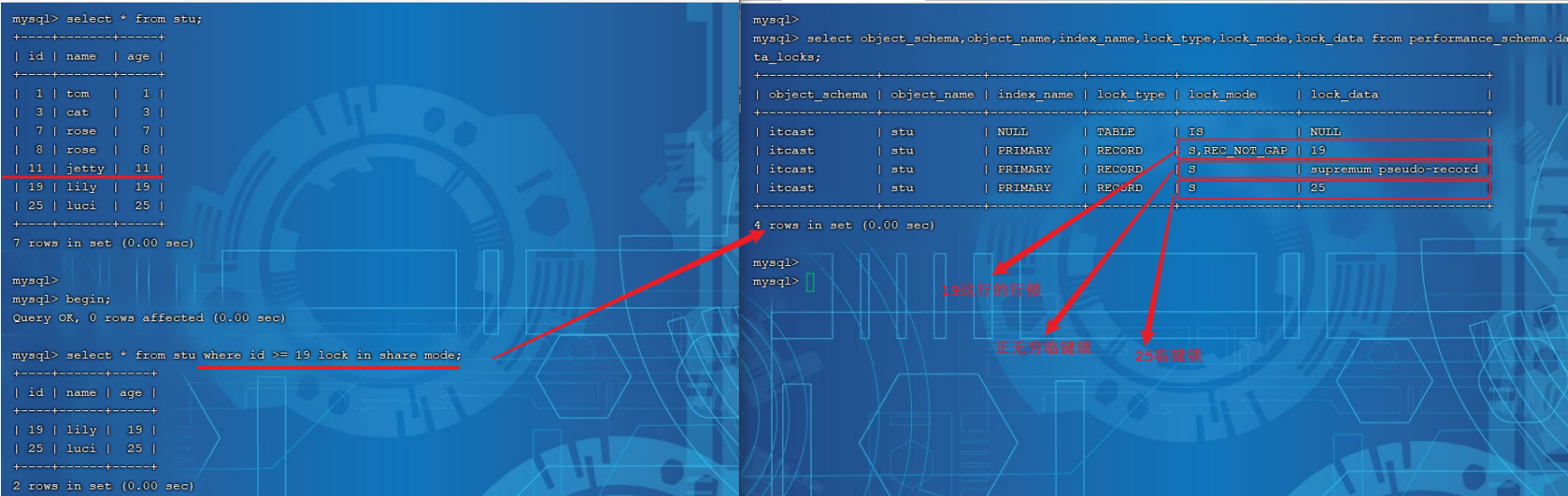

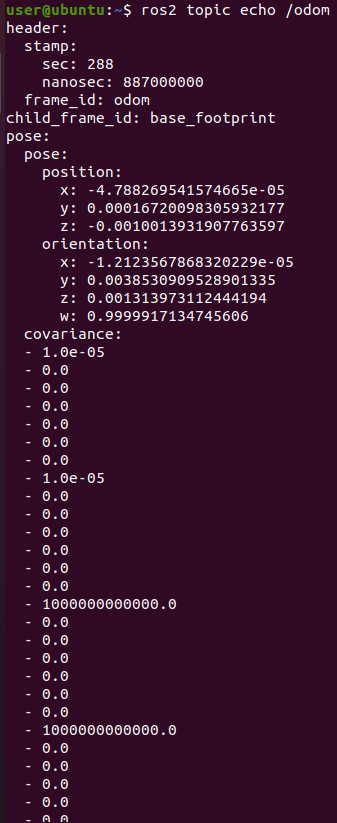

功能仿真:

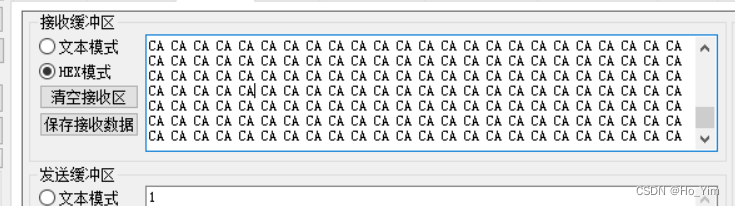

接收数据: