前段时间,在微信公众号上偶然看到一篇很不错的技术分享文章:《南湖处理器DFT设计范例》。文中详细介绍了中科院计算所的RISC-V处理器实施的DFT设计。

去年,也基于一款处理器应用过Share Test Bus技术,但在memory界面fault测试的问题,我注意到南湖的测试方法(RAM_sequential)更加友好。本文针对这方面内容,做了一些简单的技术总结。

通常,我们通过memory compiler 编译SRAM时,可以有以下几种选择或者场景:

编译是否打开Test 专用的pin/bus: TA/A, TD/D

编译器是否支持embedded scan chain

然后,环绕memory界面的缺陷测试,我们的通常选择也有如下几种:

1. RAM Bypass

在测试模式下,将RAM Bypass, 实现从写一侧逻辑拉到读一侧,提高缺陷测试的覆盖率。

在该方案下,我们注意到,进出memory的一段Net,实际上测试不到的。那么这部分,其实可以通过MBIST pattern 测试覆盖到。

但是,如果memory 编译时将功能BUS 和MBIST Test BUS 分开的话,这样就没办法用MBIST pattern 覆盖剩下的那部分测试。

2. Shadow logic

本质上,就是添加Control Point 和Observe point, 与RAM Bypass 方案其实比较接近。

3. RAM sequential Test

如果上述功能BUS与Test BUS 分开的场景;

或者,有些Core 有专门的Share Test Bus;

特别是,后者,我们既然已经采用了Share Test Bus 方案,避免了常规MBIST 方案会在SRAM 附近增加很多逻辑(对PD和Timing 很友好)。那么前述的Shadow logic insertion 或者RAM Bypass 方案,都不再合适了。

那么对,这两种场景,都将需要用到南湖方案:RAM Sequential Pattern.

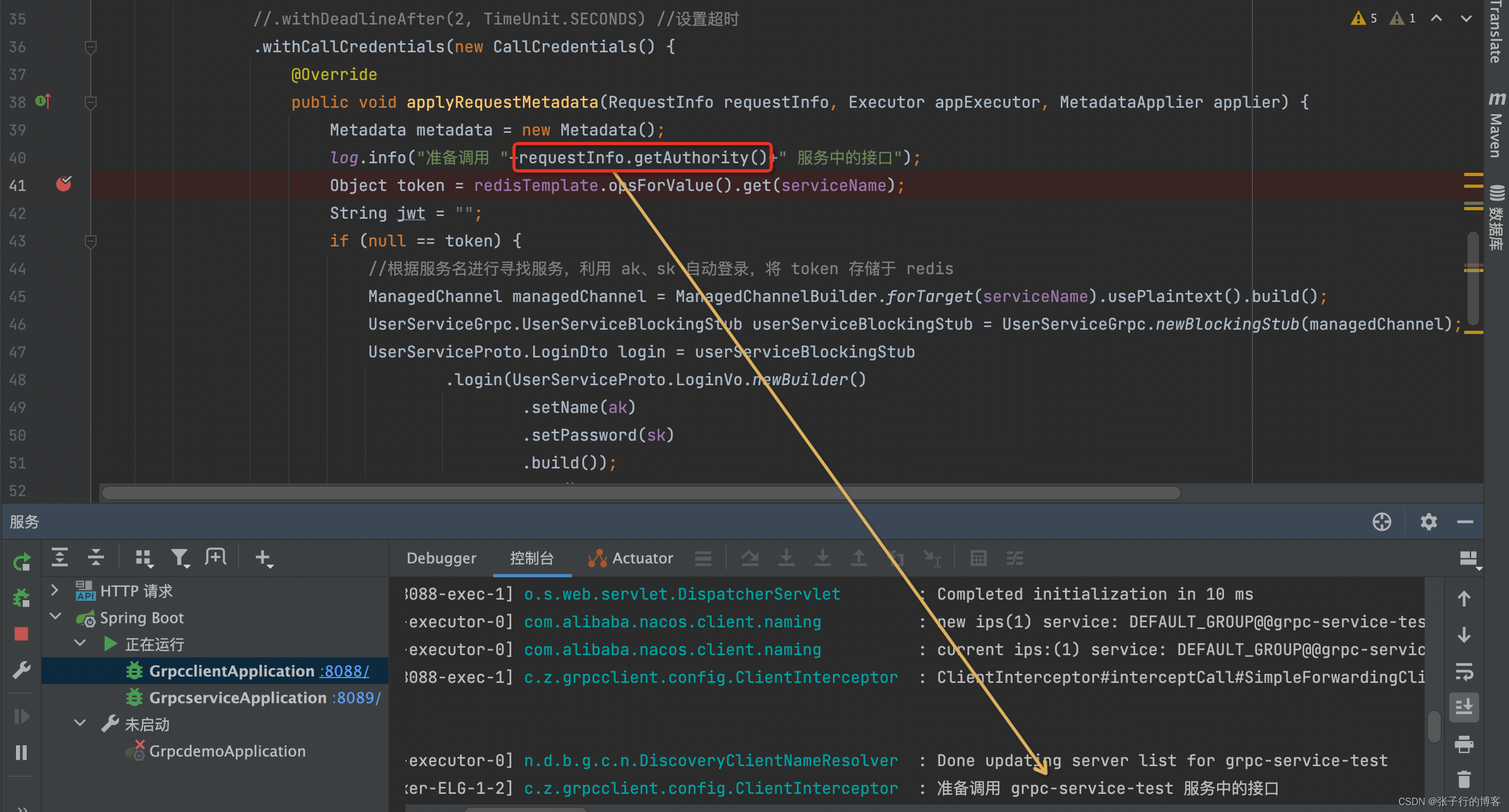

首先,以Memory Dataout BUS的Transition 测试流程为例,总结一下这个过程。

测试流程:

1. 通过scan chain load 给到Memory 前的Data flops = 0, Addr flops =0;

2. 通过OCC/OPCG 给定第一个Pulse, 将Data flops (D=0) 读入Memory 相应的地址(Addr =0)。

同时,将Data1 flops/Addr1 flops 的值更新到 Data flops/Addr flops

3. 通过OCC/OPCG 给定第二个Pulse, 将Data flops 的新值(D=1)读入Memory 相应的地址(Addr =1)

同时,Addr flops 从前级拿到新值,Addr = 0

4. 通过OCC/OPCG 给定第三个Pulse, 将Addr =0 的值读出到Memory Data Output.

同时,Addr flops 从前级拿到新值,Addr = 1

5. 通过OCC/OPCG 给定第四个Pulse, 将Addr = 1的值读出到Memory Data Output.

同时, Observe flops 读到了前面Addr =0 的值,

6. 通过OCC/OPCG给定第五个Pulse,

同时,Observe flops 读到了前面Addr = 1的值。

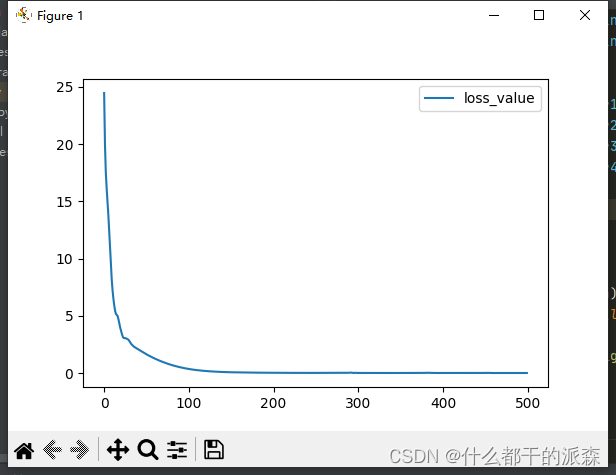

下图展示了读端口Transition 测试的时序图:

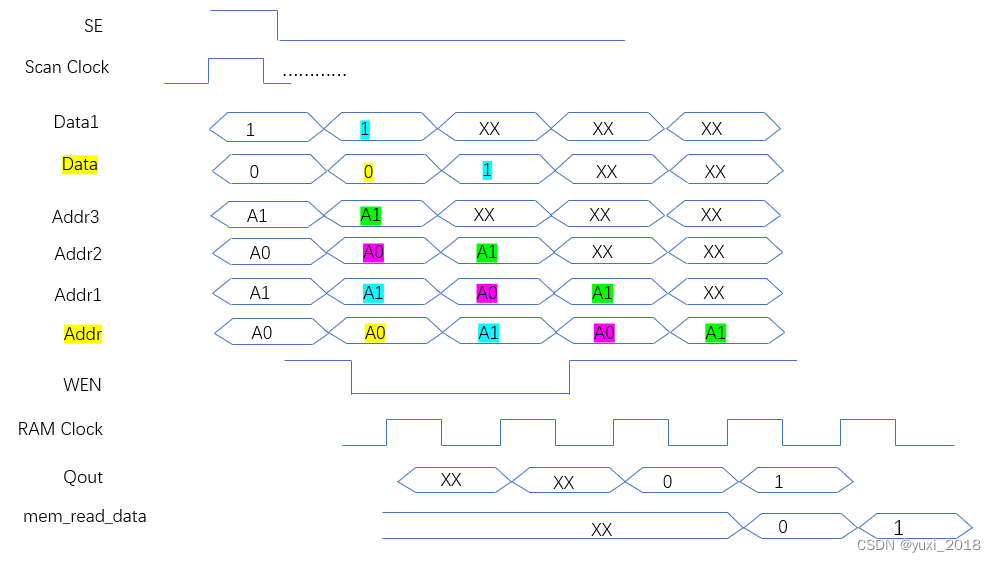

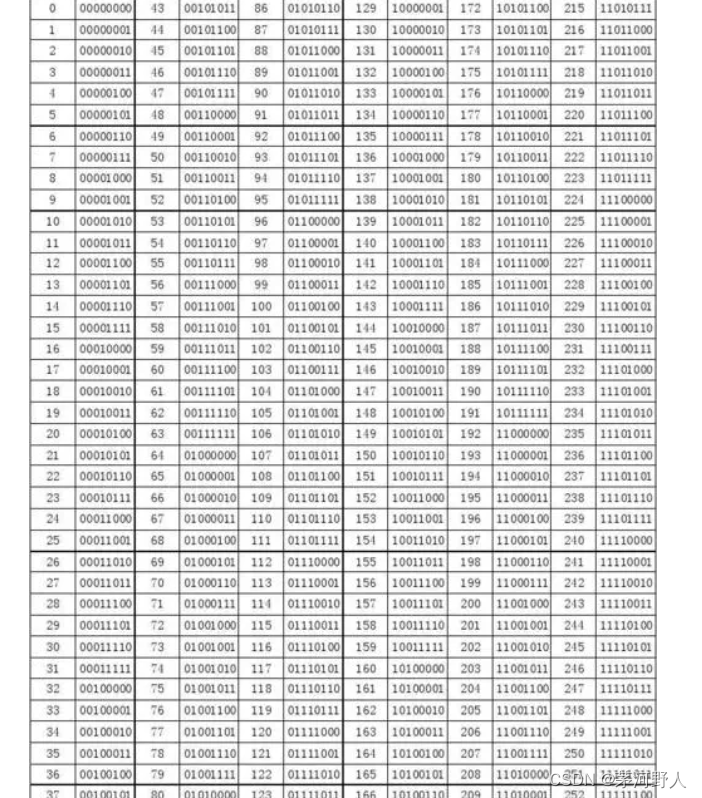

下图,展示了,memory及周围电路的示意图:

当然,如果Memory有embedded scan chain, 界面测试就更简单一些了。SRAM IP 就像一个IEEE1500 compliant Core 一样了,甚至像一个大号的MUX-D flop.

![[PyTorch][chapter 35][Batch Normalize]](https://img-blog.csdnimg.cn/32f6c77a462e465e98644bf6de4f38fa.png)