本文的思路框架:

①本文介绍3x3算子模块和5x5算子模块中,矩阵转化成串行数据后,对其排序,并获取矩阵中值数据;

②本例程中采用的FPGA设计技巧,可用于借鉴,一是采用for循环实现串行数据转化并行数据;二是采用两级for循环实现矩阵中数据的比较;

③本文比较采用纯逻辑方式进行比较,一个时钟输出数据,并且提供了3x3和5x5的矩阵算子模板使用的逻辑资源,需斟酌考虑使用,也就是所谓的面积和速度之间的平衡选择

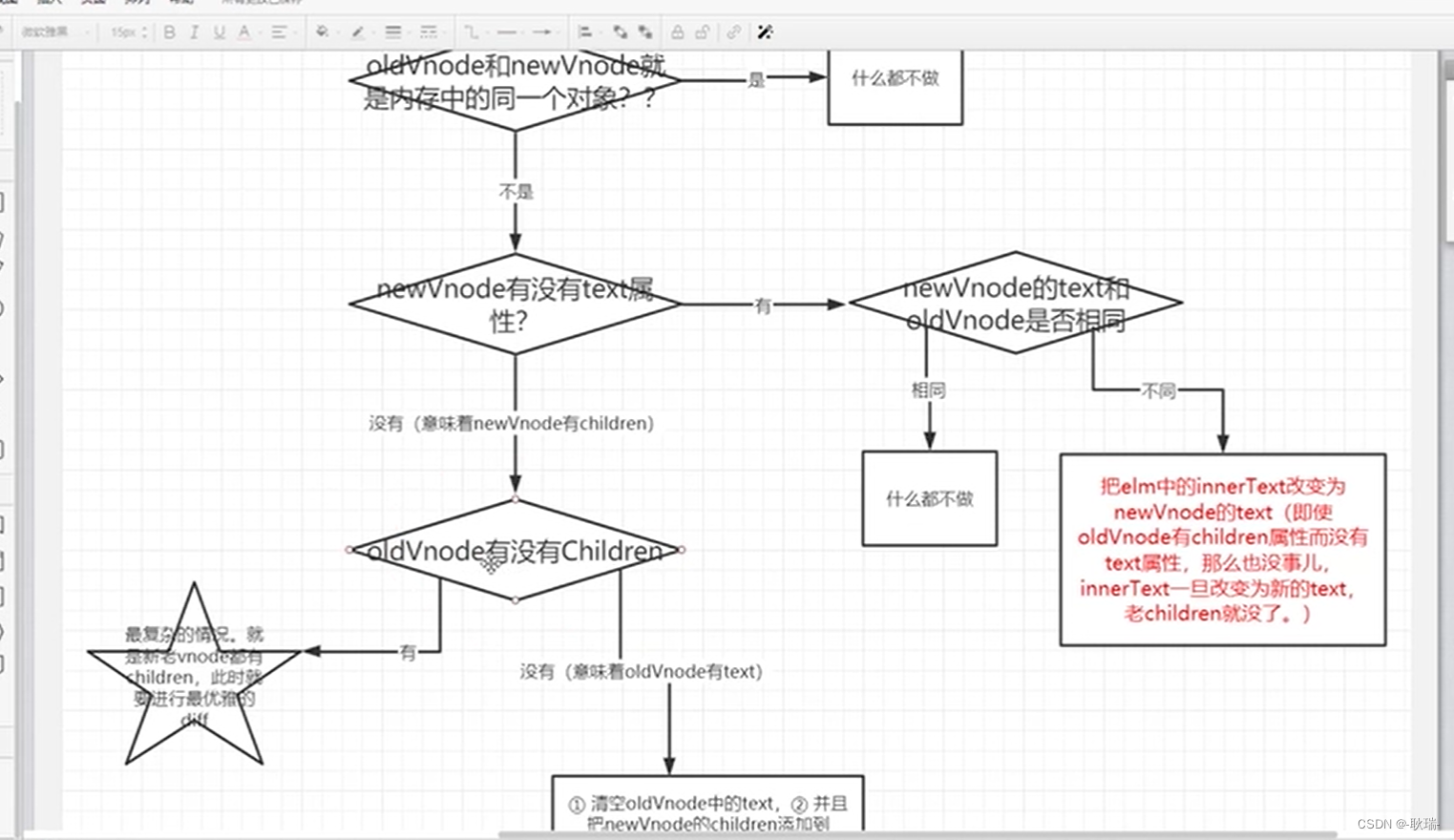

1、排序算法(组合逻辑实现)

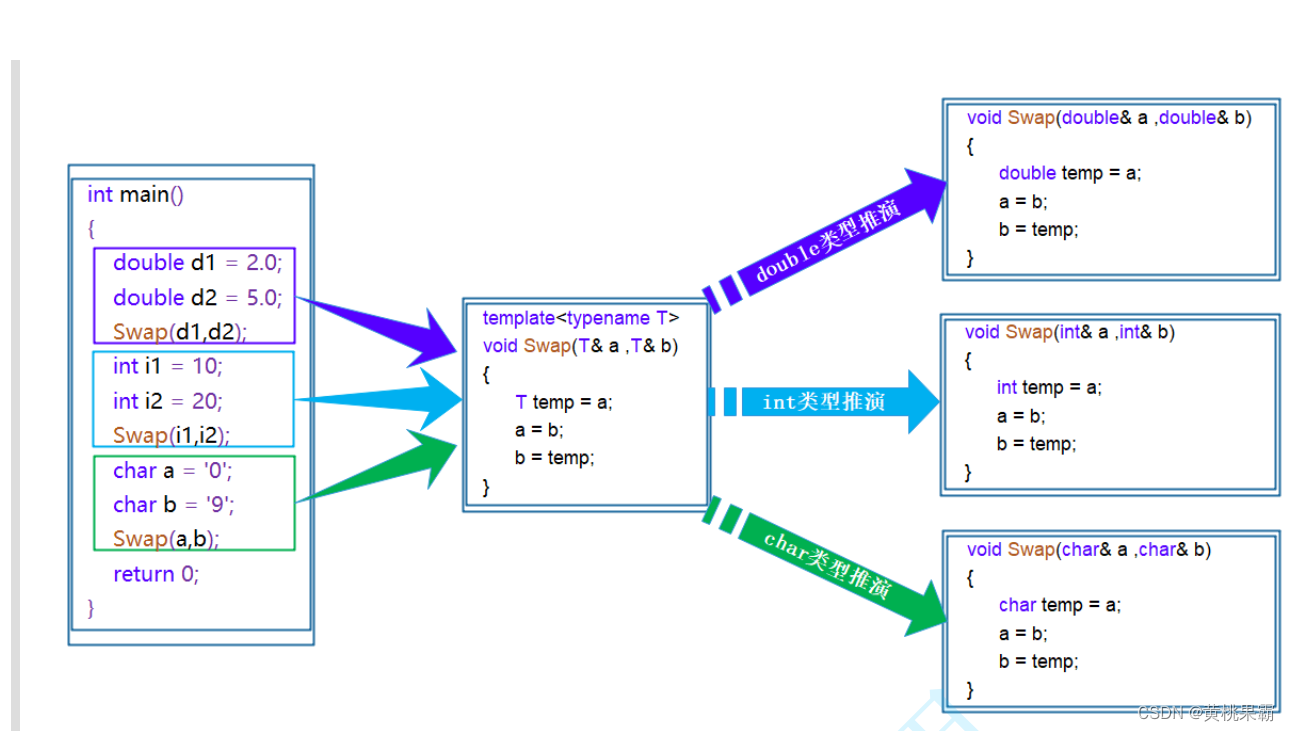

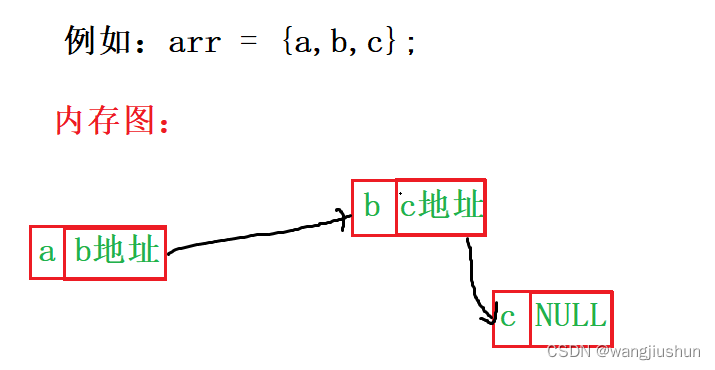

①通过for循环实现串行数据转换并行数据,用于下一级模块的比较,此处使用i计数;

②将i从最大值递减,确保当前矩阵最后一个数据输入;

③引入j,用于相邻的两组数据输入比较,将较小值赋值给中间值,进入下一级循环

integer i, j;

always@(*)

begin

for (i = 0; i < MATRIX_DATA_NUM; i = i + 1)

begin

image_array[i+1] = i_image_matrix_data[i*SIGNAL_DATA_WIDTH +: SIGNAL_DATA_WIDTH];

end

for (i = MATRIX_DATA_NUM; i > 0; i = i - 1)

begin

for (j = 1 ; j < i; j = j + 1)

begin

if (image_array[j] < image_array[j + 1])

begin

image_sort_temp = image_array[j];

image_array[j] = image_array[j + 1];

image_array[j + 1] = image_sort_temp;

end

end

end

end

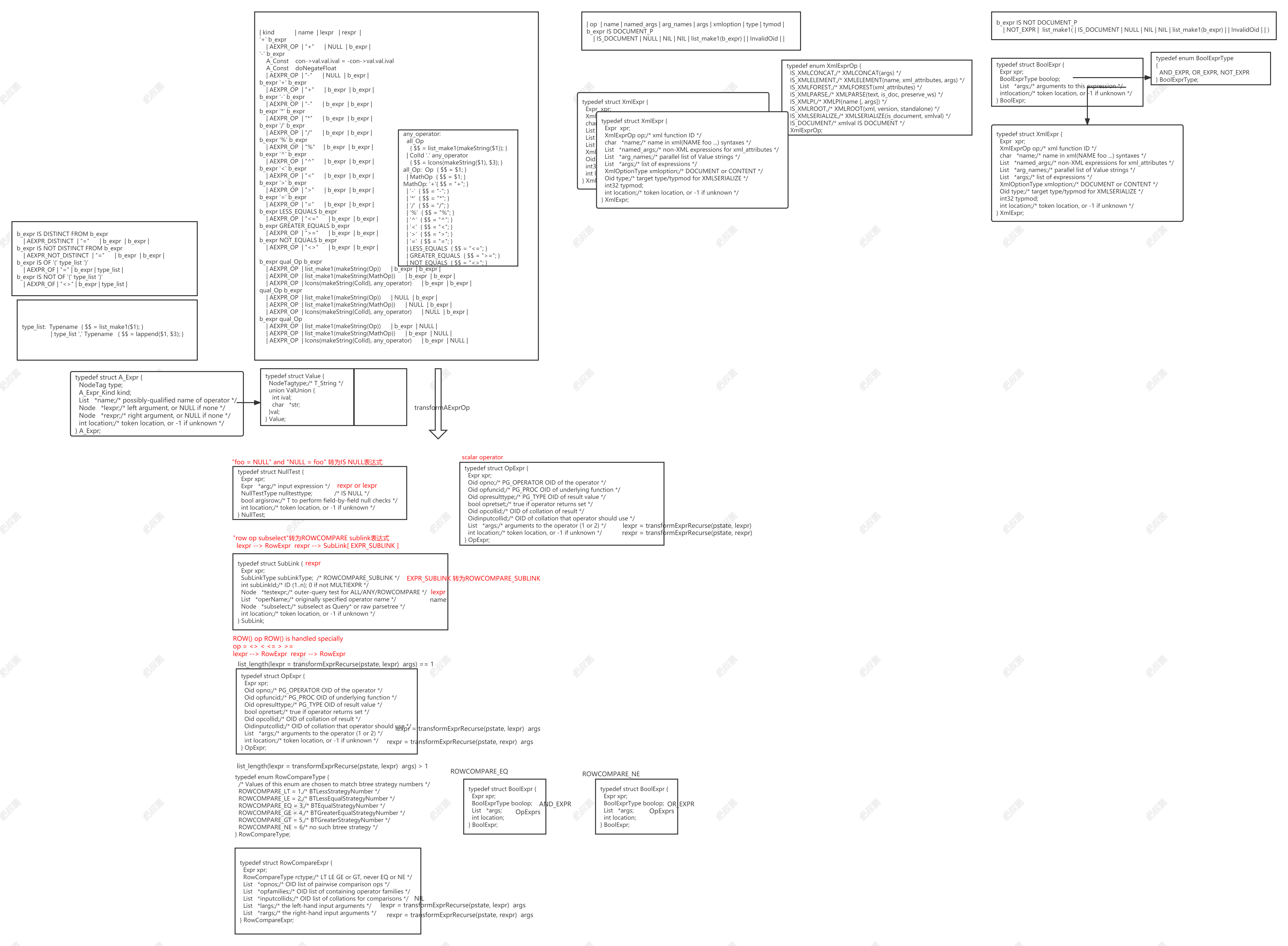

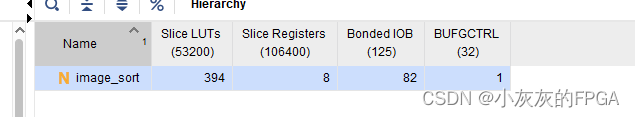

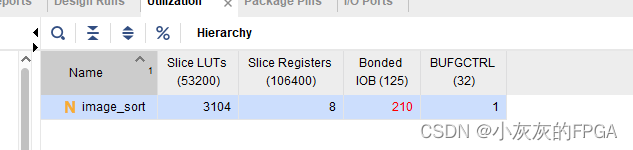

2、不同算子模块的资源比较

3x3算子模块的中值排序资源使用

5x5算子模块的中值排序资源使用

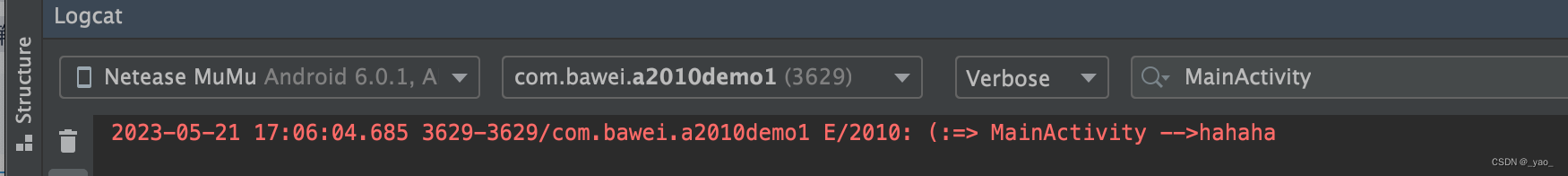

3、中值排序算法仿真验证

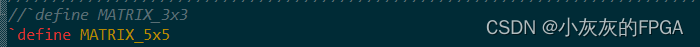

`ifdef MATRIX_3x3

parameter MATRIX_DATA_NUM = 9 ;

parameter SIGNAL_DATA_WIDTH = 8 ;

parameter MATRIX_DATA_WIDTH = SIGNAL_DATA_WIDTH * MATRIX_DATA_NUM ;

reg [MATRIX_DATA_WIDTH-1:0] i_image_matrix_data ;

wire [SIGNAL_DATA_WIDTH-1:0] o_image_median_data ;

initial begin

#(CLK_PERIOD_50M * 10000);

i_image_matrix_data = { 8'd31,8'd22,8'd23,

8'd24,8'd25,8'd26,

8'd27,8'd28,8'd39};

#(CLK_PERIOD_50M * 1000);

i_image_matrix_data = { 8'd51,8'd42,8'd43,

8'd44,8'd45,8'd46,

8'd47,8'd48,8'd59};

#(CLK_PERIOD_50M * 1000);

$stop;

end

`endif

`ifdef MATRIX_5x5

parameter MATRIX_DATA_NUM = 25 ;

parameter SIGNAL_DATA_WIDTH = 8 ;

parameter MATRIX_DATA_WIDTH = SIGNAL_DATA_WIDTH * MATRIX_DATA_NUM ;

reg [MATRIX_DATA_WIDTH-1:0] i_image_matrix_data ;

wire [SIGNAL_DATA_WIDTH-1:0] o_image_median_data ;

initial begin

#(CLK_PERIOD_50M * 10000);

i_image_matrix_data = { 8'd31,8'd22,8'd23,8'd42,8'd13,

8'd24,8'd25,8'd26,8'd55,8'd2,

8'd27,8'd28,8'd39,8'd68,8'd3,

8'd12,8'd38,8'd49,8'd78,8'd59,

8'd17,8'd15,8'd99,8'd18,8'd9};

#(CLK_PERIOD_50M * 1000);

i_image_matrix_data = { 8'd31,8'd22,8'd23,8'd42,8'd13,

8'd84,8'd25,8'd26,8'd55,8'd2,

8'd87,8'd78,8'd29,8'd68,8'd3,

8'd85,8'd71,8'd89,8'd78,8'd59,

8'd82,8'd72,8'd88,8'd18,8'd9};

#(CLK_PERIOD_50M * 1000);

$stop;

end

`endif

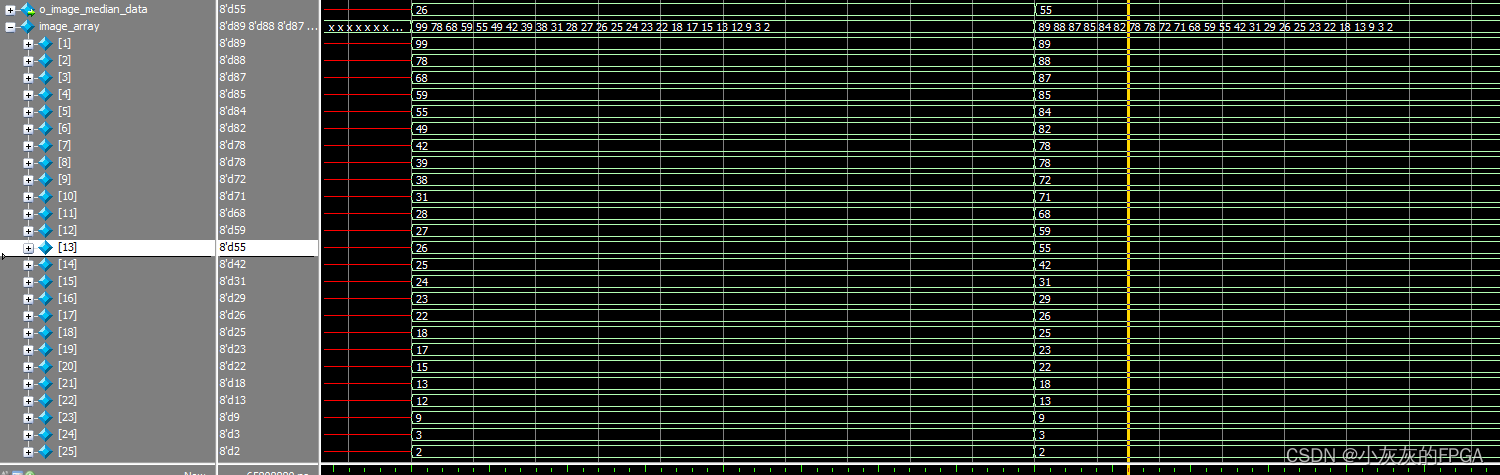

仿真结果