第5关:32位快速加法器设计

实验目的

帮助学生理解成组进位产生函数,成组进位传递函数的概念,熟悉 Logisim 平台子电路的概念,能利用前述实验封装好的4位先行进位子电路以及4位快速加法器子电路构建16位、32位、64位快速加法器,并能利用相关知识分析对应电路的时间延迟,理解电路并行的概念。

视频讲解

实验内容

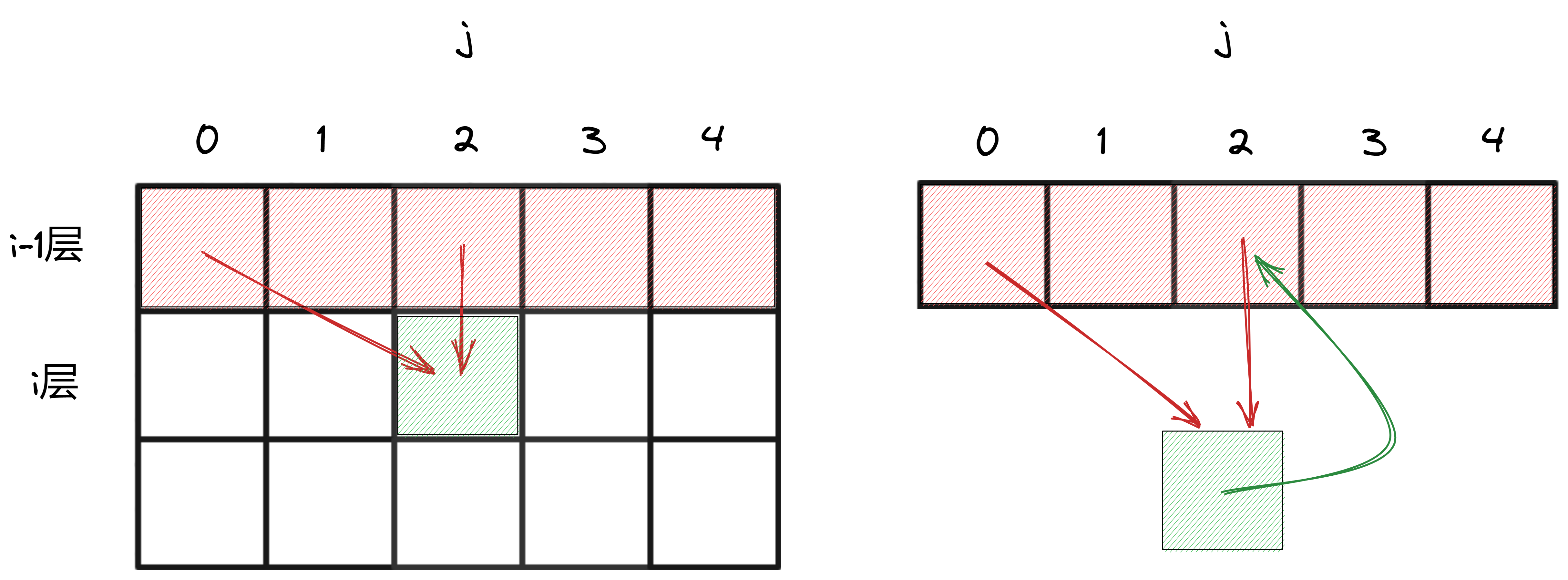

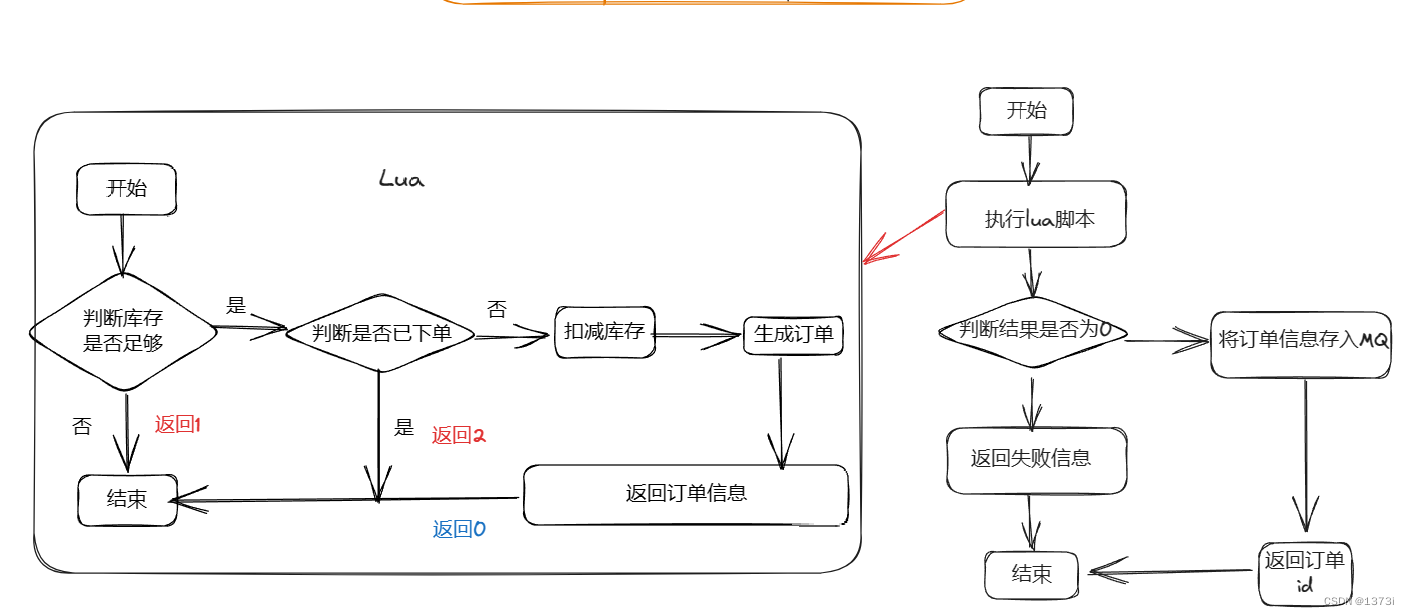

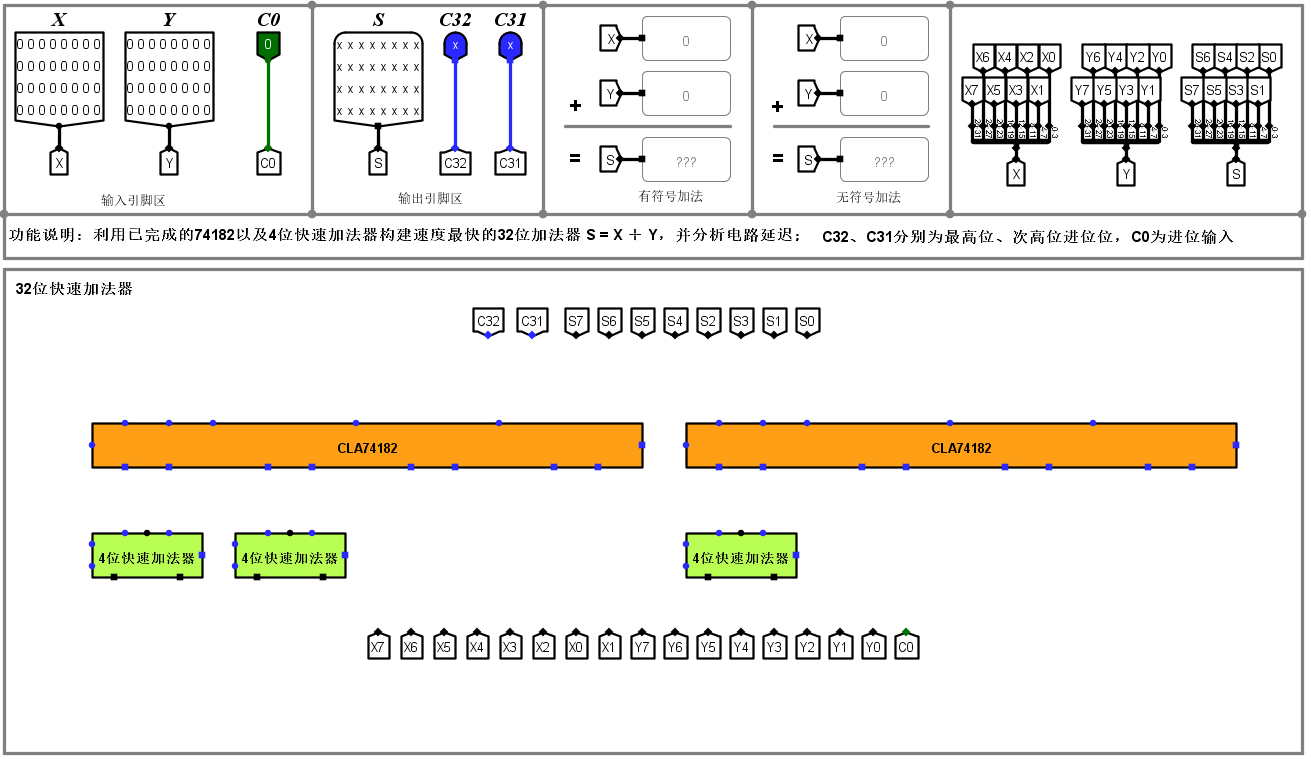

利用16位快速加法器以及先行进位电路构建32位快速加法器,并探讨其时间延迟。 可能方案:(1)2个16位加法器直接串联,C16 信号采用下层的进位输出;(2))2个16位加法器直接串联,C16 进位输入采用上层的进位输出;(3)在16位快速加法器的基础上再增加一级组间先行进位电路,类似64位快速加法器的方法;分别分析3种不同方案可能的总延迟,选择速度最快的方案实现32位快速加法器,并分析其时间延迟,其引脚如图所示。其中 X,Y 为32位相加数,Cin 为进位输入,S 为和数输出,Cout 为进位输出,Overflow 为有符号加法运算溢出信号。

电路框架

alu.circ

电路引脚

| 信号 | 输入/输出 | 位宽 | 说明 |

|---|---|---|---|

| X | 输入 | 32位 | 加数 |

| Y | 输入 | 32位 | 加数 |

| C0 | 输入 | 1位 | 进位输入 |

| S | 输出 | 32位 | 运算和 |

| C32 | 输出 | 1位 | 最32位进位位 |

| C31 | 输出 | 1位 | 第31位进位位 |

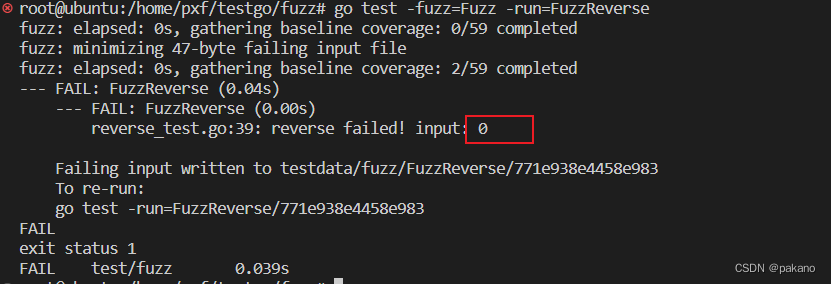

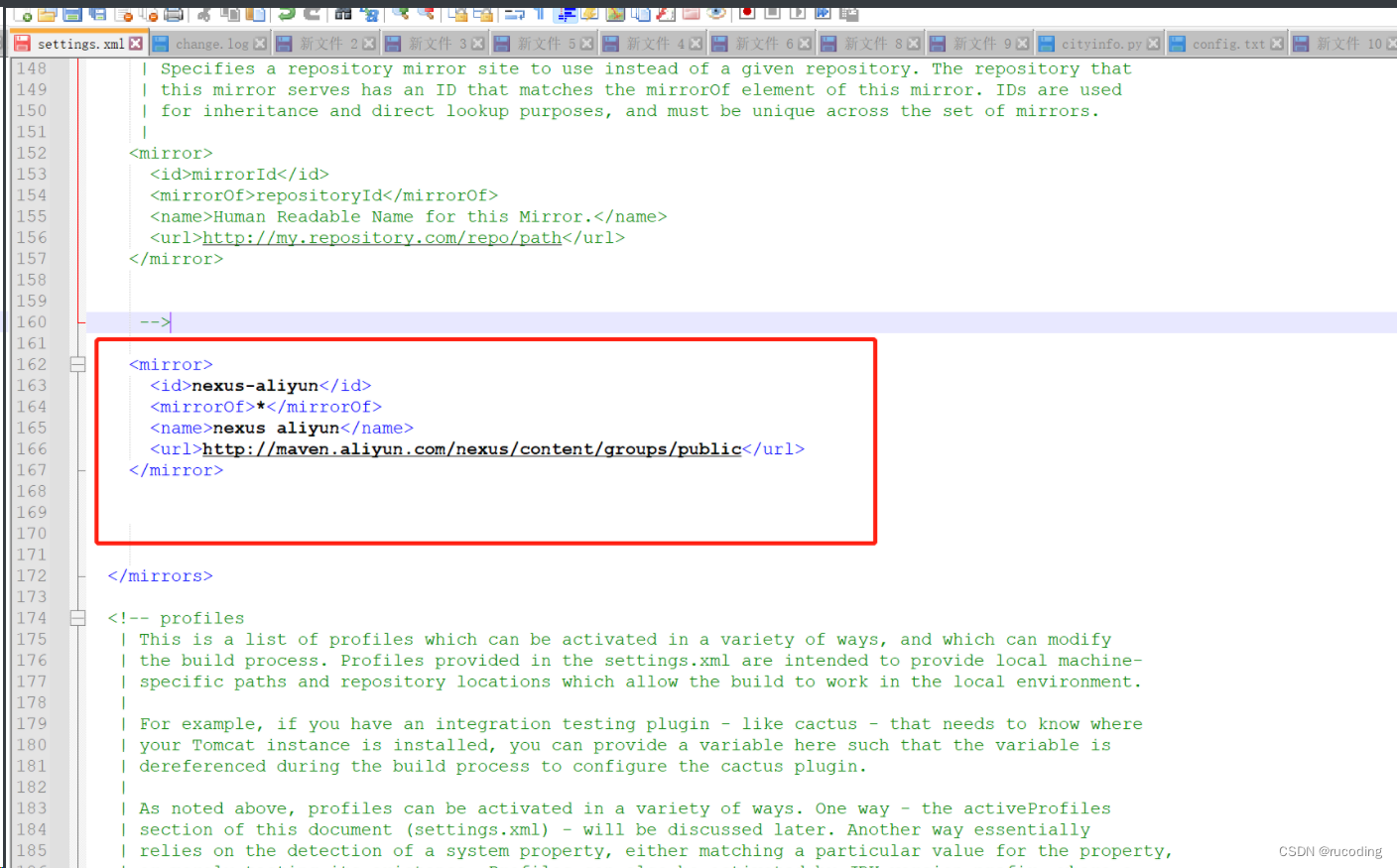

电路测试

完成实验后,利用文本编辑工具打开 alu.circ 文件,将所有文字信息复制粘贴到 Educoder 平台的 alu.circ 文件中,再点击评测按钮即可进行本关测试。平台会对你设计的电路进行自动测试,为方便测试,请勿修改子电路封装,本关测试用例如下:

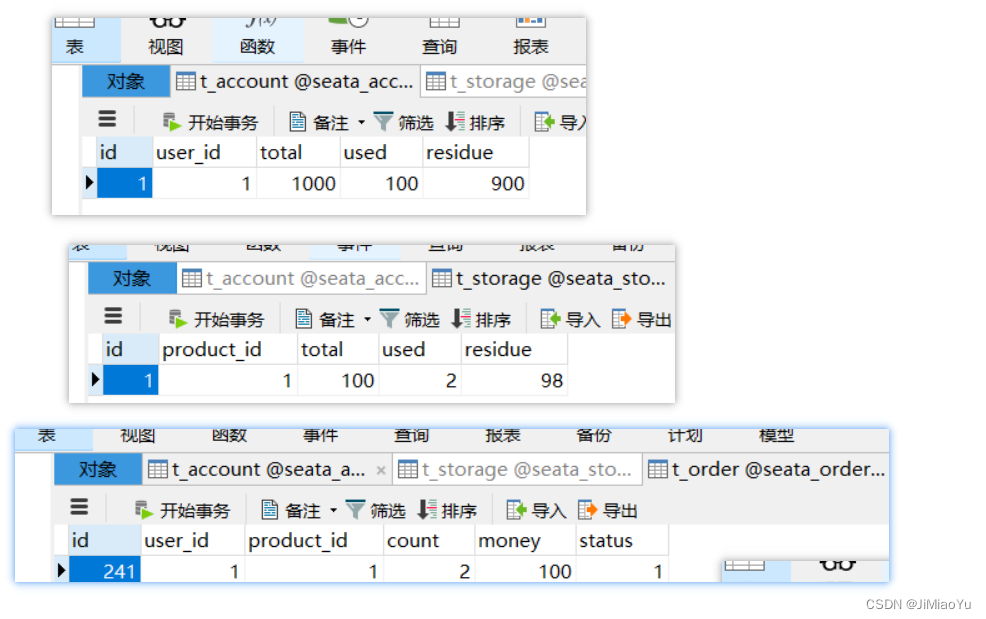

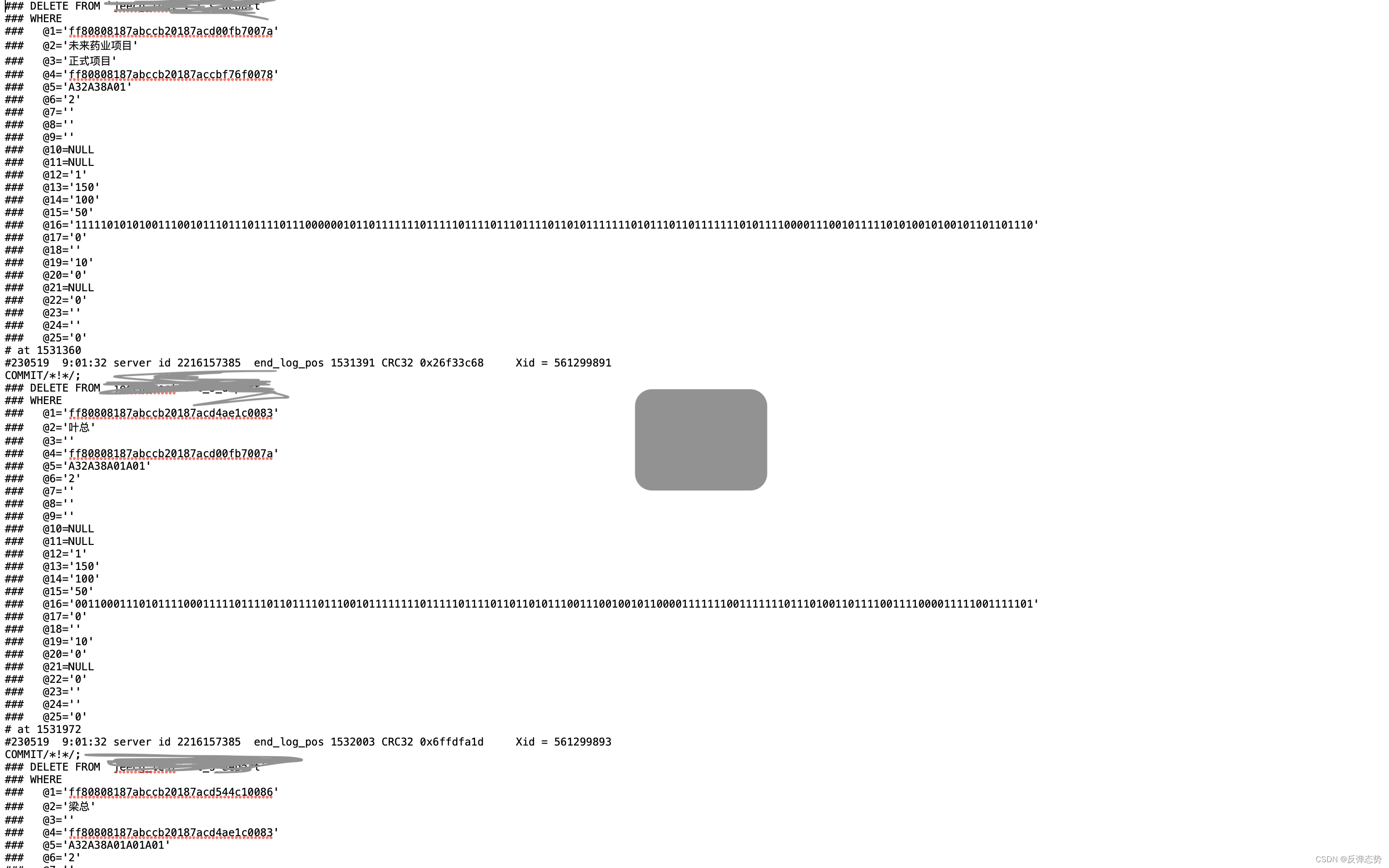

Cnt X Y C0 Sum C32 C3100 00000005 c0000003 0 c0000008 0 001 c1d5aa08 0119cc6b 1 c2ef6774 0 002 fe41a0e1 9a2b14e0 1 986c5bc2 1 103 da405843 c728b6ea 0 a169f02d 1 104 3d1c7a2a 9fad949e 0 dccae0c8 0 005 b5b838da b59899a2 1 6b502d7d 1 006 89585d86 ce717451 0 57c91dd7 1 007 e4f4bad8 ed64e090 0 d259b968 1 108 72560570 094220bc 0 7b98622c 0 0...

开始你的闯关任务吧,升级打怪中....

参考答案:

直接复制代码,字数太多,发不了,后续会上传文件

参考电路图

如果对你有所帮助,感谢点赞加收藏!

完整的代码可以到【WRITE-BUG数字空间】我的个人学习圈查看。

附上链接:

https://www.writebug.com/article/1cb43ede-f627-11ed-ada1-0242ac1a0006![]() https://www.writebug.com/article/1cb43ede-f627-11ed-ada1-0242ac1a0006

https://www.writebug.com/article/1cb43ede-f627-11ed-ada1-0242ac1a0006

关于接下来的实验内容,我也会在【WRITE-BUG数字空间】更新,也可以为大家带来更好的观感,带来更多的分享,欢迎大家前来浏览。