目录

1.ARM产品系列

2.体系结构

3.ARM指令集

定义:

ARM的指令集:

4.编译原理

5.ARM存储模型

6.ARM的8种工作方式

ARM(Advanced RISC Machines)有三种含义 一个公司的名称、一类处理器的通称、一种技术,我们在这里主要介绍ARM作为处理器。

1.ARM产品系列

早先经典处理器:包括ARM7、ARM9、ARM11家族

Cortex-A系列:对开放式操作系统的高性能处理器,应用于智能手机、数字电视、智能本等高端运用

Cortex-R系列:针对实时系统、满足实时性的控制需求应于汽车制动系统、动力系统等

Cortex-M系列:为单片机驱动的系统提供了低成本优化方案,应用于传统的微控制器市场、智能传感器、汽车周边等

2.体系结构

RISC处理器:

只保留常用的的简单指令,硬件结构简单,复杂操作一般通过简单指令的组合实现,一般指令长度固定,且多为单周期指令,RISC处理器在功耗、体积、价格等方面有很大优势,所以在嵌入式移动终端领域应用极为广泛。

CISC处理器:

不仅包含了常用指令,还包含了很多不常用的特殊指令,硬件结构复杂,指令条数较多,一般指令长度和周期都不固定,CISC处理器在性能上有很大优势,多用于PC及服务器等领域。

SOC:

SoC的定义多种多样,由于其内涵丰富、应用范围广,很难给出准确定义。一般说来, SoC称为系统级芯片,也有称片上系统,意指它是一个产品,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容。同时它又是一种技术,用以实现从确定系统功能开始,到软/硬件划分,并完成设计的整个过程。

3.ARM指令集

定义:

指令:

能够指示处理器执行某种运算的命令称为指令(如加、减、乘 ...), 指令在内存中以机器码(二进制)的方式存在,每一条指令都对应一条汇编,程序是指令的有序集合,简单来说就是把运算命名便于理解

指令集:

处理器能识别的指令的集合称为指令集,不同架构的处理器指令集不同,指令集是处理器对开发者提供的接口

ARM的指令集:

大多数ARM处理器都支持两种指令集:ARM指令集与Thumb指令集

ARM指令集:

所有指令(机器码)都占用32bit存储空间,代码灵活度高、简化了解码复杂度,执行ARM指令集时PC值每次自增4

Thumb指令集:

所有指令(机器码)都占用16bit存储空间,代码密度高、节省存储空间,执行Thumb指令集时PC值每次自增2。

4.编译原理

机器码(二进制)是处理器能直接识别的语言,不同的机器码代表不同的运算指令,处理器能够识别哪些机器码是由处理器的硬件设计所决定的,不同的处理器机器码不同,所以机器码不可移植

汇编语言是机器码的符号化,即汇编就是用一个符号来代替一条机器码,所以不同的处理器汇编也不一样,即汇编语言也不可移植

C语言在编译时我们可以使用不同的编译器将C源码编译成不同架构处理器的汇编,所以C语言可以移植

5.ARM存储模型

ARM数据类型:

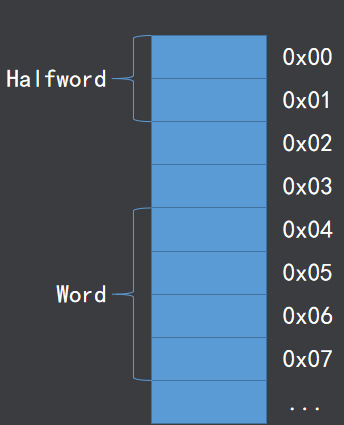

ARM采用32位架构,基本数据类型有以下三种:

- Byte 8bits -> 1个字节

- Halfword 16bits ->2个字节

- Word 32bits ->4个字节

数据存储:

Word型数据在内存的起始地址必须是4的整数倍

Halfword型数据在内存的起始地址必须是2的整数倍

注:即数据本身是多少位在内存存储时就应该多少位对齐,如下图所示。如果把Word类型数据存放的首地址为0x03是错误的。

字节序:

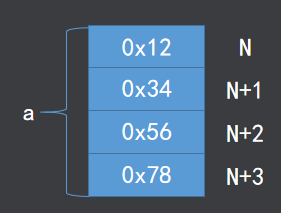

大端对齐:低地址存放高位,高地址存放低位 设a = 0x12345678,则大端对齐示意图如下

小端对齐:低地址存放低位,高地址存放高位 a = 0x12345678,小端对齐示意图如下

ARM一般使用小端对齐

ARM指令存储:

处理器处于ARM状态时:

所有指令在内存的起始地址必须是4的整数倍,因为4的整数倍转换为2进制后,其后两位的数都为0,所以ARM状态的处理器会默认起始地址的后两位为0,例如你指令的地址是0x07,转换为2进制数为0111,而ARM状态会默认其二进制的后两位为0,所以内存寻找的地址的二进制就是0100也就是0x04的地址。所以PC值由其[31:2]决定,[1:0]位未定义 。

处理器处于Thumb状态时:

所有指令在内存的起始地址必须是2的整数倍,原理同ARM状态,所以PC值由其[31:1]决定,[0]位未定义

6.ARM的8种工作方式

ARM有8个基本的工作模式:

- User 非特权模式,一般在执行上层的应用程序时ARM处于该模式

- FIQ 当一个高优先级中断产生后ARM将进入这种模式

- IRQ 当一个低优先级中断产生后ARM将进入这种模式

- SVC 当复位或执行软中断指令后ARM将进入这种模式

- Abort 当产生存取异常时ARM将进入这种模式

- Undef 当执行未定义的指令时ARM将进入这种模式

- System 使用和User模式相同寄存器集的特权模式

- Monitor 为了安全而扩展出的用于执行安全监控代码的模式

不同模式拥有不同权限 不同模式执行不同代码 不同模式完成不同的功能

工作模式分类:

按照权限:User为非特权模式(权限较低),其余模式均为特权模式(权限较高)

按照状态: FIQ、IRQ、SVC、Abort、Undef属于异常模式,即当处理器遇到异常后 会进入对应的模式

7.ARM寄存器组织

寄存器:寄存器是处理器内部的存储器,没有地址

作用:一般用于暂时存放参与运算的数据和运算结果

分类:包括通用寄存器、专用寄存器、控制寄存器

ARM的寄存器图示:

在Cortex版本中,ARM一共拥有40个寄存器,上图中左下角带小三角形的寄存器表示在该列的模式下的专用寄存器,其余的普通寄存器为全模式公用,一个模式下的专用寄存器在其余模式下是不可用的

常用的寄存器:

R15(PC,Program Counter):程序计数器,用于存储当前取址指令的地址

R14(LR,Link Register):链接寄存器,一般有以下两种用途:

- 执行跳转指令(BL/BLX)时,LR会自动保存跳转指令下一条指令的地址,程序需要返回时将LR的值复制到PC即可实现

- 产生异常时,对应异常模式下的LR会自动保存被异常打断的指令的下一条指令的地址,异常处理结束后将LR的值复制到PC可实现程序返回

R13(SP,Stack Pointer):栈指针,用于存储当前模式下的栈顶地址

CPSR(Current Program Status Register):当前程序状态寄存器,CPSR寄存器分为四个域,[31:24]为条件域用F表示、[23:16]为状态域用S表示、[15:8]为预留域用X表示、[8:0]为控制域用C表示 ,图示如下:

各主要位置的作用:

Bit[4:0] :不同的电平组合表示不同的模式,[10000]User [10001]FIQ [10010]IRQ [10011]SVC [10111]Abort [11011]Undef [11111]System [10110]Monitor

Bit[5]:[0]ARM状态 [1]Thumb状态

Bit[6]:[0]开启FIQ [1]禁止FIQ

Bit[7]:[0]开启IRQ [1]禁止IRQ

Bit[28](V):

- 当运算器中进行加法运算且产生符号位进位时该位自动置1,否则为0

- 当运算器中进行减法运算且产生符号位借位时该位自动置0,否则为1

Bit[29](C):

- 当运算器中进行加法运算且产生进位时该位自动置1,否则为0

- 当运算器中进行减法运算且产生借位时该位自动置0,否则为1

Bit[30](Z):当运算器中产生了0的结果该位自动置1,否则为0

Bit[31] (N):当运算器中产生了负数的结果该位自动置1,否则为0