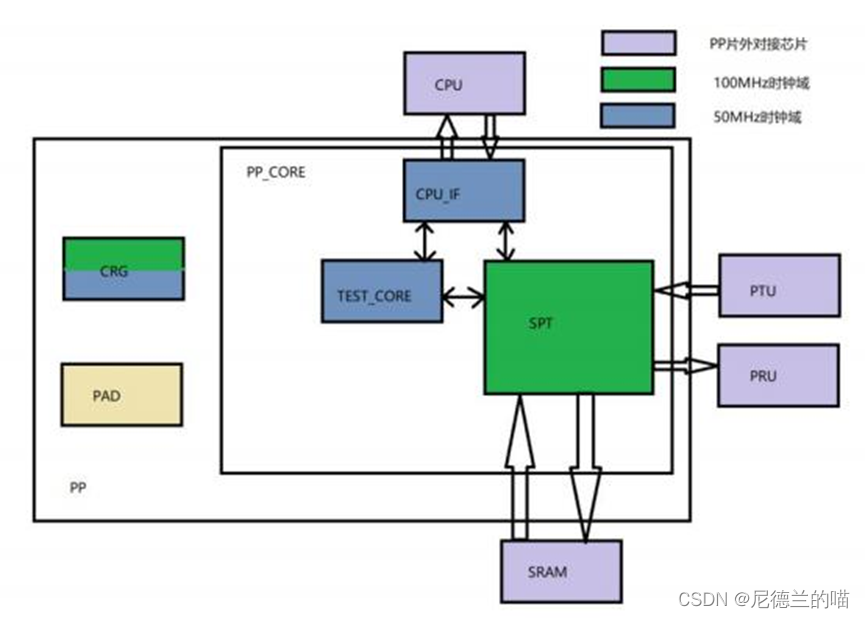

4.系统功能和主要技术指标论证

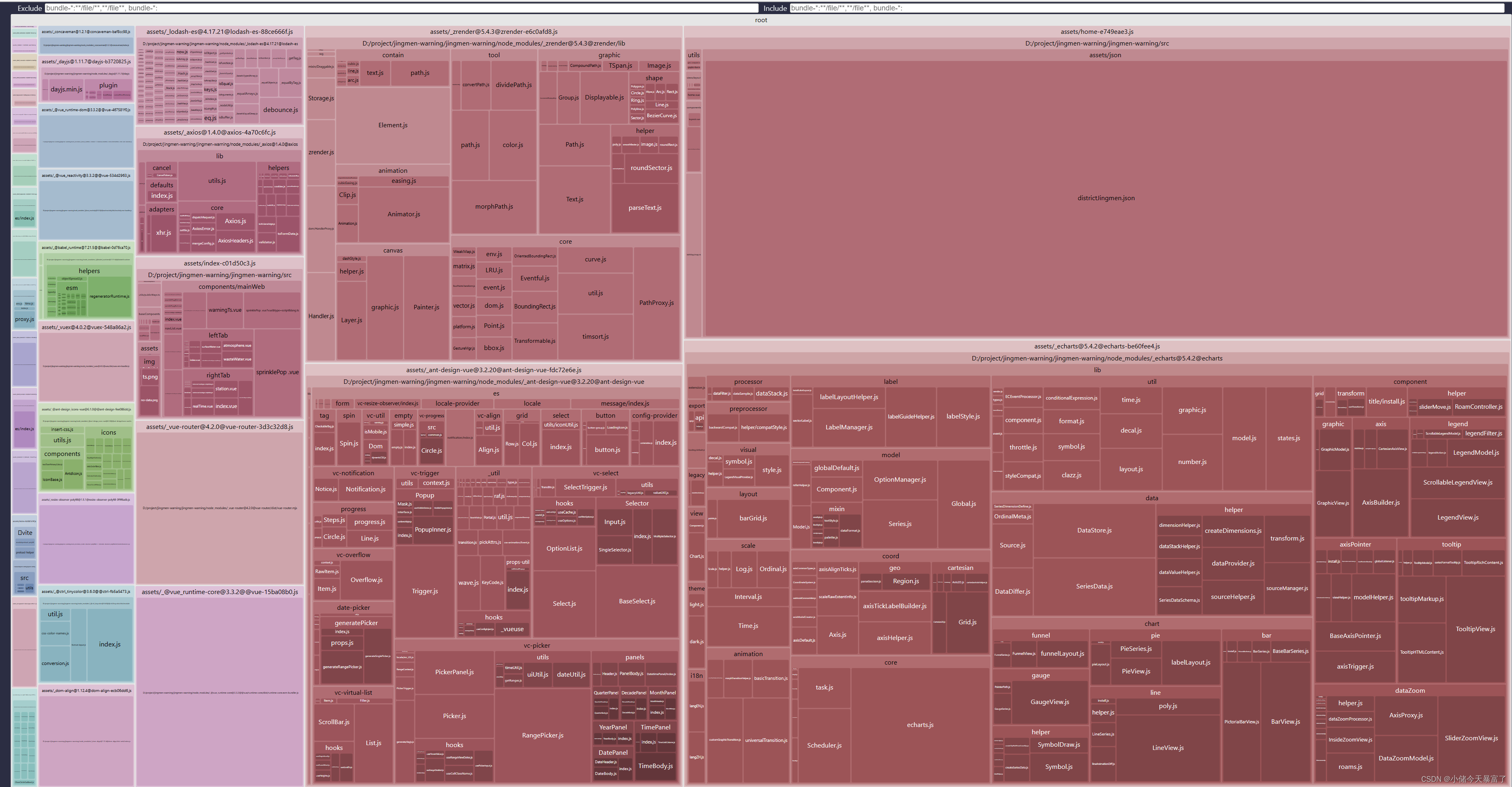

4.1芯片总体结构图

芯片总体结构框图如图2所示。

芯片内部主要电路包括 cpu_if 接口电路、sram 检测电路 test_core 以及 spt 包转发接口电 路。以下对主要部分分别进行简要介绍:

1.cpu_if 接口电路

该接口是一个异步 cpu 接口,通过 cpu_if 接口电路可向测试数据表中写入数据,进行测试数据配置;并可通过向工作模式选择寄存器写入命令字来配置芯片的工作模式——启动扫描进入扫描工作模式、结束扫描进入正常工作模式;cpu 还可以通过此接口电路读取检测状态寄存器以及统计寄存器的内容,以便掌握检测状态及结果。

2.test_core 自动检测电路

该模块根据cpu的控制,在扫描测试模式下完成对sram的扫描检测,同时将扫描结果返回给cpu_if模块。

3.spt 包转发电路

spt模块按照接口时序要求,完成接收包处理,错包丢弃、统计,以及包转发。并完成test_core模块对端口扫描的选择,对sram接口信号的处理。