FPGA是一种可编程逻辑器件,与传统的硬连线电路不同,它具有高度的可编程性和灵活性。FPGA的设计方法包括硬件设计和软件设计两部分,硬件设计包括FPGA芯片电路、存储器、输入输出接口电路等等,软件设计则是HDL程序开发,以及软硬件的联调。

本文主要介绍FPGA设计的基本流程,让大家对FPGA开发流程有一个整体的认识。

一、FPGA的基本开发流程

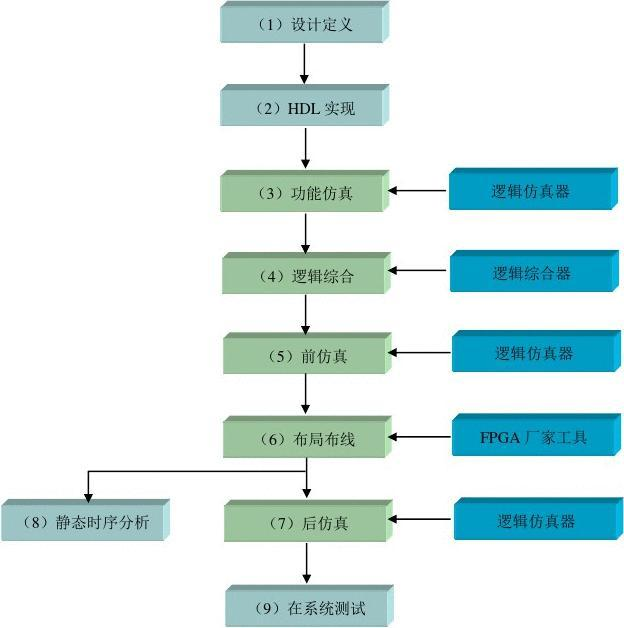

FPGA的设计流程主要包括开发需求分析、设计框架搭建、硬件电路设计、软件编程以及验证测试等多个阶段,每个阶段都需要专业的EDA开发软件和编程工具进行支持。

通过这些工具,设计人员可以对FPGA进行仿真、合成、布局布线等操作,从而实现对FPGA芯片的开发和优化。

二、具体流程介绍

1、设计定义

在FPGA设计项目开始之前,根据任务要求和系统的功能,对工作速度和器件本身的资源、成本等方面进行权衡,选择合适的设计方案和合适的器件类型,并根据功能需求来设计定义整个项目的架构设计。

架构设计的目的是将设计需求转化为硬件结构,确定模块划分、信号传输方式、时序关系等。在进行架构设计时,我们需要考虑到设计复杂度、资源利用率、功耗消耗等多个方面。

这块需要资深FPGA来设计,同时设计方案需要分析和验证,确保FPGA器件的资源和性能可以达到功能的要求,可能需要迭代多个版本,这部分需要经验积累。

2、HDL实现

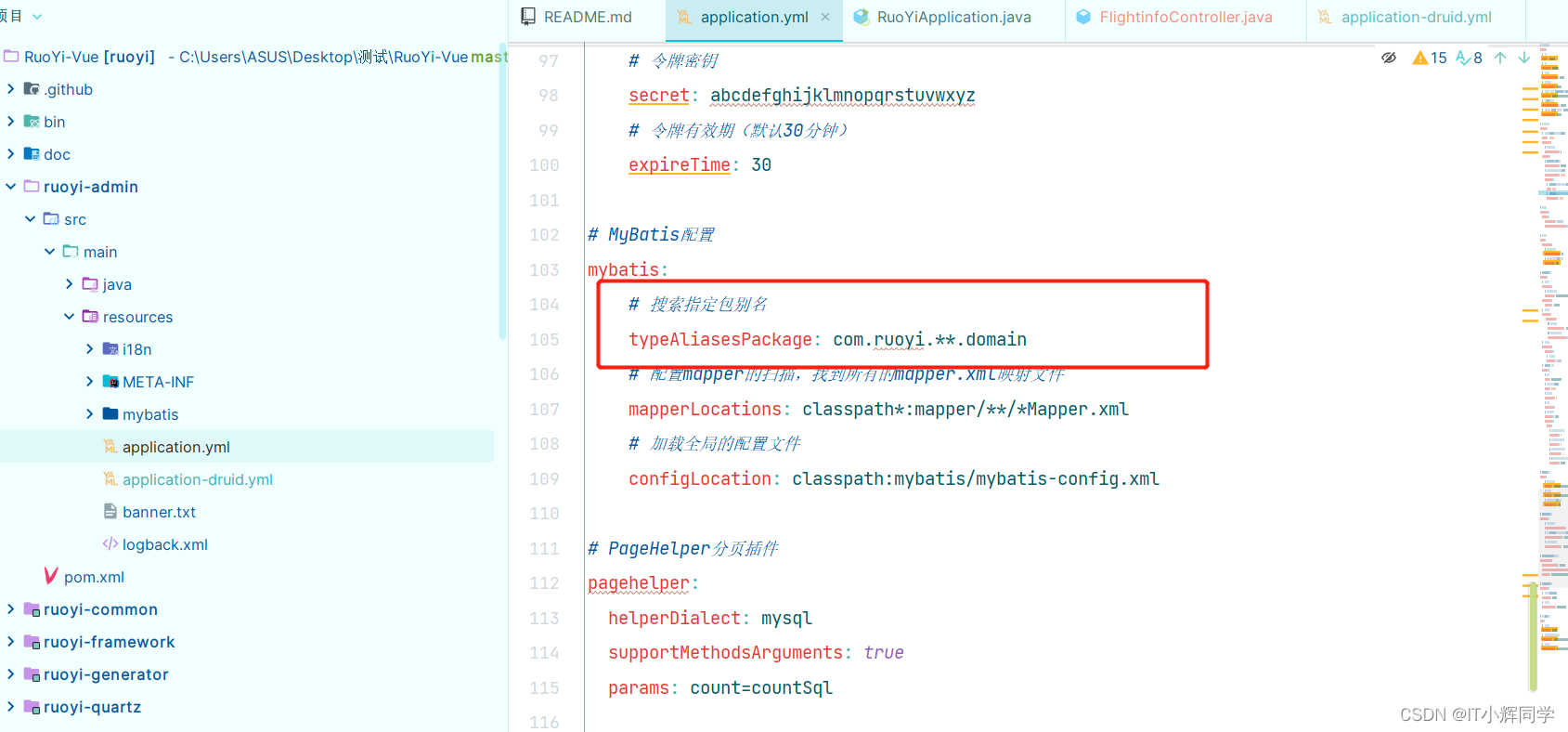

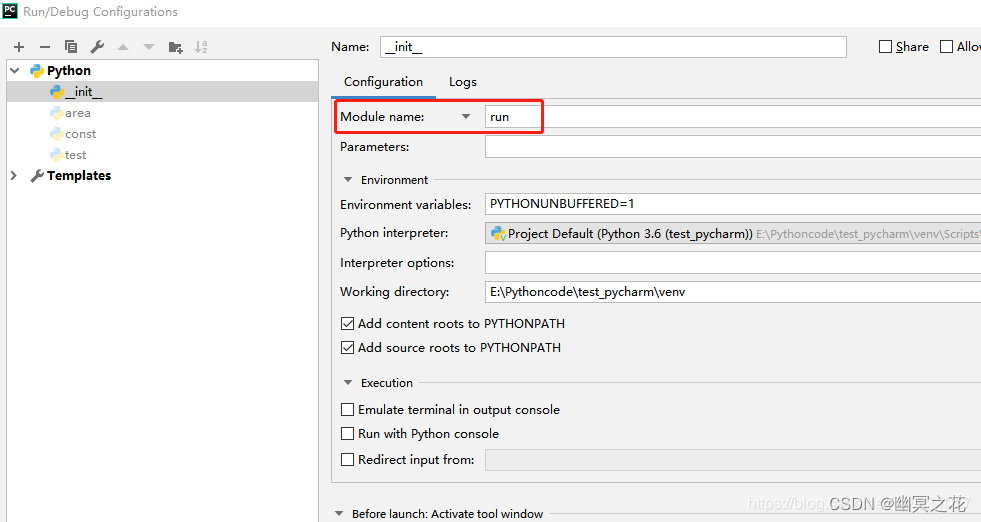

这块主要是编写代码,按照设计需求和架构设计,将功能模块拆分为各个子模块,然后编写相应的模块代码,常用HDL语言是verilog HDL和VHDL。

这部分涉及到verilog开发,推荐使用Vivado+Visual Studio Code的开发环境,写起代码来还是很方便的。

3、功能仿真

功能仿真,是在编译之前进行逻辑功能验证的过程,主要用来验证。

此时的仿真没有考虑电路的延迟信息,只能对逻辑功能进行检测,并不能保证上板运行的正确性。

功能仿真需要编写测试激励,需要根据要测试的功能,来编写测试激励逻辑。

功能仿真是一种非常重要的验证手段,可以尽早发现设计中的问题和错误,从而减少后期的调试和修改工作。

常用的仿真软件有Vivado自带仿真器和modelsim仿真器,其中modelsim仿真速度比Vivado仿真速度快,推荐使用modelsim仿真。

4、 逻辑综合

综合(Synthesis)是将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表的过程。综合的目标是将较高级的抽象描述转化成较低层次的描述,并进行优化,以提高电路的性能和效率。

综合优化根据目标和要求来优化所生成的逻辑连接,使层次设计平面化,为FPGA布局布线软件提供实现支持。

综合的时间,与FPGA工程大小有关,工程越复杂,时间则越长。

5、综合后仿真

综合后仿真,主要是检查综合结果是否和原设计一致,但这个仿真很耗时和耗资源,一般可以跳过这个仿真,不如直接上板调试来的靠谱

6、实现与布局布线

这步是FPGA设计流程中非常重要的一步,可以将综合生成的逻辑网表配置到具体的FPGA芯片,同时也是耗时特别长的一个阶段。

布局布线根据时序约束条件,以及芯片内部各个逻辑单元的布局结构,通过连线资源,将逻辑网表中的硬件原语和底层单元合理地配置到芯片内部的固有硬件结构上,这部分往往需要在速度优化和面积优化之间找平衡。

可以在开发软件上,设置实现和布局布线策略,一般情况下使用默认设置即可。

7、 时序仿真

时序仿真,也称为后仿真,主要检测布局布线后的电路是否有时序不满足的情况。这块一般用的少,建议直接略过这一步,上板调试更好。

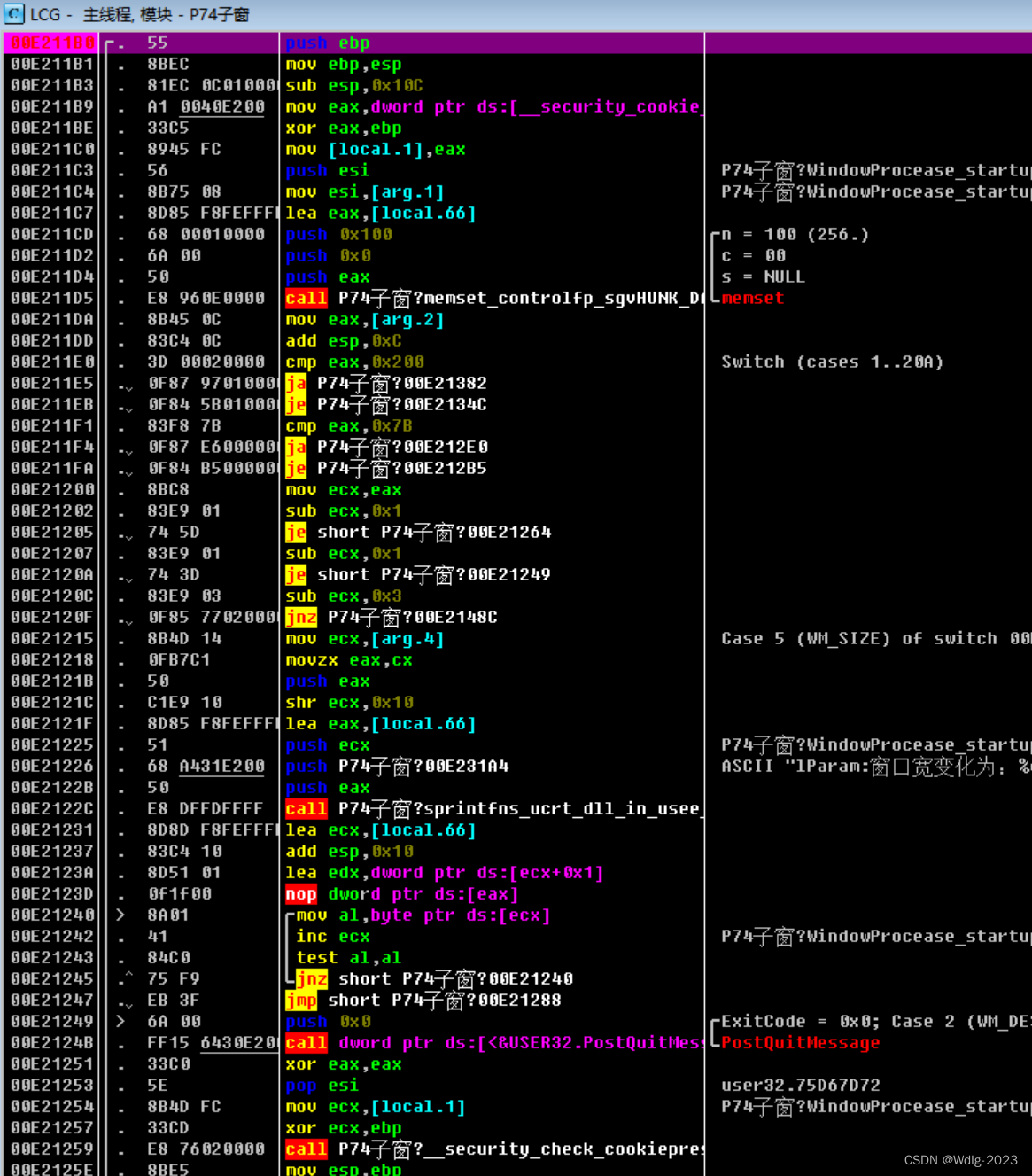

8、上板调试

一般是通过JTAG在线下在bit文件到FPGA芯片中,接入实际的输入信号,在线实时测试,这里在第一次测试时,大概率会运行异常。

我们调试的时候,要保持耐心,要根据现象大胆推荐可能的原因,并将存在问题的模块信号,加入ILA,抓取实时信号出来分析,如果实在是没哟头绪,那就只要一个个模块排查,猜测可能的原因。

上板调试经验,需要不断积累,做项目越多,越熟练,注意总结和复盘。

三、总结

FPGA设计流程包括分析设计需求、FPGA架构设计、HDL代码编写、逻辑综合、布局布线、仿真调试和生成比特流文件等步骤。这些步骤并不是一次完成的,可能需要多次迭代,反复编译和调试,才能完成项目。当然了项目经验需要不断积累的,多思考,多总结,才能进步。

本文将不断定期更新中,码字不易,点⭐️赞,收⭐️藏一下,不走丢哦

本文由FPGA入门到精通原创,有任何问题,都可以在评论区和我交流哦

学习资料分享,github开源代码:“FPGA知识库”

您的支持是我持续创作的最大动力!如果本文对您有帮助,请给一个鼓励,谢谢。