Icarus Verilog是一个轻量、免费、开源的Verilog编译器,基于C++实现,开发者是 Stephen Williams ,遵循 GNU GPL license 许可证,安装文件中已经包含 GTKWave支持Verilog/VHDL文件的编译和仿真,命令行操作方式,类似gcc编译器,通过testbench文件可以生成对应的仿真波形数据文件,通过自带的GTKWave可以查看仿真波形图,支持将Verilog转换为VHDL文件。

安装

sudo apt-get install iverilog

sudo apt-get install gtkwave

测试

rtl

add.v

module simple(A, B, C);

input [3:0] A;

input [3:0] B;

output [3:0] C;

// mix up the input bits

assign C = A&B;

endmodule

TB

tb.v

module simple_tb;

reg [3:0] A = 4’b1010;

reg [3:0] B = 4’b0101;

wire [3:0] C;

initial

begin

$dumpfile(“simple.vcd”);

$dumpvars(0, s);

$monitor(“A is %b, B is %b , C is %b.”, A, B, C);

#50 A = 4’b1100;

B = 4’b1100;

#50 $finish;

end

simple s(A, B, C);

endmodule

编译命令

两个输入文件,一个编译出来的bin

iverilog -o simple.vvp add.v tb.v

仿真

vvp simple.vvp

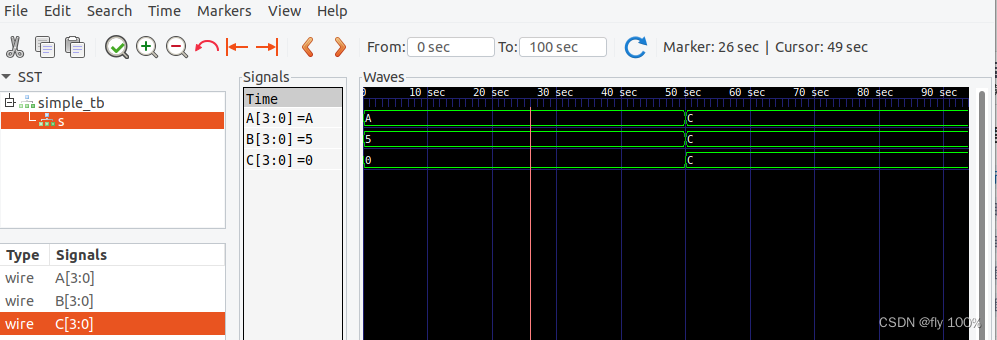

看波形

gtkwave simple.vcd