轻量化Verilog学习环境搭建

本文记录基于vscode、iverilog搭建轻量化Verilog学习环境的方法。

ref: VSCode Verilog工具链、linux下搭建轻量易用的verilog仿真环境

环境搭建

(1)安装iverilog,这是一个轻量化的开源verilog编译器,配合gtkwave可进行波形仿真。

sudo apt-get install iverilog

sudo apt-get install gtkwave

(2)安装vscode插件Verilog-HDL为verilog提供语法高亮和静态检查等基本支持。打开扩展设置,设置Verilog格式化插件和Lint插件。其中Lint插件可选iVerilog。Format插件可选Verible( 下载地址)。将Verible二进制文件解压到/usr/local/bin,并在插件设置中填好二进制文件的路径。

(3)添加一个简单的自动化脚本来自动调用iverilog,提高效率。

工程结构(下载):

verilog_learn/

├── build

│ ├── a.out

│ ├── wave.vcd

├── gtkwave.tcl

├── led_demo_tb.v

├── led_demo.v

├── run.sh

└── .vscode

└── tasks.json

run.sh:

echo "Handling: $1..." # the verilog file

source="../$1.v"

testbanch="../$1_tb.v"

# 生成波形文件

iverilog -o ./a.out $source $testbanch

vvp -n ./a.out -lxt2

# 使用gtkwave查看仿真波形

# https://blog.csdn.net/yelllowcong/article/details/78424329

isGtkWaveRunning=$(ps -ef |grep gtkwave |grep -v "grep" |wc -l)

if [ $isGtkWaveRunning -eq 0 ]; then

# echo NOT RUN

gtkwave wave.vcd --script=../gtkwave.tcl

else

# echo is RUN

echo "gtkwave is running"

# gtkwave wave.vcd

fi

# 综合并可视化网表

# yosys -p 'prep ; show -format pdf -prefix yosys' $source

# code ./yosys.pdf

其中gtkwave.tcl文件是对gtkwave进行自动化配置的脚本,内容如下:

# ref: https://gist.github.com/davidzwa/ef1eafc6cd23e613af612e27eddb054b

# ref: https://ughe.github.io/2018/11/13/gtkwave-automation

# Add all signals

set nfacs [ gtkwave::getNumFacs ]

set all_facs [list]

for {set i 0} {$i < $nfacs } {incr i} {

set facname [ gtkwave::getFacName $i ]

lappend all_facs "$facname"

}

set num_added [ gtkwave::addSignalsFromList $all_facs ]

puts "num signals added: $num_added"

# zoom full

gtkwave::/Time/Zoom/Zoom_Full

随后在vscode中新建一个task(存于.vscode/task.json路径)来自动运行run.sh,这样在xxx.v文件下按快捷键ctrl+shift+B即可执行run.sh。

{

// See https://go.microsoft.com/fwlink/?LinkId=733558

// for the documentation about the tasks.json format

"version": "2.0.0",

"options": {

// 这里指定tasks 的运行目录,默认是${workspaceRoot},也就是.vscode/..

"cwd": "${workspaceRoot}/build"

},

"tasks": [

{

// 这个task完成编译

"label": "build",

"type": "shell",

"command": "../run.sh",

"args": [

"${fileBasenameNoExtension}"

]

},

]

}

验证

添加led_demo.v及其测试脚本led_demo_tb.v

led_demo.v:

module led_demo(

input clk,

input rst_n,

output reg led

);

reg [7:0] cnt;

always @ (posedge clk)

begin

if(!rst_n)

cnt <= 0;

else if(cnt >= 10)

cnt <= 0;

else

cnt <= cnt + 1;

end

always @ (posedge clk)

begin

if(!rst_n)

led <= 0;

else if(cnt == 10)

led <= !led;

end

endmodule

led_demo_tb.v

`timescale 1ns/100ps

module led_demo_tb;

parameter SYSCLK_PERIOD = 10;

reg SYSCLK;

reg NSYSRESET;

initial

begin

SYSCLK = 1'b0;

NSYSRESET = 1'b0;

end

/*iverilog */

initial

begin

$dumpfile("wave.vcd"); //生成的vcd文件名称

$dumpvars(0, led_demo_tb); //tb模块名称

end

/*iverilog */

initial

begin

#(SYSCLK_PERIOD * 10 )

NSYSRESET = 1'b1;

#1000

$stop;

end

always @(SYSCLK)

#(SYSCLK_PERIOD / 2.0) SYSCLK <= !SYSCLK;

led_demo led_demo_ut0 (

// Inputs

.rst_n(NSYSRESET),

.clk(SYSCLK),

// Outputs

.led( led)

);

endmodule

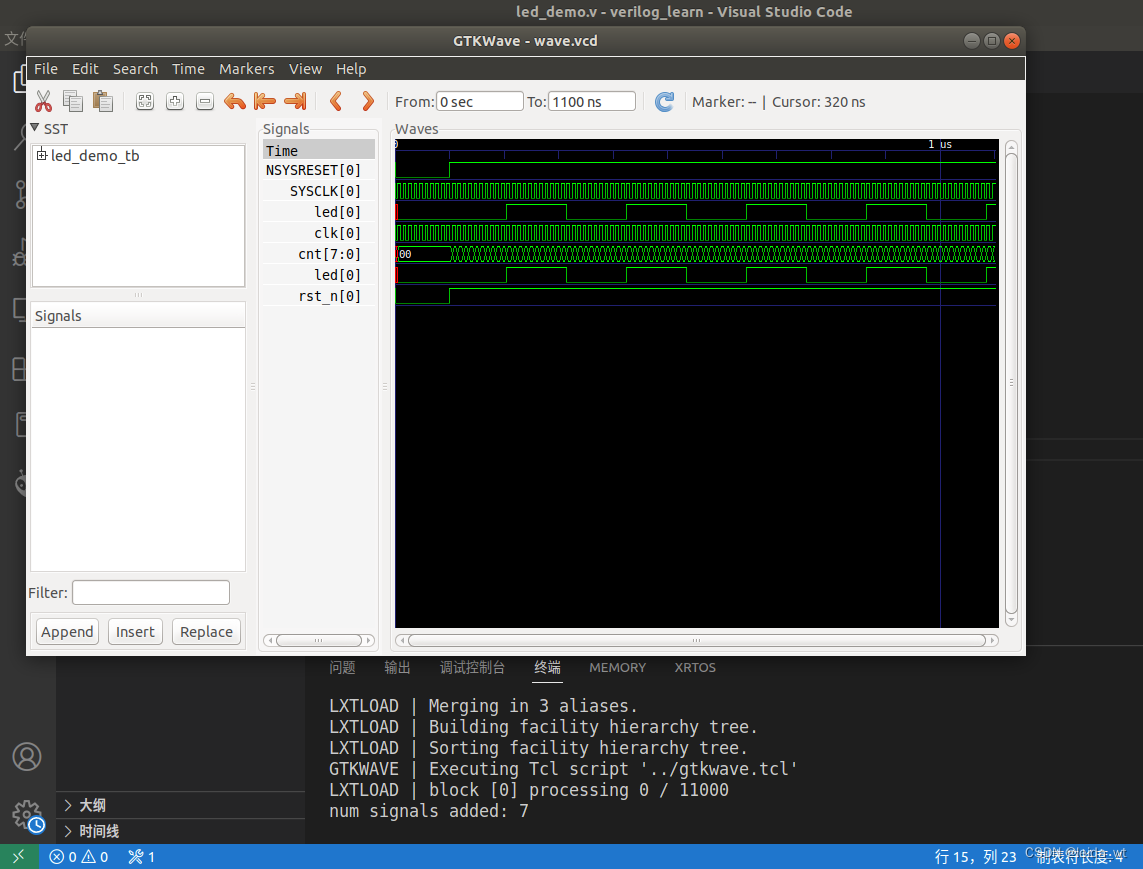

打开led_demo.v,按快捷键ctrl+shift+B,即可自动执行编译,并开启gtkwave显示仿真波形: