机缘

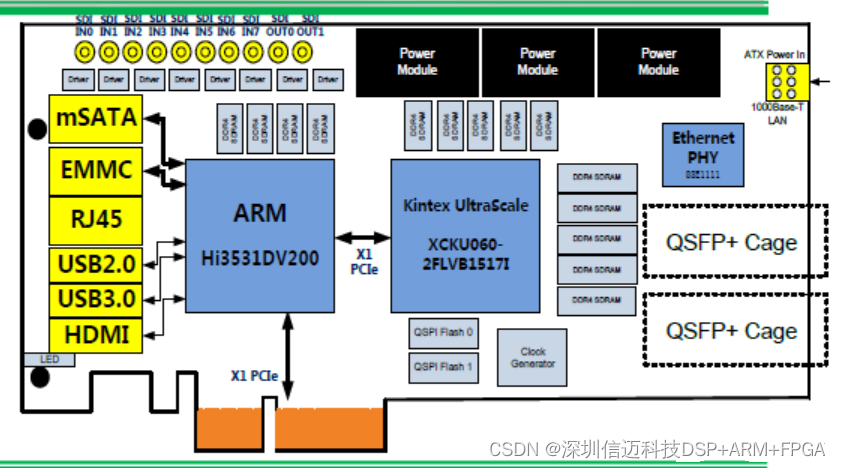

平台今天提示我已经坚持创作3年了。如果不提醒的话,我自己都没什么感觉。三年时间说长也不长,说短呢,其实也不短了。截止今天我在CSDN累计发文213篇,上传资源117个。涉及领域包含:数字信号处理、FPGA设计、IC设计验证、雷达信号处理算法仿真等。

在这篇总结中(2022 在路上~)我也提到过创作初心的问题。主要是想着记录一下自己学习的过程。有句话说的甚好:好记性不如烂笔头。在科技如此发达的今天,我选择用博客的形式延续我的学习习惯,多记录总归是好的。记录总结的时候也是自己重新反思,精进技术的好时机。除此之外我记录的博客内容也可以给同样处于学习初期的同学一些启发,一些帮助。并且可以通过私信或者评论的方式实现技术的交流。闭门造车是我所不能接受的,所以这种方式真的可以提供很好的学习交流的机会。

所以呢,在此处我也想说,各位IC/IT技术人,有博客记录习惯的咱继续保持,因为点滴技术的记录和积累,总有一天可以做到厚积薄发,成为某一领域的技术专家/大牛。那些还没有记录过博客的呢,咱要大胆迈出第一步,不要害怕你发的文章质量不够,你要知道的是发博客第一目的不是为了给别人看的,而是总结技术给自己看的。经过时间的洗涤,咱也可以从技术小白慢慢蜕变为技术牛人。加油!

收获

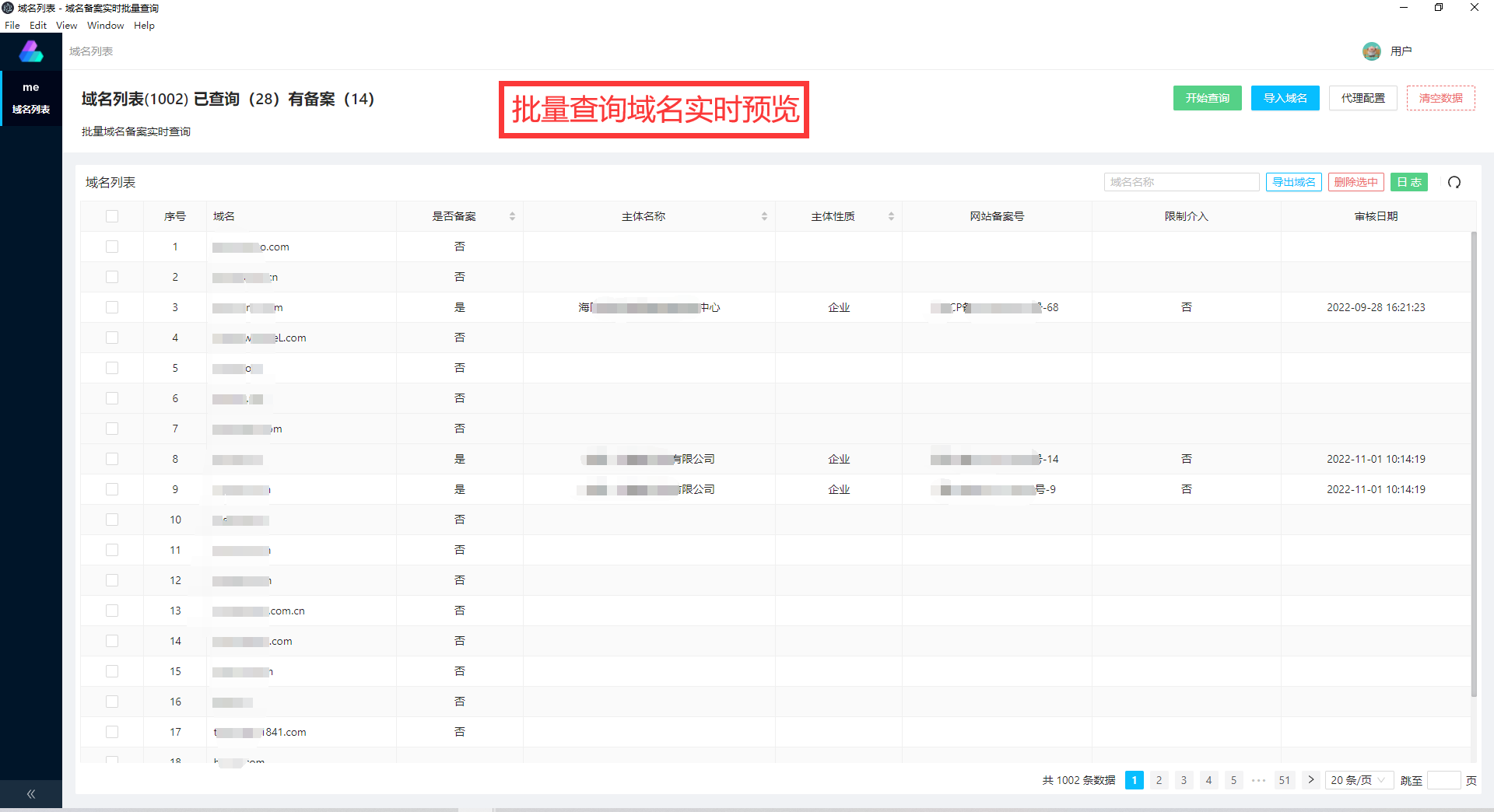

收获自然也是有的,目前平台统计的粉丝数量为8379,总访问量超过36万,文章收藏量达3285。这也会带给我很大的激励,激励我不断做更好的博客分享给大家。

另外也收到了很多交流技术以及认同我的评论:

出现此之外,也有更多的同行通过文末链接加入了我创建的技术交流群:

日常

现阶段,我还是一名在读研究生(研二)。在空闲时间还是会主动创作一些技术文章。特别是今年面临找工作的问题,可能随着自己找工作的进度也会分享一些笔试面试的经验。

我相信到未来毕业之后,在工作岗位上我也会继续坚持创作。

成就

我是一个经常写代码的人,要说写过的最好的代码是啥,我可能一时间想不出来。但最近一段时间用Verilog写过的轮询仲裁器的代码让我印象深刻。此处就把实现的代码展示一下:

原文链接,详情:联发科 2024届 IC设计验证 实习笔试分析

// ===================================================================================

// 功能:

// -1- Round Robin 仲裁器

// -2- 仲裁请求个数N可变

// -3- 加入lock机制(类似握手)

// -4- 复位时的最高优先级定为 0 ,次优先级:1 -> 2 …… -> N-2 -> N-1

// By:Xu Y. B.

// ===================================================================================

`timescale 1ns / 1ps

module Round_Robin_Arbiter #(

parameter N = 4 //仲裁请求个数

)(

input clock,

input reset_b,

input [N-1:0] request,

input [N-1:0] lock,

output reg [N-1:0] grant//one-hot

);

// 模块内部参数

localparam LP_ST_IDLE = 3'b001;// 复位进入空闲状态,接收并处理系统的初次仲裁请求

localparam LP_ST_WAIT_REQ_GRANT = 3'b010;// 等待后续仲裁请求到来,并进行仲裁

localparam LP_ST_WAIT_LOCK = 3'b100;// 等待LOCK拉低

// 模块内部信号

reg [2:0] R_STATUS;

reg [N-1:0] R_MASK;

wire [N-1:0] W_REQ_MASKED;

assign W_REQ_MASKED = request & R_MASK;

always @ (posedge clock)

begin

if(~reset_b)

begin

R_STATUS <= LP_ST_IDLE;

R_MASK <= 0;

grant <= 0;

end

else

begin

case(R_STATUS)

LP_ST_IDLE:

begin

if(|request) //首次仲裁请求

begin

R_STATUS <= LP_ST_WAIT_LOCK;

grant <= request & ((~request)+1);

R_MASK <= ~((request & ((~request)+1))-1 | (request & ((~request)+1)));

end

else

begin

R_STATUS <= LP_ST_IDLE;

end

end

LP_ST_WAIT_REQ_GRANT://处理后续的仲裁请求

begin

if(|request)

begin

R_STATUS <= LP_ST_WAIT_LOCK;

if(|(request & R_MASK))//不全为零

begin

grant <= W_REQ_MASKED & ((~W_REQ_MASKED)+1);

R_MASK <= ~((W_REQ_MASKED & ((~W_REQ_MASKED)+1))-1 | (W_REQ_MASKED & ((~W_REQ_MASKED)+1)));

end

else

begin

grant <= request & ((~request)+1);

R_MASK <= ~((request & ((~request)+1))-1 | (request & ((~request)+1)));

end

end

else

begin

R_STATUS <= LP_ST_WAIT_REQ_GRANT;

grant <= 0;

R_MASK <= 0;

end

end

LP_ST_WAIT_LOCK:

begin

if(|(lock & grant)) //未释放仲裁器

begin

R_STATUS <= LP_ST_WAIT_LOCK;

end

else if(|request) //释放的同时存在仲裁请求

begin

R_STATUS <= LP_ST_WAIT_LOCK;

if(|(request & R_MASK))//不全为零

begin

grant <= W_REQ_MASKED & ((~W_REQ_MASKED)+1);

R_MASK <= ~((W_REQ_MASKED & ((~W_REQ_MASKED)+1))-1 | (W_REQ_MASKED & ((~W_REQ_MASKED)+1)));

end

else

begin

grant <= request & ((~request)+1);

R_MASK <= ~((request & ((~request)+1))-1 | (request & ((~request)+1)));

end

end

else

begin

R_STATUS <= LP_ST_WAIT_REQ_GRANT;

grant <= 0;

R_MASK <= 0;

end

end

default:

begin

R_STATUS <= LP_ST_IDLE;

R_MASK <= 0;

grant <= 0;

end

endcase

end

end

endmodule憧憬

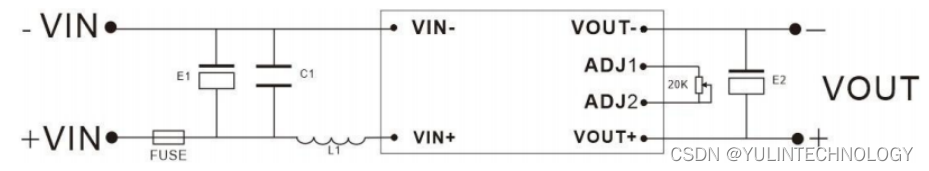

今年也是到了找工作的时候,未来我对职业方向的规划有两个:

1、从事FPGA设计验证方向的职业

2、从事ASIC芯片设计验证方向的职业

从可能性和意愿的强烈程度来说,我更加倾向于第二个:设计和验证ASIC。努力为IC事业做出一点贡献。

同样祝自己以及同行能在今年的秋招中,找到心仪的工作。加油 冲冲冲!