linux pl320 mbox控制器驱动分析

- 1 pl320简介

- 1.1 pl320用途

- 1.2 pl320 IPCM 由以下部分组成:

- 1.3 pl320 IPCM可配置的参数

- 1.4 功能操作

- 1.5 IPCM 操作流程

- 1.6 Channel ID

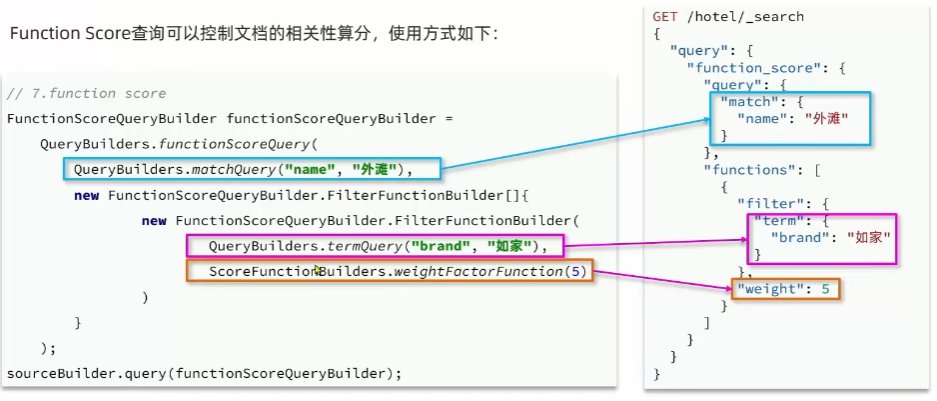

- 2 Using mailboxes(使用邮箱中断)

- 2.1 Defining source core

- 2.2 Defining destination core

- 2.3 Using the Mailbox Mask Register

- 2.4 Using the Mailbox Send Register

- 2.5 Mailbox Data Registers

- 2.6 Setting mode

- 2.6.1 Auto Acknowledge

- 2.6.2 Auto Link

- 2.7 Interrupts and status Registers

- 2.8 Configuration Status Register

- 2.9 Usage constraints

- 2.9.1 Multiple cores

- 2.9.2 Single core

- 2.9.3 Auto Link feature

- 2.9.3.1 Auto Acknowledge enabled

- 2.9.3.2 Auto Acknowledge disabled

pl320手册的下载地址为:

https://developer.arm.com/documentation/ddi0306/b/?lang=en

https://developer.arm.com/Processors/PL320

1 pl320简介

1.1 pl320用途

PL320 is an Inter-processor communications module for servicing interrupts. It pre-dates the GIC architecture.

PL320 是用于服务中断的处理器间通信模块。它早于 GIC 架构。

The IPCM provides up to 32 mailboxes with control logic and interrupt generation to support inter-processor communication. An AHB interface enables access from source and destination cores. The IPCM:

IPCM 提供多达 32 个邮箱,带有控制逻辑和中断生成以支持处理器间通信。 AHB 接口支持从源core和目标core进行访问。 IPCM:

- Sends interrupts to other cores.

- 向其他内核发送中断。

- Passes small amounts of data to other cores.

- 将少量数据传递给其他核心。

The mailboxes within the IPCM can be available as floating resources between cores or as dedicated resources to specific cores. A source core can have multiple mailboxes and send messages in parallel.

IPCM 中的邮箱可用作内核之间的浮动资源或用作特定内核的专用资源。源core可以有多个邮箱并并行发送消息。

1.2 pl320 IPCM 由以下部分组成:

- 1-32 个可编程邮箱,每个包含:

- 单个 1-32 位邮箱源寄存器

- 单个 1-32 位邮箱目标寄存器,具有单独的设置、清除和状态地址

- 单个 2 位邮箱模式寄存器以启用自动确认和自动链接模式

- 单个 1-32 位邮箱屏蔽寄存器,具有单独的设置、清除和状态地址,使您能够屏蔽掉需要轮询而不是被中断的内核的单个邮箱中断

- 单个 2 位邮箱发送寄存器,用于触发源和目标内核的邮箱中断

- 0-7 32 位数据寄存器存储消息。

- 1-32组只读中断状态寄存器,每个中断一个,每组包括:

- 1-32位原始中断状态寄存器(每个位对应每个邮箱)

- 1-32 位屏蔽中断状态寄存器(每个位对应每个邮箱)

- 一个 32 位配置状态寄存器

- 中断输出的集成测试寄存器

- 外设和 PrimeCell 标识寄存器。

1.3 pl320 IPCM可配置的参数

IPCM 是一个高度可配置和可编程的模块。它具有三个可配置的参数:

- 1-32个邮箱

- 每个邮箱 0-7 个数据寄存器

- 1-32 中断。

这些参数使您能够配置 IPCM 实例以满足系统要求,从而减少门数。源、目标、模式和掩码等可编程特性使配置的 IPCM 能够由不同的内核以不同的方式使用,具体取决于当前的应用。

1.4 功能操作

The IPCM generates interrupts under software control. These interrupts normally have data associated with them and can be directed to one or more of up to 32 different interrupt outputs. Each interrupt output corresponds directly to a bit in every Mailbox Source, Mailbox Destination, and Mailbox Mask Register in every mailbox in the IPCM. These registers therefore control which interrupt lines are asserted when messages are sent and acknowledged.

IPCM 在软件控制下产生中断。这些中断通常具有与其关联的数据,并且可以定向到多达 32 个不同中断输出中的一个或多个。每个中断输出直接对应于 IPCM 中每个邮箱中每个邮箱源、邮箱目标和邮箱掩码寄存器中的一个位。因此,这些寄存器控制在发送和确认消息时断言哪些中断线。

You connect the interrupt outputs to the system interrupt controllers during integration. One or more interrupt outputs can connect to each interrupt controller. Normally the IPCM has at least one interrupt output connected to every interrupt controller in the system, enabling any core to send a message to any other core. When more than one IPCM interrupt is connected to the same interrupt controller, different types of message can be indicated on different interrupt lines, and therefore handled by different ISRs.

在集成期间将中断输出连接到系统中断控制器。一个或多个中断输出可以连接到每个中断控制器。通常情况下,IPCM 至少有一个中断输出连接到系统中的每个中断控制器,使任何内核都可以向任何其他内核发送消息。当多个 IPCM 中断连接到同一个中断控制器时,不同类型的消息可以在不同的中断线上指示,因此由不同的 ISR 处理。

A multi-core system normally has at least one IPCM instantiated. More can be instantiated if required. Because the IPCM is configurable, you can have several differently configured IPCMs instantiated in the same system.

一个多核系统通常至少有一个实例化的 IPCM。如果需要,可以实例化更多。因为 IPCM 是可配置的,所以您可以在同一系统中实例化多个不同配置的 IPCM。

1.5 IPCM 操作流程

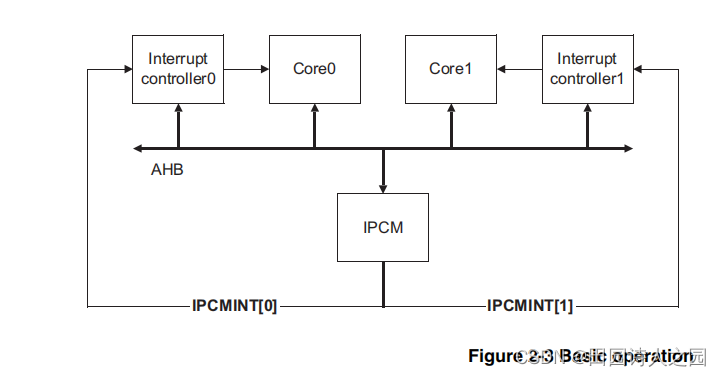

Figure 2-3 shows an example system in which the IPCM is integrated so that IPCMINT[0] is connected to the interrupt controller for Core0 and IPCMINT[1] is connected to the interrupt controller for Core1.

图 2-3 显示了一个示例系统,其中集成了 IPCM,因此 IPCMINT[0] 连接到 Core0 的中断控制器,IPCMINT[1] 连接到 Core1 的中断控制器。

- Core0 有一条消息要发送给 Core1。 Core0 通过在邮箱源寄存器中设置位 0 来声明邮箱。 Core0 然后在邮箱目标寄存器中设置位 1,启用中断并将消息编程到邮箱数据寄存器中。最后,Core 0 通过将 01 写入邮箱发送寄存器来发送消息。这会将中断断言到 Core1。

- 当 Core1 被中断时,它会读取 IPCMINT[1] 的屏蔽中断状态寄存器以确定哪个邮箱包含消息。 Core1 读取该邮箱中的消息,然后清除中断并通过向邮箱发送寄存器写入 10 来断言确认中断。

- Core0 被确认消息中断,完成操作。然后 Core0 决定是保留邮箱以发送另一条消息,还是释放邮箱,释放邮箱以供系统中的其他内核使用。

1.6 Channel ID

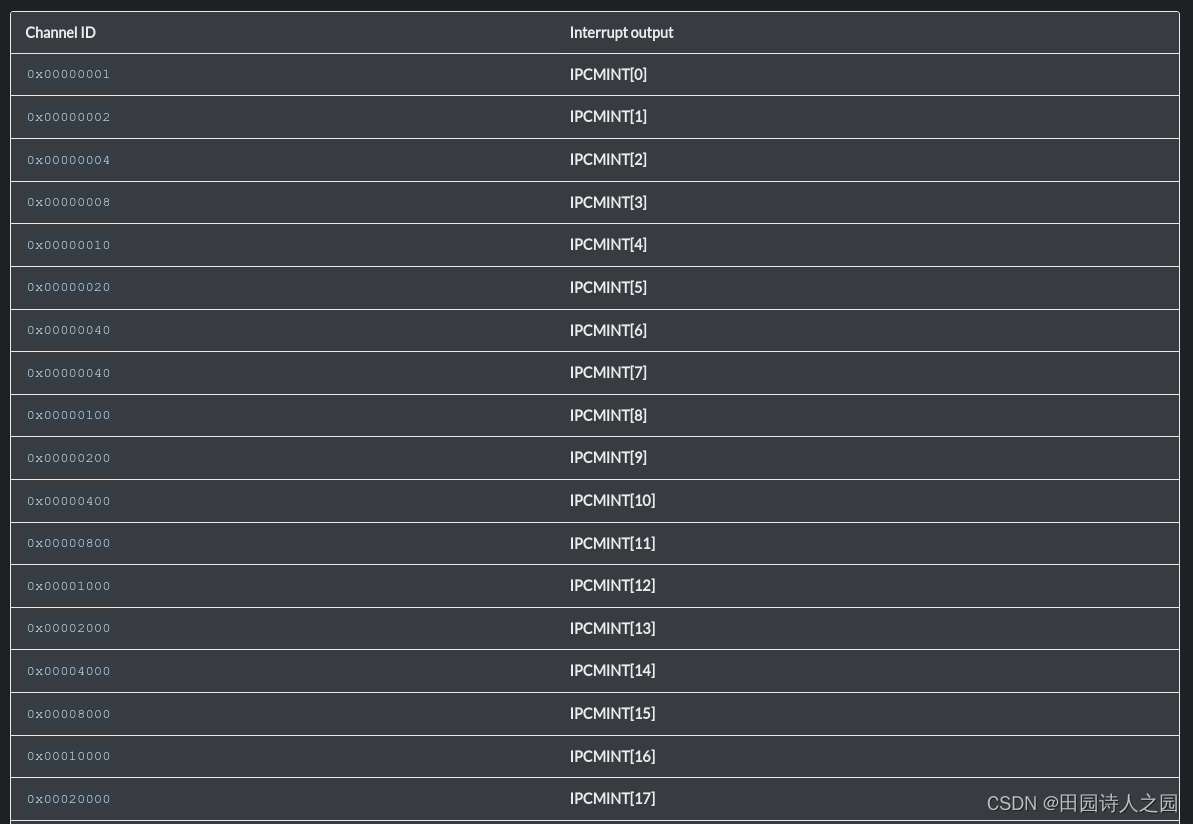

The Channel ID is defined as the one-hot encoded value that corresponds to a specific interrupt output from the IPCM. An IPCM configured to have 32 interrupt outputs has 32 corresponding Channel IDs. The Channel ID programs the Mailbox Source, Mailbox Destination, and Mailbox Mask Registers.

通道 ID 定义为与 IPCM 的特定中断输出相对应的单热编码值。配置为具有 32 个中断输出的 IPCM 具有 32 个对应的通道 ID。通道 ID 对邮箱源、邮箱目标和邮箱掩码寄存器进行编程。

Channel IDs map to 32 interrupt outputs (通道 ID 映射到 32 个中断输出).

从channel id和中断的映射关系可以看出,每个channel对应一个mbox中断。

在每个内核有一个 IPCM 中断的系统中,每个内核都有一个在 IPCM 中定义它的通道 ID。一些系统每个内核可以有多个 IPCM 中断,因此每个内核有多个通道 ID。

2 Using mailboxes(使用邮箱中断)

2.1 Defining source core

A core must obtain a mailbox to send a message. To do this the core writes one of its Channel IDs to the Mailbox Source Register and then reads the Mailbox Source Register back again to check whether the write was successful. The Mailbox Source Register must only contain a one-hot encoded value, that is, a single Channel ID. The software must ensure that only a one-hot encoded number is written to the Mailbox Source Register. You can only clear the Mailbox Source Register after it is programmed. Any writes other than 0x00000000 are ignored. This mechanism guarantees that only a single core has control of the mailbox at any one time.

核心必须获得邮箱才能发送消息。为此,核心将其通道 ID 之一写入邮箱源寄存器,然后再次读取邮箱源寄存器以检查写入是否成功。邮箱源寄存器必须只包含一个单热编码值,即单个通道 ID。软件必须确保只有一个热编码号码被写入邮箱源寄存器。您只能在编程后清除邮箱源寄存器。除 0x00000000 之外的任何写入都将被忽略。这种机制保证在任何时候只有一个核心可以控制邮箱。

A core gives up a mailbox, when it is no longer required, by clearing the Mailbox Source Register. Clearing the Mailbox Source Register also clears all the other registers in the mailbox. This guarantees that a mailbox is always cleared when it is newly allocated.

当不再需要邮箱时,核心会通过清除邮箱源寄存器来放弃邮箱。清除邮箱源寄存器也会清除邮箱中的所有其他寄存器。这保证了邮箱在新分配时总是被清除。

2.2 Defining destination core

The Mailbox Destination Register has separate Set and Clear write locations to enable you to set individual bits in the Mailbox Destination Register without using read-modify-write transfers. You can set a single bit in the Mailbox Destination Register by writing that bit to the Destination Set Register. This causes the hardware to OR that bit with the current Mailbox Destination Register value. Similarly, you can clear a single bit in the Mailbox Destination Register by writing that bit to the Destination Clear Register.

邮箱目标寄存器具有单独的设置和清除写入位置,使您能够在不使用读-修改-写传输的情况下设置邮箱目标寄存器中的各个位。您可以通过将该位写入目标设置寄存器来设置邮箱目标寄存器中的单个位。这会导致硬件将该位与当前的邮箱目标寄存器值进行“或”运算。同样,您可以通过将邮箱目标寄存器中的一位写入目标清除寄存器来清除该位。

When the source core defines the mode of a mailbox, it defines which other cores are to receive the message by programming the OR of all the Channel IDs into the Mailbox Destination Register. If a core has more than one Channel ID only one is used per message. You can only write to the Mailbox Destination Register after the Mailbox Source Register is defined.

当源 core 定义邮箱模式时,它通过将所有通道 ID 的 OR 编程到邮箱目标寄存器中来定义哪些其他core将接收消息。如果一个core有多个通道 ID,则每条消息只使用一个。您只能在定义邮箱源寄存器后写入邮箱目标寄存器。

2.3 Using the Mailbox Mask Register

The Mailbox Mask Register uses separate Set and Clear registers for modification similar to the Mailbox Destination Register. The Mailbox Mask Register enables the interrupt outputs. To enable interrupts for a particular mailbox, a core writes its Channel ID to the Mask Set location. The interrupt for that mailbox can be masked out by writing the same Channel ID to the Mask Clear location. You can only write to the Mailbox Mask Register locations after the Mailbox Source Register is defined.

邮箱掩码寄存器使用单独的设置和清除寄存器进行修改,类似于邮箱目标寄存器。邮箱掩码寄存器启用中断输出。要为特定邮箱启用中断,内核将其通道 ID 写入掩码集位置。可以通过将相同的通道 ID 写入屏蔽清除位置来屏蔽该邮箱的中断。您只能在定义邮箱源寄存器后写入邮箱掩码寄存器位置。

2.4 Using the Mailbox Send Register

A message is sent by setting bit 0 of the Mailbox Send Register. This triggers the interrupt to the destination core. Clearing this bit clears the interrupt to the destination core. The acknowledge message is sent to the source core by setting bit 1 of the Mailbox Send Register. Clearing this bit clears the interrupt to the source core. You can use one write to clear bit 0 and set bit 1 in the Mailbox Send Register, although this is not mandatory. You cannot set bit 1 then clear bit 0 because 11 is an invalid value for the Mailbox Send Register. The Mailbox Send Register can only be written to after the Mailbox Source Register is defined.

通过设置邮箱发送寄存器的位 0 来发送消息。这会触发到目标core的中断。清除该位会将中断清除到目标内核。通过设置邮箱发送寄存器的位 1 将确认消息发送到源core。清除该位会清除源内核的中断。您可以使用一次写入清除邮箱发送寄存器中的位 0 并设置位 1,但这不是强制性的。您不能设置位 1 然后清除位 0,因为 11 是邮箱发送寄存器的无效值。邮箱发送寄存器只能在邮箱源寄存器定义后写入。

2.5 Mailbox Data Registers

The Mailbox Data Registers are general-purpose 32-bit registers that contain the message and can only be written to after the Mailbox Source Register is defined. The Mailbox Data Registers are normally written to before sending the message.

邮箱数据寄存器是包含消息的通用 32 位寄存器,只能在定义邮箱源寄存器后写入。邮箱数据寄存器通常在发送消息之前写入。

2.6 Setting mode

The Mailbox Mode Register controls how the acknowledge interrupt is sent back to the source core, and whether the current mailbox is linked to the next mailbox in the IPCM. The Mailbox Mode Register has two bits and you can only write to it after the Mailbox Source Register is defined.

邮箱模式寄存器控制如何将确认中断发送回源内核,以及当前邮箱是否链接到 IPCM 中的下一个邮箱。邮箱模式寄存器有两个位,您只能在定义邮箱源寄存器后写入它。

2.6.1 Auto Acknowledge

In Auto Acknowledge mode, an acknowledge interrupt is automatically sent to the source core after the final destination core has cleared its interrupt. Destination cores must clear their interrupts by writing their Channel ID value to the Destination Clear location. This clears their Channel ID from the Mailbox Destination Register. When the Mailbox Destination Register finally reaches zero, indicating that all destination cores have cleared their interrupts, the mailbox automatically detects this, clears bit 0 and sets bit 1 of the Mailbox Send Register. The source core then receives the acknowledge interrupt. The data associated with an Auto Acknowledge is the same as that for the original message. You can use Auto Acknowledge mode for 1-32 destination cores.

在自动确认模式下,在最终目标core清除其中断后,确认中断会自动发送到源内核。目标内核必须通过将它们的通道 ID 值写入目标清除位置来清除它们的中断。这将从邮箱目标寄存器中清除他们的通道 ID。当邮箱目标寄存器最终达到零时,表明所有目标内核都已清除其中断,邮箱会自动检测到这一点,清除位 0 并设置邮箱发送寄存器的位 1。源core然后接收确认中断。与自动确认关联的数据与原始消息的数据相同。您可以对 1-32 个目标内核使用自动确认模式。

Note

You can use Auto Acknowledge when the system contains just two cores, a source core and a destination core.

当系统仅包含两个内核(一个源core和一个目标core)时,您可以使用自动确认。

When Auto Acknowledge mode is disabled, the acknowledge interrupt is optional. The destination core must clear its interrupt by clearing bit 0 of the Mailbox Send Register. Only when the destination core sets bit 1 of the Mailbox Send Register does the source core obtain its acknowledge interrupt, indicating that the destination core has finished with the message. You can only disable Auto Acknowledge mode when there is only one destination core, where there is also a possibility of updating the message for the acknowledge.

当禁用自动应答模式时,应答中断是可选的。目标core必须通过清除邮箱发送寄存器的位 0 来清除其中断。只有当目标内核设置邮箱发送寄存器的位 1 时,源内核才会获得其确认中断,表明目标内核已完成消息处理。您只能在只有一个目标core时禁用自动确认模式,其中也有可能更新确认消息。

2.6.2 Auto Link

Auto Link provides a mechanism to link mailboxes together so that when a message is acknowledged in one mailbox, the next message is sent from the linked mailbox instead of interrupting the source core. When Auto Link is enabled, the destination core clears bit 0 and sets bit 1 of the Mailbox Send Register in the usual way, but the acknowledge interrupt to the source core is masked out and Mailbox Send Register bit 0 is set in the next mailbox, sending that message.

自动链接提供了一种将邮箱链接在一起的机制,这样当一个邮箱中的一条消息被确认时,下一条消息将从链接的邮箱发送,而不是中断源core。当启用自动链接时,目标core会以通常的方式清除邮箱发送寄存器的位 0 并设置位 1,但是源内核的确认中断被屏蔽掉,邮箱发送寄存器的位 0 会在下一个邮箱中设置,发送该消息。

In this mode, a source core can allocate multiple mailboxes to itself, link them together by setting the Auto Link bits and preload messages in all the mailboxes. When the first message is sent, it is not acknowledged until all the messages have been sent. There is no restriction on the destinations of these messages or whether Auto Acknowledge is enabled when Auto Link is used. In the IPCM, Mailbox0 can be linked to Mailbox1, which in turn can be linked to Mailbox2, up to Mailbox31. For example, if you want to link Mailbox0, Mailbox1, and Mailbox2, set the Auto Link bits in Mailbox0 and Mailbox1. Do not set the Auto Link bit in Mailbox2, to enable the acknowledge interrupt to be sent back to the source core.

在这种模式下,源内核可以为自己分配多个邮箱,通过设置自动链接位将它们链接在一起,并在所有邮箱中预加载消息。发送第一条消息时,直到发送完所有消息后才会确认。对于这些消息的目的地或使用自动链接时是否启用自动确认没有限制。在 IPCM 中,Mailbox0 可以链接到 Mailbox1,Mailbox1 又可以链接到 Mailbox2,直到 Mailbox31。例如,如果要链接 Mailbox0、Mailbox1 和 Mailbox2,请设置 Mailbox0 和 Mailbox1 中的自动链接位。不要设置 Mailbox2 中的自动链接位,以允许将确认中断发送回源内核。

When Auto Link is disabled, the source core is interrupted if an acknowledge interrupt is sent that has no effect on any other mailbox.

禁用自动链接时,如果发送了对任何其他邮箱都没有影响的确认中断,则源内核将被中断。

Note

When using Auto Link with Auto Acknowledge, the mailbox automatically sets Mailbox Send Register bit 1 in the first mailbox to send the acknowledge back to the source core but, because Auto Link is also set, the mailbox automatically sets Mailbox Send Register bit 0 in the linked mailbox.

当使用带有自动确认的自动链接时,邮箱会自动在第一个邮箱中设置邮箱发送寄存器位 1 以将确认发送回源内核,但是,由于还设置了自动链接,邮箱会自动在第一个邮箱中设置邮箱发送寄存器位 0链接邮箱。

2.7 Interrupts and status Registers

When a core receives an IPCM interrupt, it determines which mailbox triggered it by reading the Masked Interrupt Status Register related to that interrupt line. Each Masked Interrupt Status Register contains up to 32 bits, each bit referring to a single mailbox.

当内核接收到 IPCM 中断时,它通过读取与该中断线相关的屏蔽中断状态寄存器来确定哪个邮箱触发了它。每个屏蔽中断状态寄存器最多包含 32 位,每一位对应一个邮箱。

If a core is using a mailbox in polled mode, it can use the Raw Interrupt Status Register to indicate which mailbox requires attention.

如果内核在轮询模式下使用邮箱,它可以使用原始中断状态寄存器来指示需要注意哪个邮箱。

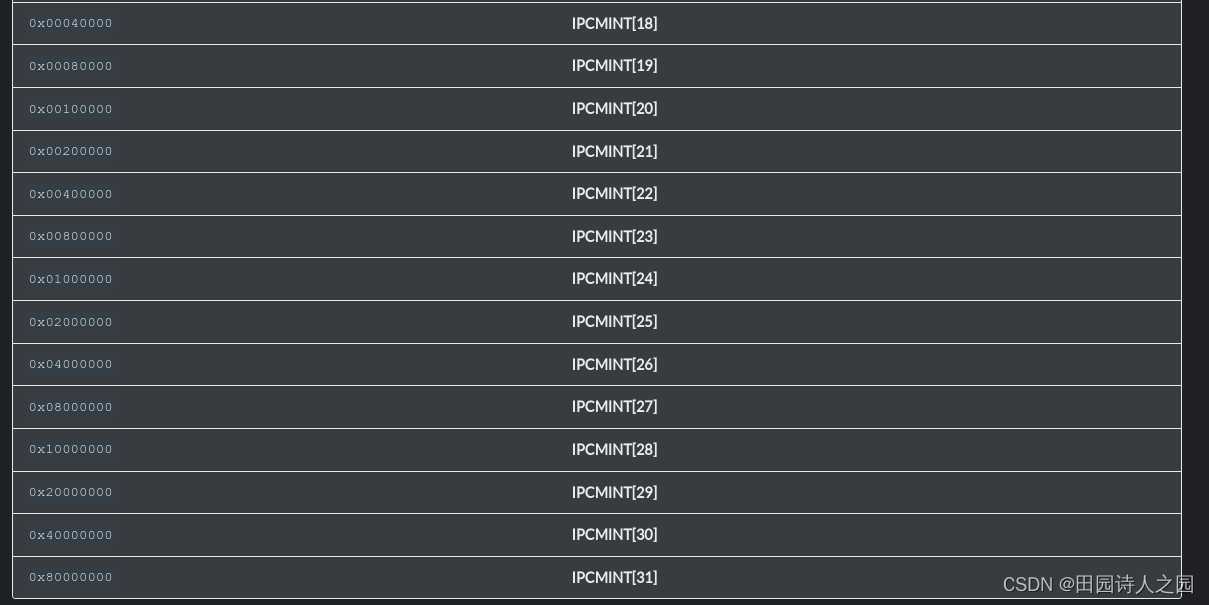

In Figure 2.4, each mailbox contains up to seven data registers to hold the message. Every mailbox instance with a single IPCM must have the same number of data registers.

在图 2.4 中,每个邮箱最多包含 7 个数据寄存器来保存消息。每个具有单个 IPCM 的邮箱实例必须具有相同数量的数据寄存器。

Each mailbox can generate up to 32 interrupts, one for each Channel ID. The number of interrupts defines the number of bits in the Mailbox Source Register, Mailbox Destination Register, and Mailbox Mask Register. For example, in Figure 2.4, the IPCM has 32 interrupt outputs. Mailbox0 generates bit 0 of the IPCMMIS0-31 buses, while Mailbox31 generates bit 31 of the IPCMMIS0-31 buses.

每个邮箱最多可产生 32 个中断,每个通道 ID 一个。中断的数量定义了邮箱源寄存器、邮箱目标寄存器和邮箱掩码寄存器中的位数。例如,在图 2.4 中,IPCM 有 32 个中断输出。 Mailbox0 生成 IPCMMIS0-31 总线的位 0,而 Mailbox31 生成 IPCMMIS0-31 总线的位 31。

Multiple mailboxes are grouped together as shown in Figure 2.4 to form the 32-bit IPCM interrupt bus, IPCMINT[31:0]. All the interrupt bits from each mailbox relating to a single Channel ID are grouped together to form the masked interrupt status buses, IPCMMIS0[31:0] to IPCMMIS31[31:0]. The bits within these buses are then ORed together to form the IPCM interrupt bus, IPCMINT[31:0].

如图 2.4 所示,多个邮箱组合在一起形成 32 位 IPCM 中断总线,IPCMINT[31:0]。来自与单个通道 ID 相关的每个邮箱的所有中断位组合在一起形成屏蔽中断状态总线,IPCMMIS0[31:0] 到 IPCMMIS31[31:0]。然后将这些总线中的位进行“或”运算以形成 IPCM 中断总线 IPCMINT[31:0]。

2.8 Configuration Status Register

The three configurable parameters for the IPCM are:

IPCM 的三个可配置参数是:

- number of mailboxes, 1-32

- 邮箱数量,1-32

- number of data registers per mailbox, 0-7

- 每个邮箱的数据寄存器数,0-7

- number of interrupts, 1-32.

- 中断数,1-32

The configuration options that you choose define the read-only Configuration Status Register, enabling software to determine the IPCM configuration by reading this register. This enables a generic IPCM software driver to determine how to use each IPCM instance within a system.

您选择的配置选项定义了只读配置状态寄存器,使软件能够通过读取该寄存器来确定 IPCM 配置。这使通用 IPCM 软件驱动程序能够确定如何使用系统中的每个 IPCM 实例。

2.9 Usage constraints

There are several valid use models for a mailbox and some constraints under which they can be used. Messages can be sent to:

有几种有效的邮箱使用模型和使用它们的一些限制条件。消息可以发送至:

2.9.1 Multiple cores

If a message is sent to multiple cores, you must use the Auto Acknowledge feature and data must not be modified for the acknowledge. Destination cores must clear their interrupts by writing their Channel ID to the Destination Clear Register.

如果一条消息被发送到多个内核,您必须使用自动确认功能,并且不得为确认修改数据。目标内核必须通过将它们的通道 ID 写入目标清除寄存器来清除它们的中断。

2.9.2 Single core

If there is only a single destination core, the Auto Acknowledge mode is optional. If you disable the Auto Acknowledge mode, the acknowledge is optional, although an acknowledge normally happens, and the Mailbox Data Register can optionally be updated. When Auto Acknowledge is disabled, the destination core must clear its interrupt by clearing bit 0 of the Mailbox Send Register.

如果只有一个目标内核,则自动确认模式是可选的。如果禁用自动确认模式,则确认是可选的,尽管通常会发生确认,并且可以选择更新邮箱数据寄存器。禁用自动确认时,目标core必须通过清除邮箱发送寄存器的位 0 来清除其中断。

2.9.3 Auto Link feature

You can only use the Auto Link feature when there is an acknowledge. You can use the Auto Link feature with either:

您只能在确认时使用自动链接功能。您可以将自动链接功能用于:

2.9.3.1 Auto Acknowledge enabled

The mailbox automatically sets the acknowledge when the final destination core clears its interrupt.

当最终目标内核清除其中断时,邮箱会自动设置应答。

2.9.3.2 Auto Acknowledge disabled

The destination core must send the acknowledge.

目标内核必须发送确认。

![PMP项目管理-[第十一章]风险管理](https://img-blog.csdnimg.cn/a4b3f502a3554c43a0c8d9e75547dd19.png)

![[数据集][目标检测]篮球数据集VOC格式7398张](https://i2.hdslb.com/bfs/archive/fc56600314ed0869f21da32f4d9837fef9eb17d6.jpg@100w_100h_1c.png@57w_57h_1c.png)