1 概述

近年来 ,大容量数据存储设备受到软硬件等发展的限制主

要还是采用机械硬盘叠加组合而用。机械硬盘以磁盘片作为载

体 ,采用机械马达 ,存在抗振性能低、低温性能差、噪声大等缺点。

固态硬盘是以半导体作为存储介质及控制载体 ,无机械装置 ,

具有抗震、宽温、无噪、可靠和节能等特点 ,在大型、复杂电

子设备中发挥着越来越显著的作用。大容量固态存储技术正引

起人们广泛的关注。

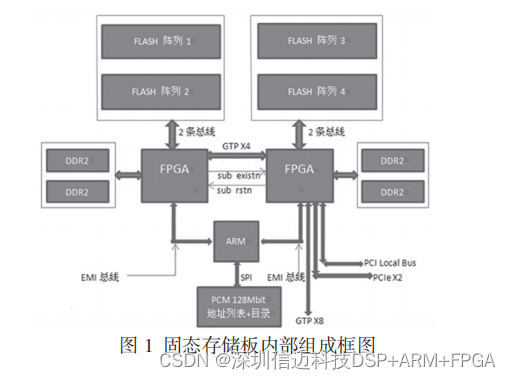

本文结合某项目的需要 ,采用由 ARM 与现场可编程门阵列

(FPGA)控制管理固态存储板的实现方法 ,实现单板(6U CPCI

标准板卡)容量不低于 4TB 固态存储板。

2 系统方案架构

针对不同的应用 ,以 ARM 为处理器 ,可以扩展 FPGA 来实

现不同容量的存储控制板 ,各种系统架构基本类似。现以本公

司某型号双 FPGA 控制技术实现 6U CPCI 标准板卡 ,其单板支

持最大 4TB 存储容量固态板加以说明。

该固态存储板由 128 片 NAND FLASH 组成(每片 32 GB),

每 32 片 NAND FLASH 为一组 ,总存储容量为 4 TB。其通过 2

片高性能 FPGA 和 1 片 ARM 处理器对 NAND FLASH 进行逻辑

控制 ,共有 4 条 64-bit 的 FLASH 总线。每 32 片 NAND FLASH

有一条 FLASH 总线驱动 ,读写速度可达 260 MB/S,单板可达到

1040 MB/s 总带宽。由于选择 GTP×4 高速串行总线方式 ,其可

满足 448 MByte/s 存储速度的项目需求。固态存储板内部组成框

图如图 1 所示。

3 ARM 处理器 ,FPGA 的选用及驱动算法实现

NXP 半导体是以 16 或 32 位的 ARM7TDMI-S CPU 内核来实

现 LPC2478 微控制器 ,其自带实时嵌入式跟踪与 JTAG 调试接

口。LPC2478 微控制器运行频率高达 72 MHz,Flash 程序存储器

有 512 KB,可实现应用编程(IAP)和系统编程(ISP)的功能。

LPC2478 能够执行 16 位 Thumb 指令及 32 位 ARM,可为技术人

员在程序级下就可选择性优化应用。其 98 KB 片内 SRAM 可由

RTC 供电存储数据,对于高性能 CPU 可通过 ARM 局部总线访问。

通过双 AHB 总线系统 ,可保证片内 Flash 程序的执行与同步以

太网 USB DMA、DMA 之间互不抢占。LPC2478 微控制器对于多

种用途的通信应用也十分适用 ,其具有丰富的串行接口及其它

的外设。

Virtex-5 系列作为第二代高级芯片组合模块(ASMBLTM)

列式架构 ,有 5 个截然不同的子系列(LX、LXT、SXT、TXT

及 FXT),是 FPGA 系列中选择最为丰富的系列。主要应用包括

具备高级串行连接功能的高性能逻辑、具备双密度高级串行连

接功能的高性能系统、具备高级串行连接功能的高性能信号处

理应用、具备高级串行连接功能的高性能嵌入式系统、其高性

能通用逻辑应用每个平台都拥有独特特性 ,以满足诸多高级逻

辑设计的需求。除最先进的高性能逻辑结构外 ,Vritex-5 FPGA

内置大量 IP 硬核系统级模块、可支持多达 330,000 个逻辑单

元及多达 17 个外部模拟输入通道、具有多速率 FIFO 支持逻辑、

也可以通过 JTAG TAP 或内部结构访问系统监控器。

本 例 固 态 存 储 板 中 的 同 样 为 Vritex-5 FPGA 芯 片 具 备

FLASH 控制器功能 ,在整个 FLASH 控制技术中融入了均衡管

理技术、实时坏块剔除技术、纠错技术等多项技术 ,对存储数

据的正确性、稳定性及安全性得到了保障。这几项 FLASH 控制

技术已在多个项目中稳定应用。产品实物正面图如图 2。

其中 ,均衡管理技术是采用

顺序循环管理算法 ,包含线性表

内含顺序表和链表 ,依据数据记

录设备对数据读写访问的方式 ,

在整个存储空间的 BLOCK 中均衡

的 进 行 ERASE、PROGRAM 操 作

方法 ,从而保证硬件的整体寿命。

实时坏块剔除技术是采用坏

块实时监测电路方法 ,在读写过

程 对 FLASH 的 BLOCK 状 态 进 行

实时监测 ,从而识别整个存储空

间的 BAD BLOCK,进行标识和替

换 ,有效的保证了对 BAD BLOCK

的实时剔除。

纠错技术是采用针对二进制

通道的 BCH 算法 ,具有严格的纠

错能力、构造简单、编码较其它

编码容易等特点 ,其中又采用了

硬件高速电路并行工作方式 ,从

而实现了高性能的 BCH 编码、解

码算法 ,保证 FLASH 数据的正确

性。

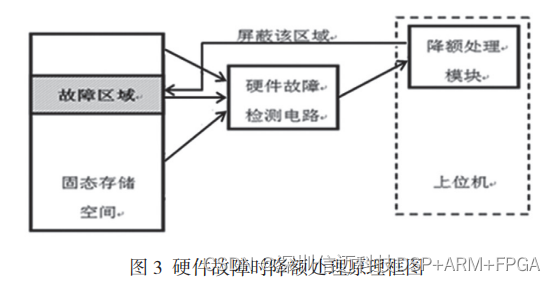

虽然以 NAND Flash 大容量存储器具有许多优点 ,但其有随

机产生不可避免的坏块可能 ,此时如不能很好解决该坏块问题 ,

将导致较高故障率。当在 FLASH 芯片出现硬件故障时 ,产品在

存储速度或存储数据容量上还要满足紧急、临时侦查任务的数

据存储实际使用要求时。这需要进一步提高存储板的容错能力 ,

在发生硬件故障时可以通过降额使用的方式 ,保证产品仍能继

续使用。降额设计包括硬件故障自动检测和降额处理两项功能。

硬件故障时降额处理原理框图如图 3 所示。

产品上电时 ,硬件故障自动检测功能会对存储板的所有

NAND FLASH 进行硬件状态检测 ,如果发现硬件故障 ,则向上

层报告硬件故障的区域。

为了保证存储板发生故障时仍能正常工作 ,上层的降额处

理功能在接收到硬件故障报告后 ,能有效的屏蔽故障区域对硬

件故障进行处理。

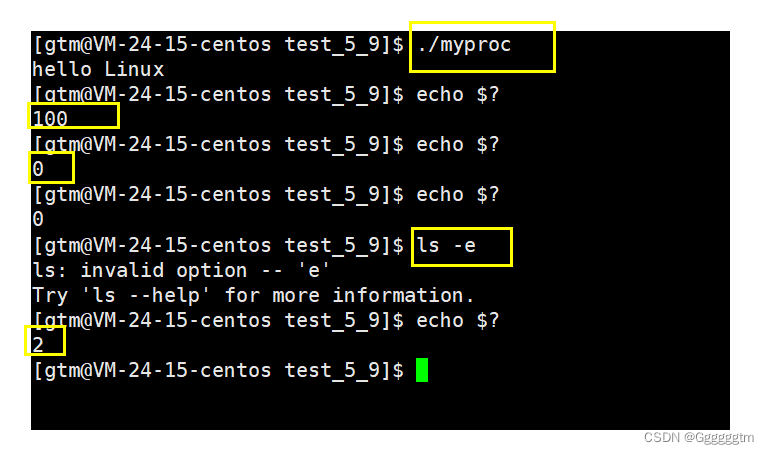

4 开发工具使用与实现的调试过程

1)ARM 调试 :本例中与 NXP(LPC2478FET208)微处理

器使用的单片机开发环境为 Keil uVision4 界面如图 4 所示 ,对

已调试好的程序可通过 ARM 下载仿真器查看下载是否正确 ,并

且确认程序是否能正常加载运行。若出现异常现象 ,可以进行

相应排查处理及后期的低格处理。

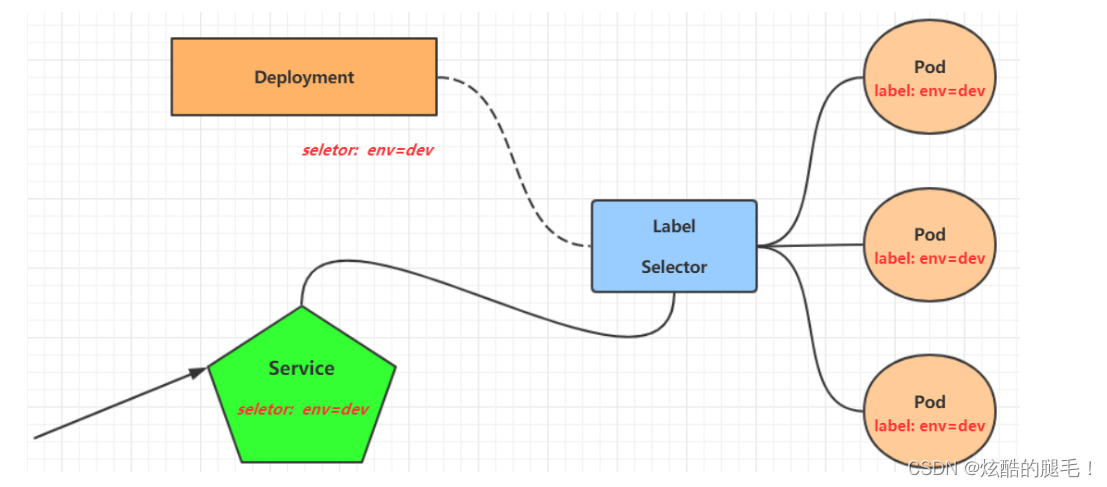

2)FPGA 调试 :本例是以 Xilinx ISE Design Suite 13.3 为开

发环境 ,通过仿真器可对其硬件 FPGA 程序进行编译、调试及

下载、包括对其 FLASH 阵列焊接情况扫描 ,如果发现 FLASH

读 ID、STATUS 信号线有异常情况 ,可通过 FLASH 的 IO 值及

片选信号确定 FLASH 出错具体位置。图 5 为通过 ChipScope Pro

Analyzer 工具 ,扫描 FLASH 状态以便排除不良焊接及有坏道的

FLASH。

同样在调试前期工作完成后 ,再通过内部信号源模拟测试

记录、回放。既可判别整块固态存储板卡的数据的存储与读取

的正确性。