要建立DDR3的测试工程,首先要生成mig IP核,然后写测试模块使用这个IP核进行测试。

一、生成 mig IP核

建立一个新工程,然后生成 mig IP核。

关键步骤如下:

(1)点击 IP catalog,在搜索框输入mig,然后双击IP核打开进行数据配置。

(2)根据需要选择AXI接口:如果用FIFO控制读写,就不需要勾选;如果用AXI控制读写,则勾上。

(3)选择DDR3

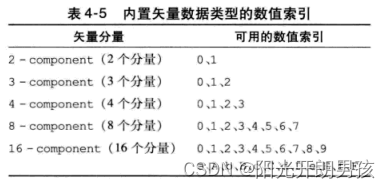

(4)时钟周期,根据需要选择,一般用800M或者400M。DDR的型号也是根据自己实际使用情况进行选择。数据位宽,如果一片DDR是16位,用了一片DDR,就选择16位;如果用了两片,那就选择16 *2 = 32位。其他情况以此类推。

有些型号的DDR有不同的电压要求,根据实际情况选择memory voltage。

(5)这里的时钟周期得是(4)当中选的时钟的四分之一。

(6)system clock,如果是FPGA内部产生的就选择no buffer,如果不是,根据原理图上所给信号的类型选择差分或者单端。而reference clock 一般选择使用system clock。

(7)开始进行引脚约束,选择fixed 开头的选项,进入引脚约束界面:

约束引脚的方法有两个:

第一,在这个界面对着原理图一个一个约束,比较花时间;

第二,提前写好xdc文件,点击右下角的read xdc/ucf读XDC文件,这样比较快。

约束完全部引脚,点validate,然后再next。

(8)选择时钟的输入引脚

以上步骤完成后,一直next就可以了。

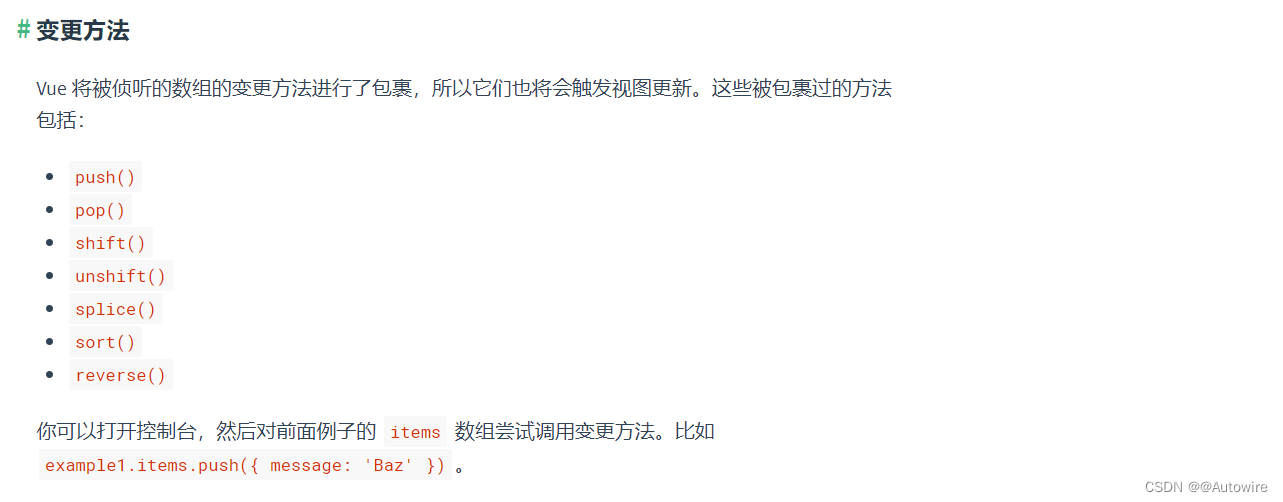

二、写测试模块

IP核生成之后,写测试模块使用IP核进行测试。