大家好,我是虎哥,很长时间没有发布新内容,主要是这段时间集中精力,研究DTB设备树的修改,以适配不同载板,同时也是专门做了一个TX1&TX2核心,双网口,可以使用SPI 扩展CAN接口的载板,EdgeBox_Umate_A200。也是有感于网上修改DTB文件的测试SPI的资料不是nano的,就是NX的,TX1和TX2相关的说明已经很少了,所以这里我将我自己修改DTB文件做测试的经验分享给大家,希望可以对相关爱好者有帮助。

注意:

-

以下内容都是TX1核心,JetPack4.6.2环境版本的详细说明,如果使用TX2的SPI口,我后续可以再补充。

-

如果你的载板没有引出对应的SPI,就不要修改,只关注你引出的SPI口的对应DTB内容即可

目录

一、TX1 核心模块中SPI接口的说明

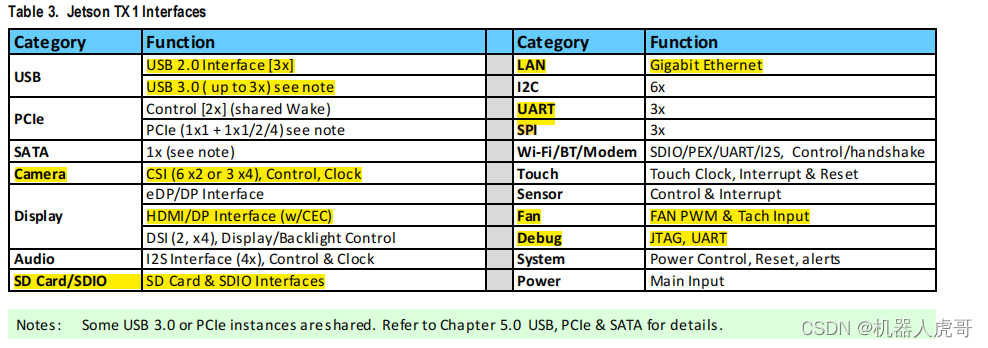

1.1 TX1核心模块的外设资源汇总

1.2 SPI接口对应管脚说明

1.3 SPI在内容的对应地址关系

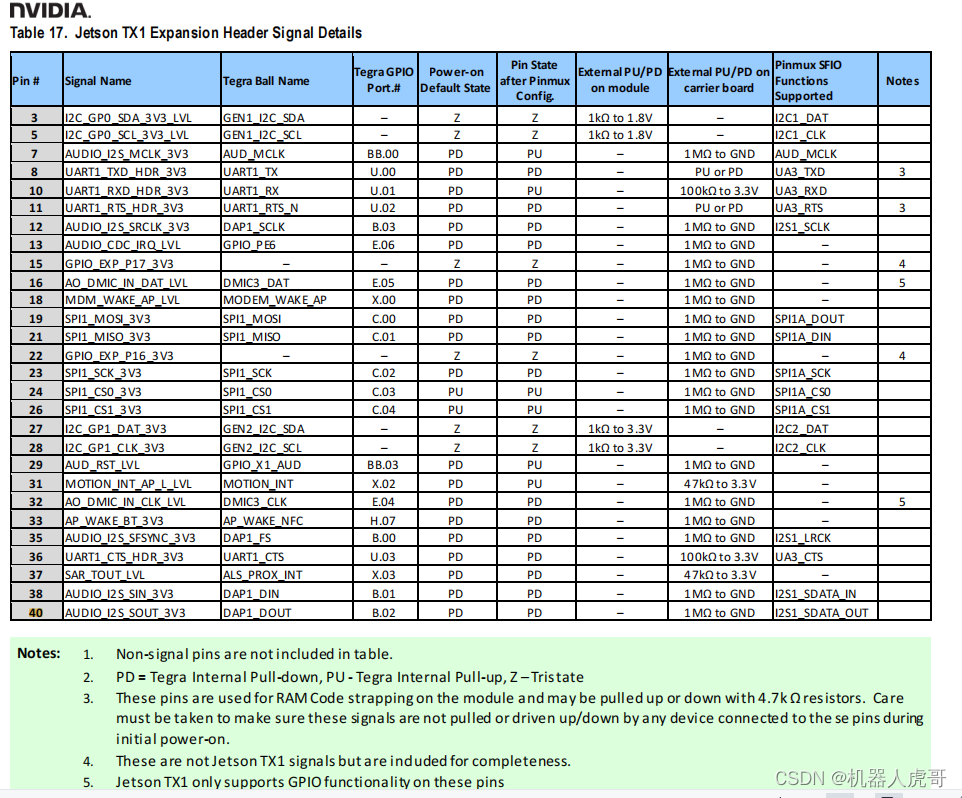

1.4 TX1官方开发条件40P外部接口中的SPI说明

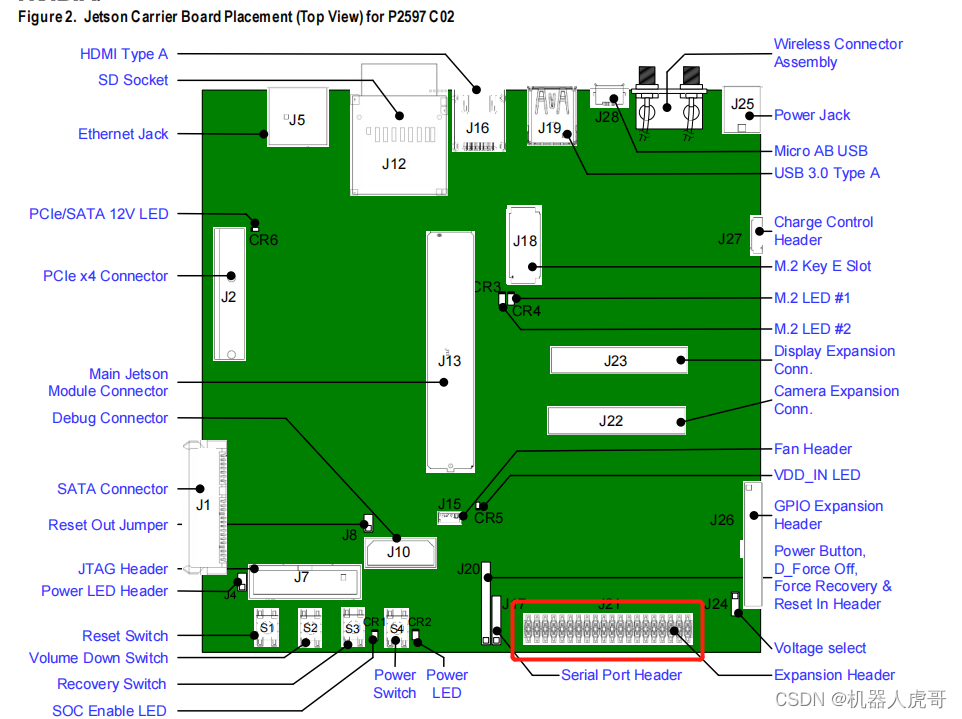

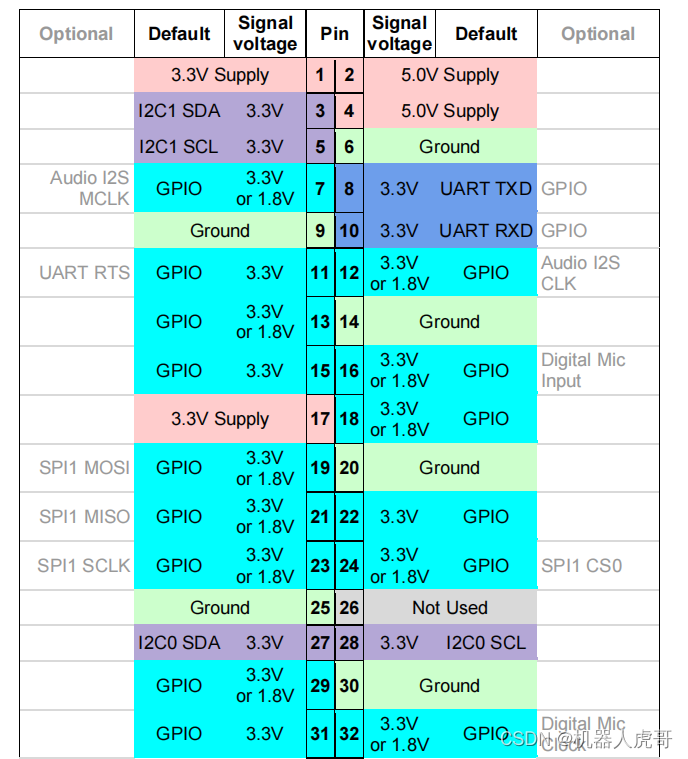

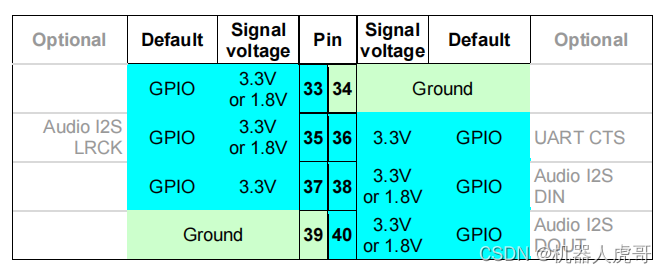

C02 开发套件中40 Pin接口定义,兼容 TX2 有些 TX1是没有的

TX1 40pin定义

二、A200载板+TX1 核心模块中使能SPI4 和 SPI1 控制器

2.1 修改所有SPI对应的引脚定义

1、spi4 Pin原始定义:

2、spi2 Pin原始定义:

3、spi1 Pin原始定义:

4、spi1 Pin初始化管脚定义修改

2.2 修改所有SPI设备详细初始化定义

1、spi0 = "/spi@7000d400"; ---------->SPI1修改:

2、spi3 = "/spi@7000da00"; ---------->SPI0---------->SPI4 修改:

3、spi1 = "/spi@7000d600"; ---------->SPI2---------->SPI2 修改:

2.3 小技巧:

三、编译DTS文件至DTB文件,更新系统

3.1 编译烧写

3.2 测试

3.3 开机自动加载SPIDEV设备技巧

四、总结

一、TX1 核心模块中SPI接口的说明

1.1 TX1核心模块的外设资源汇总

其中描述,可用的SPI资源是3路。

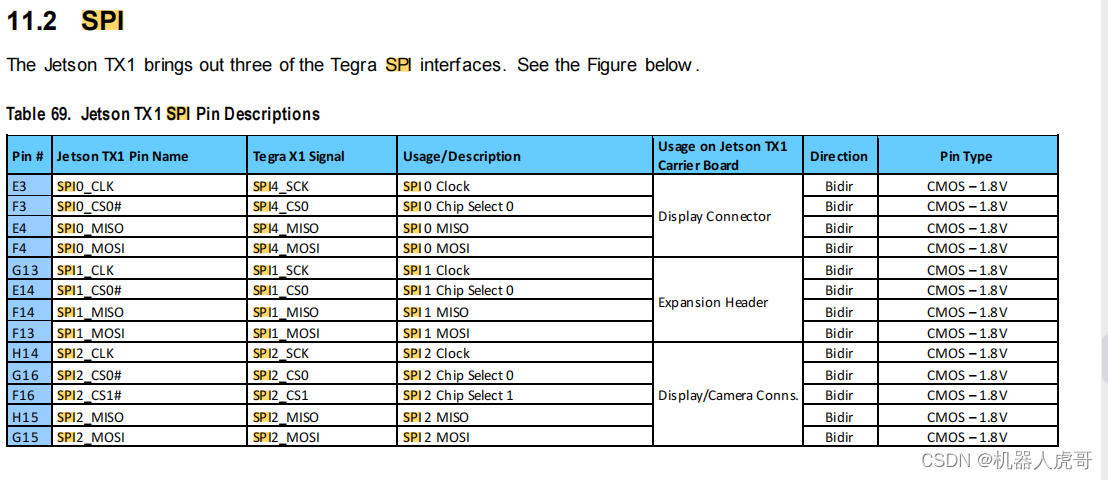

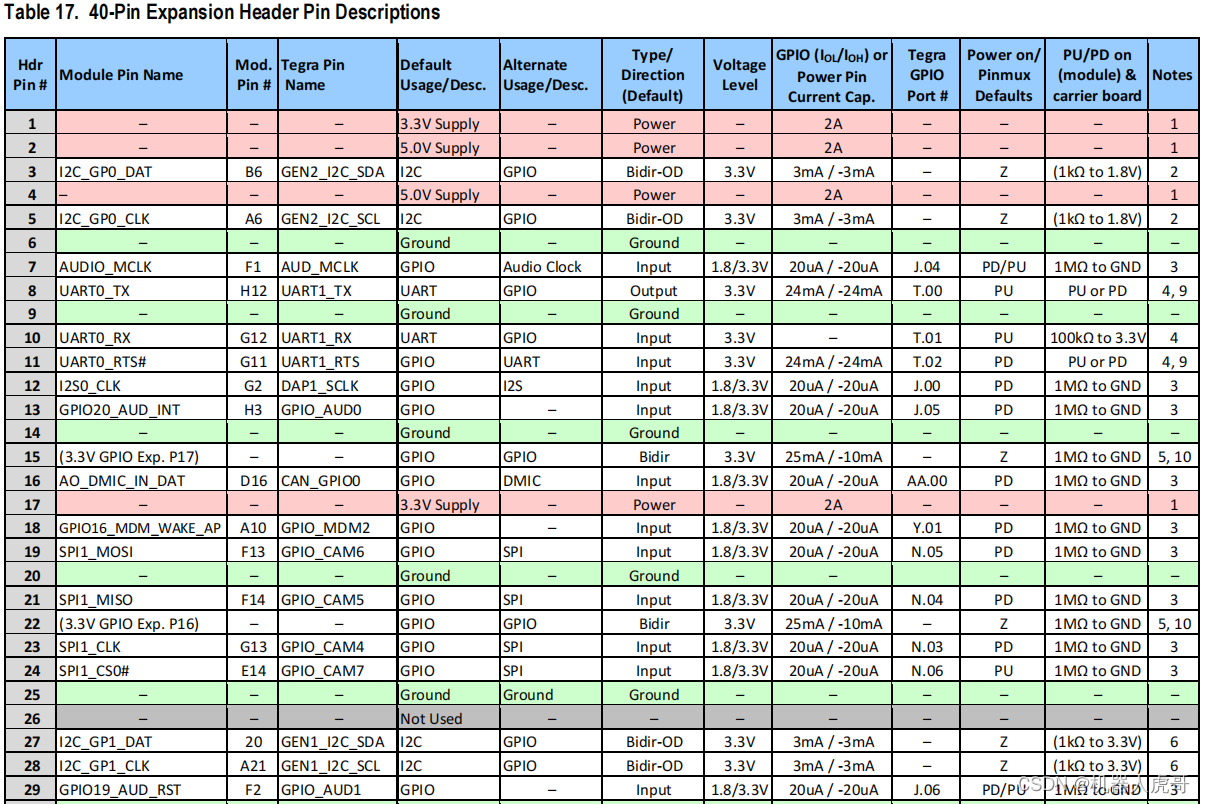

1.2 SPI接口对应管脚说明

TX1模块中的3路SPI,对应管脚见上图。图中注意区分两个同喜,第2列是TX1 PIN name,这个其实是官方开发套件图中的名字,对应的TX1核心模块系统中,其实看第2列,这个地方不注意,很容易混淆。

#SPI0 ------------>TX1 系统核心内是SPI4

SPI0_CS0------F3

SPI0_MOSI-----F4

SPI0_CLK------E3

SPI0_MISO-----E4

#SPI1 ------------>TX1内是SPI1

SIP1_CS0------E14

SIP1_CS1------E13

SPI1_MOSI-----F13

SPI0_MISO-----F14

SPI1_CLK------G13

#SPI1 Tegra X1 Signal Name

SIP1_CS0------E14 ---------->spi1_cs0_pc3

SPI1_MOSI-----F13 ---------->spi1_miso_pc1

SPI1_MOSI-----F14 ---------->spi1_mosi_pc0

SPI1_CLK------G13 ---------->spi1_sck_pc2

SIP1_CS1------E13 ---------->spi1_cs1_pc4

#SPI0 Tegra X1 Signal Name

SIP0_CS0------F3 ---------->spi4_cs0_pc6

SPI0_MISO-----E4 ---------->spi4_miso_pd0

SPI0_MOSI-----F4 ---------->spi4_mosi_pc7

SPI0_CLK------E3 --------->spi4_sck_pc5

#SPI2 Tegra X1 Signal Name

SIP2_CS0------G16 ---------->spi2_cs0_pb7

SIP2_CS1------F16 ---------->spi2_cs1_pdd0

SPI2_MISO-----H15 ---------->spi2_miso_pb5

SPI2_MOSI-----G15 ---------->spi2_mosi_pb4

SPI2_CLK------H14 --------->spi2_sck_pb6

可以到核心内的SPI2已经被用来干别的了,你自己的载板,如果没有被使用,你可以修改DTB,改回单纯的SPI使用。同理,SPI4,也就是官方开发套件中,对应的SPI0,你也可以根据自己需要改出来用,这也是我们今天主要讲的内容。所以整理一下,确认我们可以正常使用的SPI资源其实有3路,在此说明一下管脚对应关系,这个和OEM说明中有点小区别,尤其是CS信号

#SPI1 Tegra X1 Signal Name

SIP1_CS0------E14 ---------->spi1_cs0_pc3

SPI1_MOSI-----F13 ---------->spi1_miso_pc1

SPI1_MOSI-----F14 ---------->spi1_mosi_pc0

SPI1_CLK------G13 ---------->spi1_sck_pc2

SIP1_CS1------E13 ---------->spi1_cs1_pc4

#SPI0 Tegra X1 Signal Name

SIP0_CS0------F3 ---------->spi4_cs0_pc6

SPI0_MISO-----E4 ---------->spi4_miso_pd0

SPI0_MOSI-----F4 ---------->spi4_mosi_pc7

SPI0_CLK------E3 --------->spi4_sck_pc5

#SPI2 Tegra X1 Signal Name

SIP2_CS0------G16 ---------->spi2_cs0_pb7

SIP2_CS1------F16 ---------->spi2_cs1_pdd0

SPI2_MISO-----H15 ---------->spi2_miso_pb5

SPI2_MOSI-----G15 ---------->spi2_mosi_pb4

SPI2_CLK------H14 --------->spi2_sck_pb61.3 SPI在内容的对应地址关系

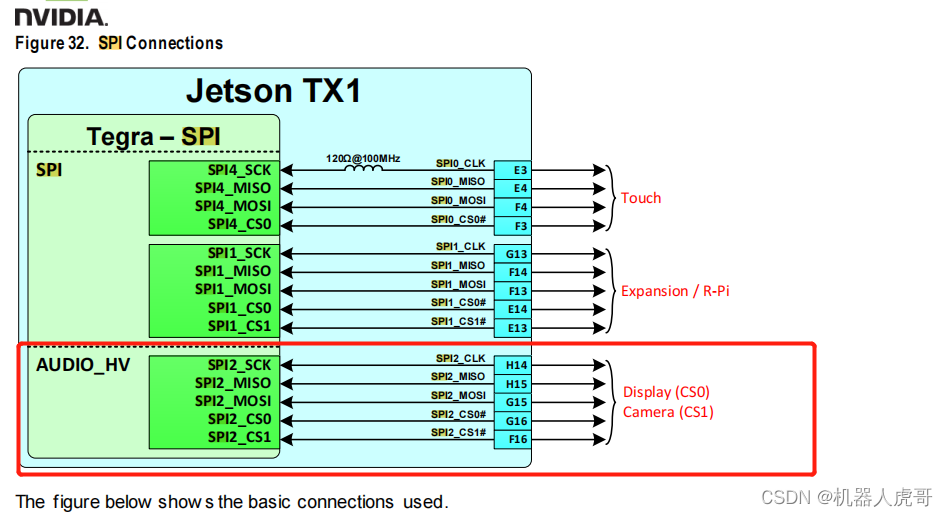

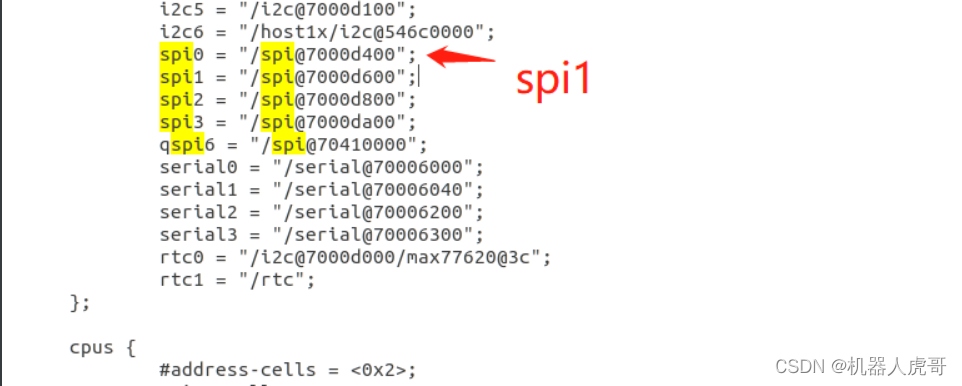

在nvidia JetPack 4.6.1以后的版本,都是使用DTB文件来描述定义硬件,在这些描述文件中,SPI控制器有一定的对应关系,这里就直接罗列,大家看的时候,只要可以看到想起到这里来查找就可以。

#JetPack4.6.2 对应 R32.7.2中地址对应关系

#开发板上的对应 #核心模块的对应

spi0 = "/spi@7000d400"; ---------->SPI1 ---------->SPI1

spi1 = "/spi@7000d600"; ---------->SPI2 ---------->SPI2

spi2 = "/spi@7000d800"; ---------->SPI3 ---------->SPI3

spi3 = "/spi@7000da00"; ---------->SPI0 ---------->SPI4

qspi6 = "/spi@70410000";我们要使用这些SPI设备,就需要再DTB文件中修改对应的配置和描述,来使能初始化SPI控制器,这样我们在系统中才能正常使用

1.4 TX1官方开发条件40P外部接口中的SPI说明

C02 开发套件中40 Pin接口定义,兼容 TX2 有些 TX1是没有的

TX1 40pin定义

二、A200载板+TX1 核心模块中使能SPI4 和 SPI1 控制器

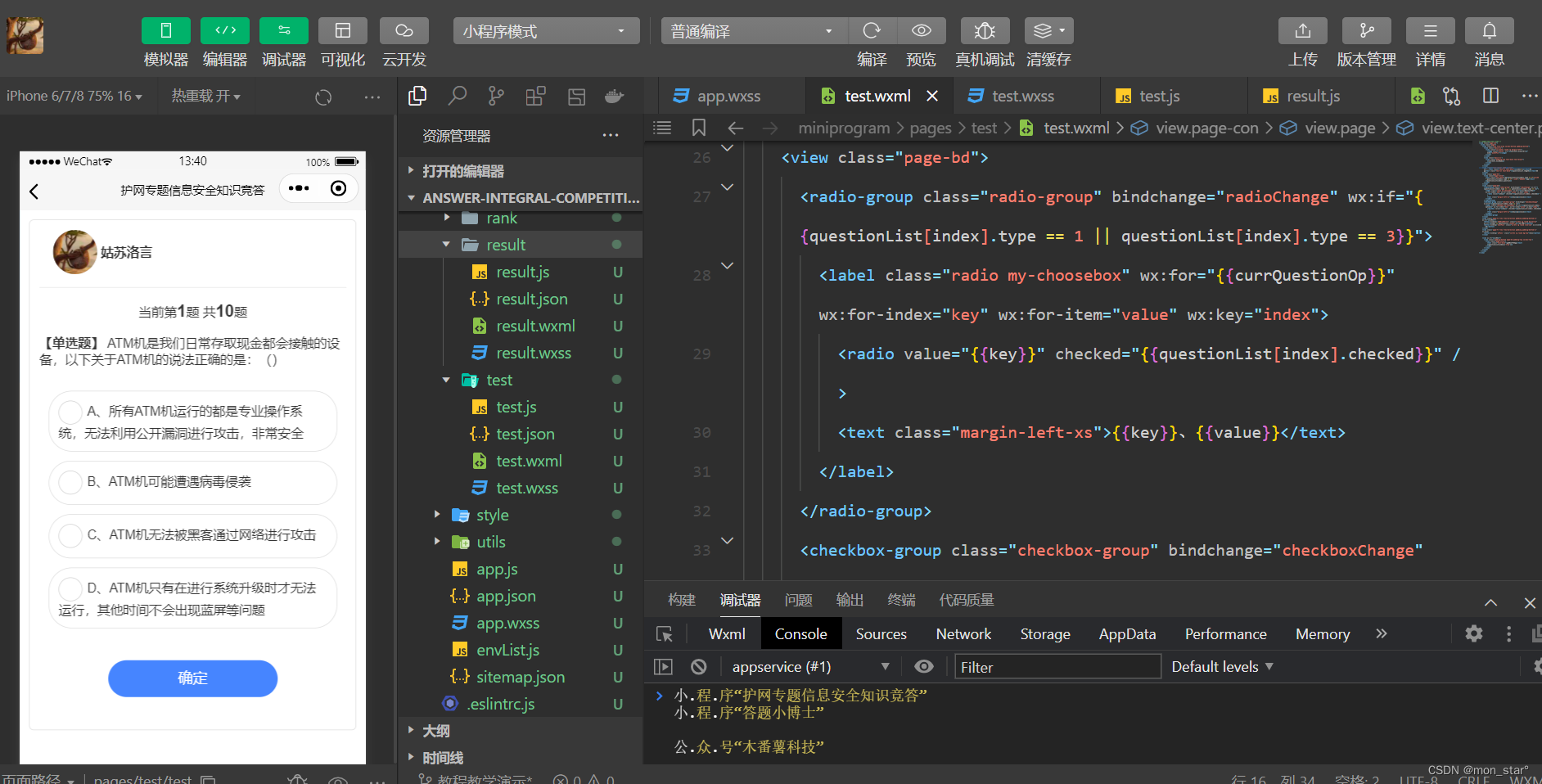

要在你的载板上,自己根据自己的原理图,使用这些硬件,你需要下载官方的开发套件对应的内核源码,然后自己修改编译对应的DTB文件,当时有人对于一些小修改,采取的反编译DTB文件至DTS文件后,修改完毕后在编译成DTB文件替换使用,这样对于小的修改时没有问题的,但是并不是很助于理解整体DTB 官方套件的组织逻辑,导致后续增加外设就不是很容易。所以我们还是从官方下载源码后,自己修改后编译成对应载板的DTB文件。

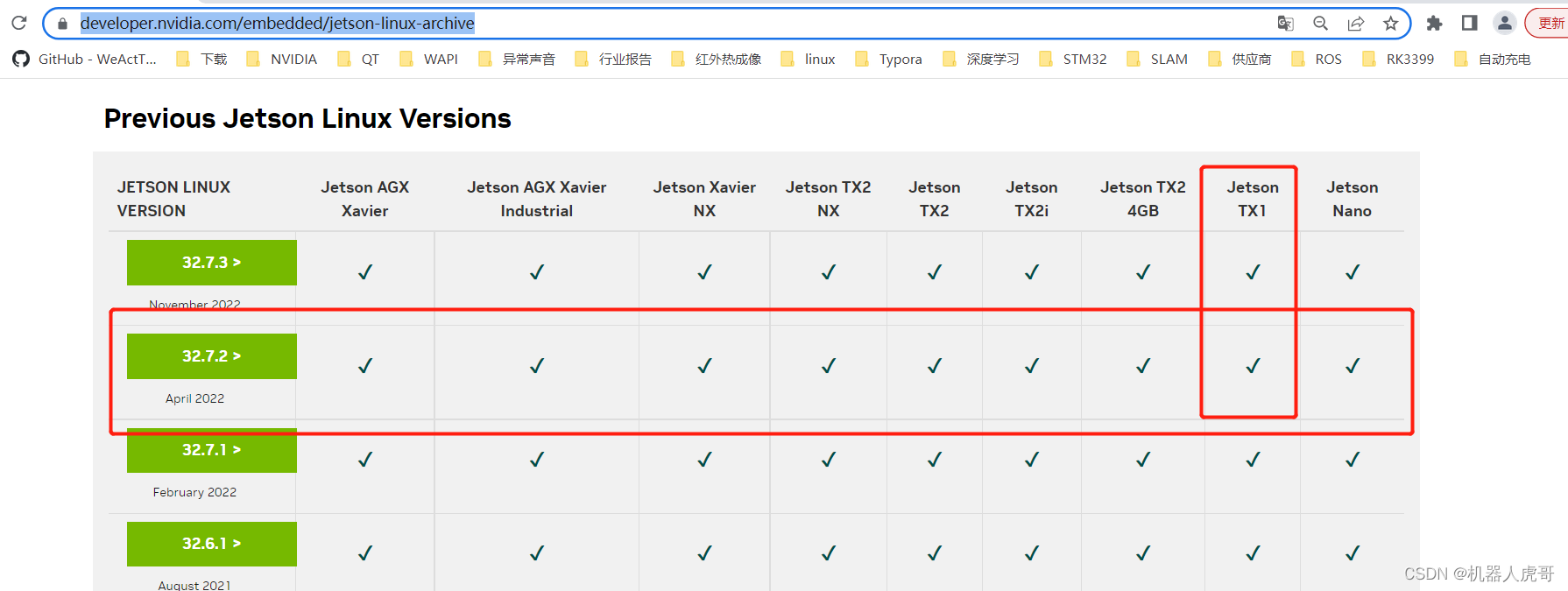

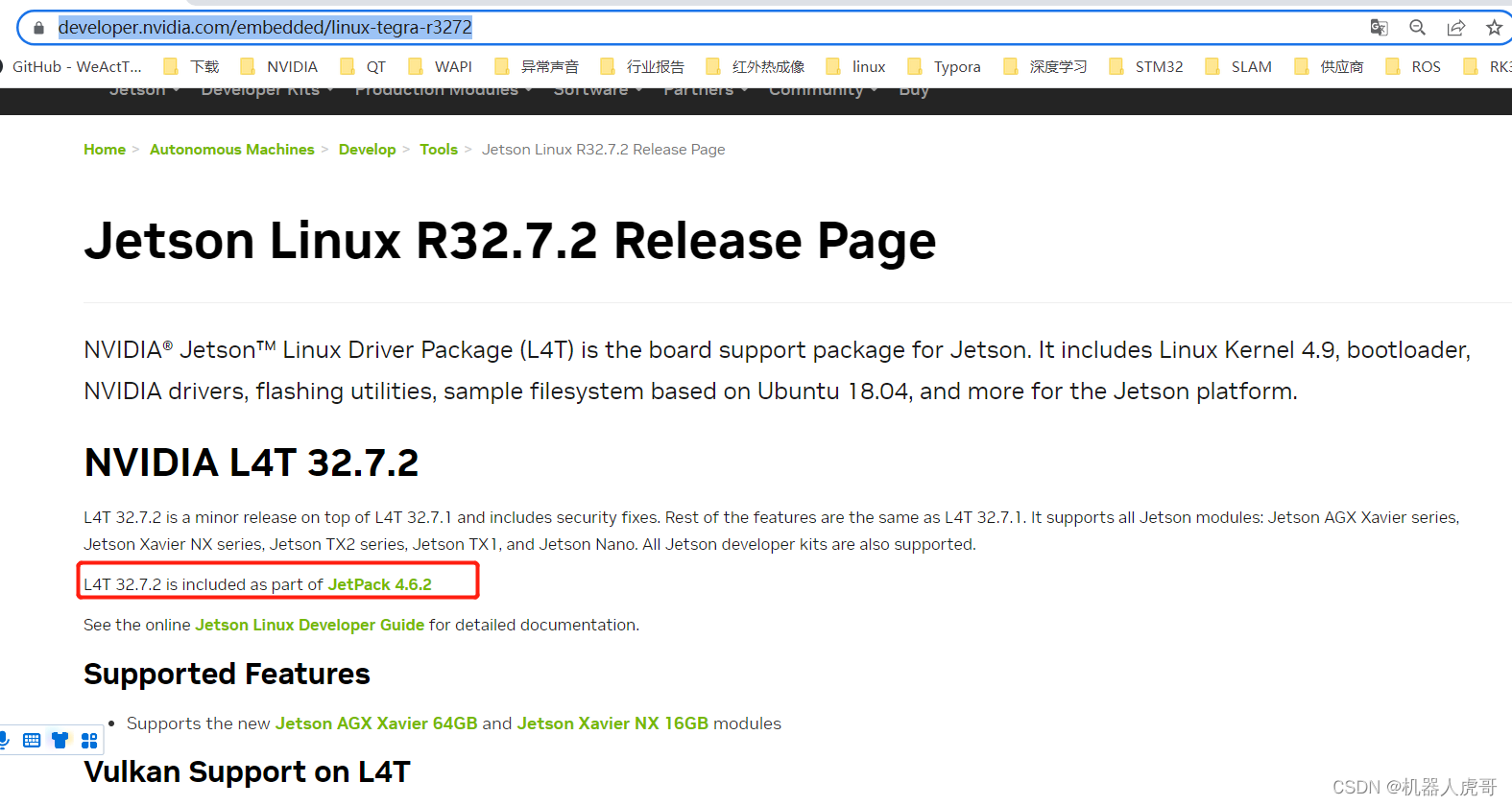

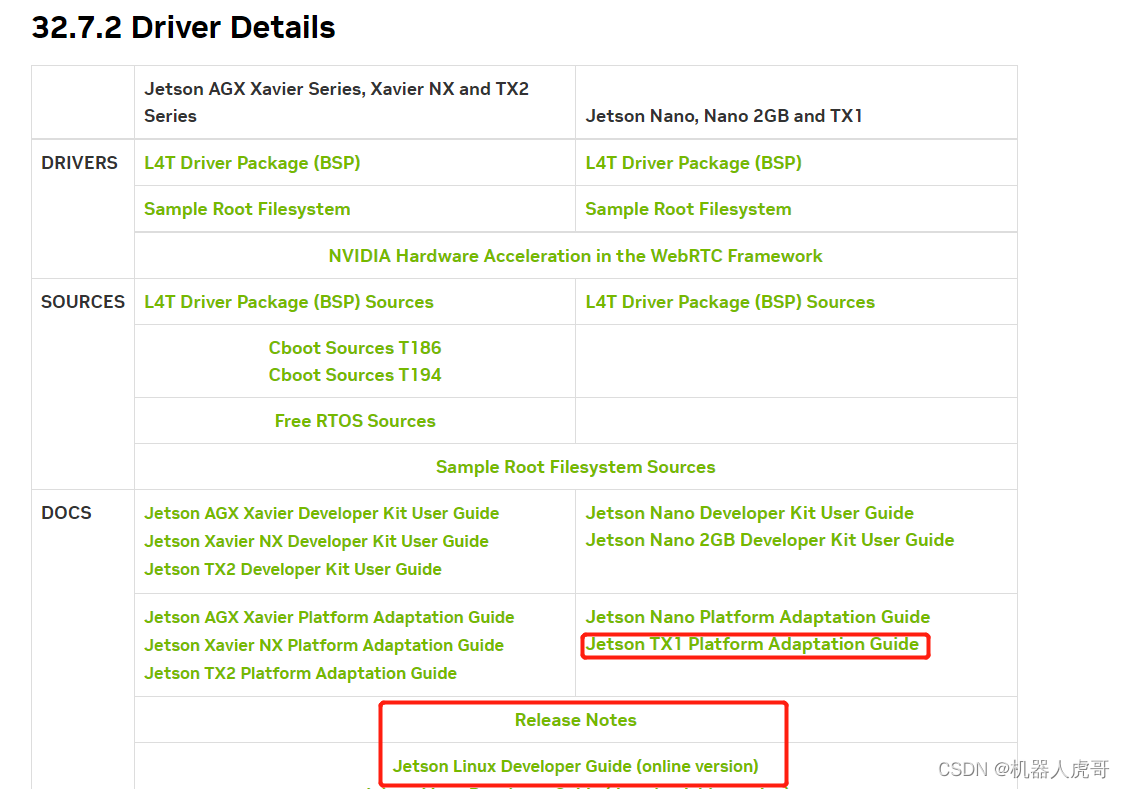

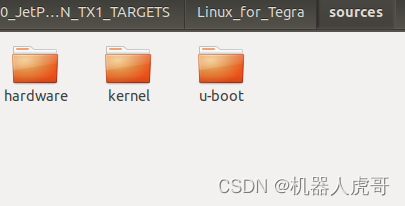

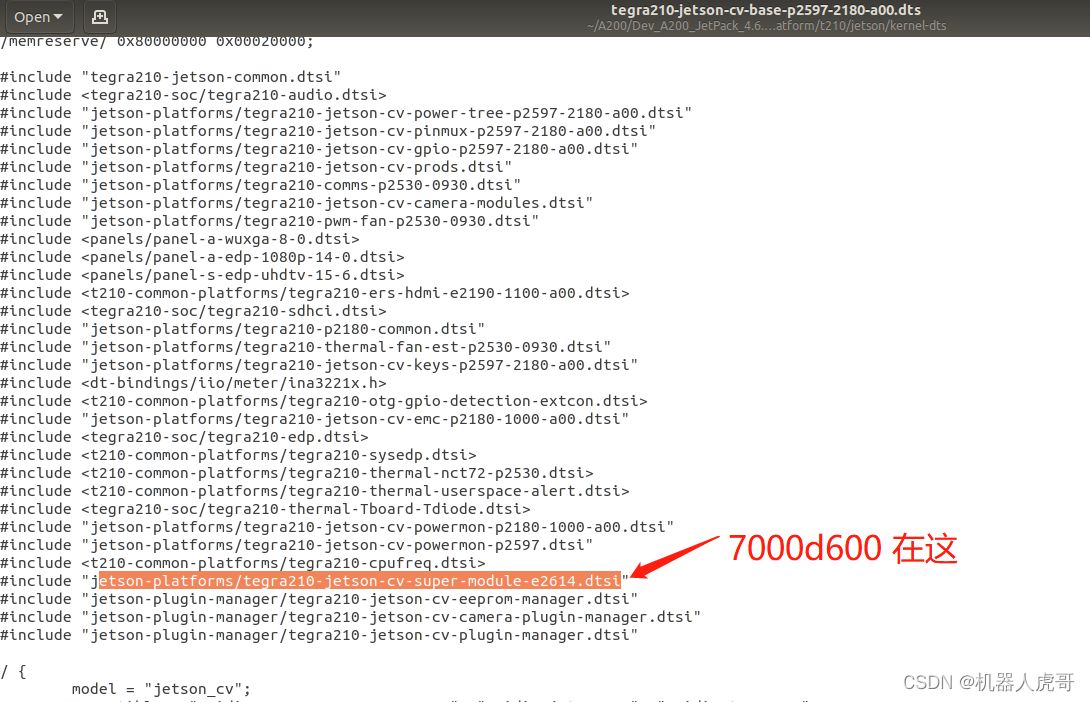

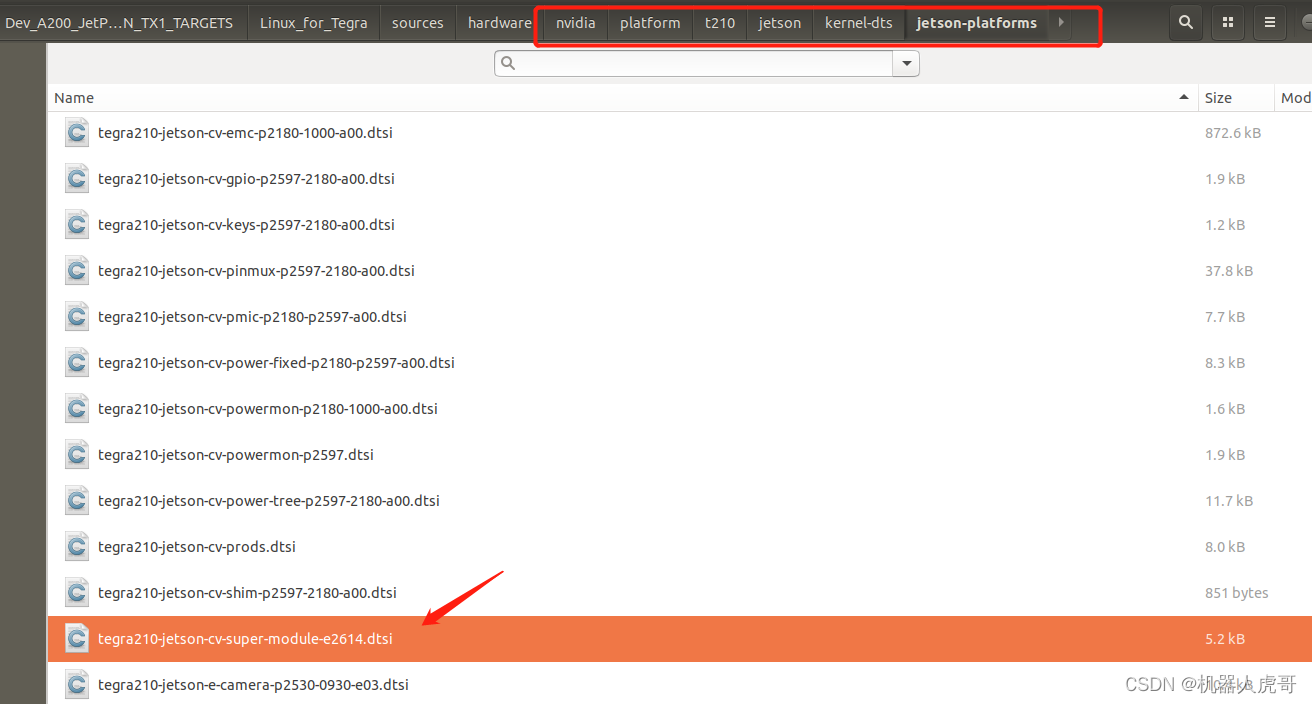

JetPack 4.6.2 对应内核源码是R32.7.2版本,在Jetson Linux Archive找到后,下载,按照步骤大家环境,我自己下载完,搭建环境后,在sources目录下存在这3个文件。Jetson Linux Archive | NVIDIA Developer

进入:Jetson Linux R32.7.2 Release Page | NVIDIA Developer

参考这些文件,完成对应的环境搭建。

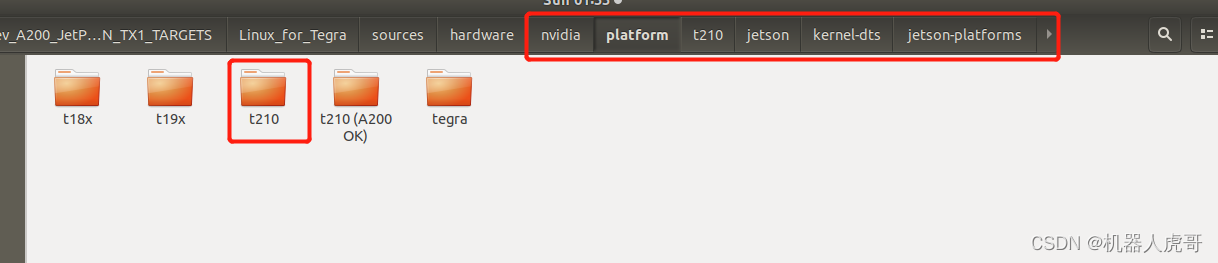

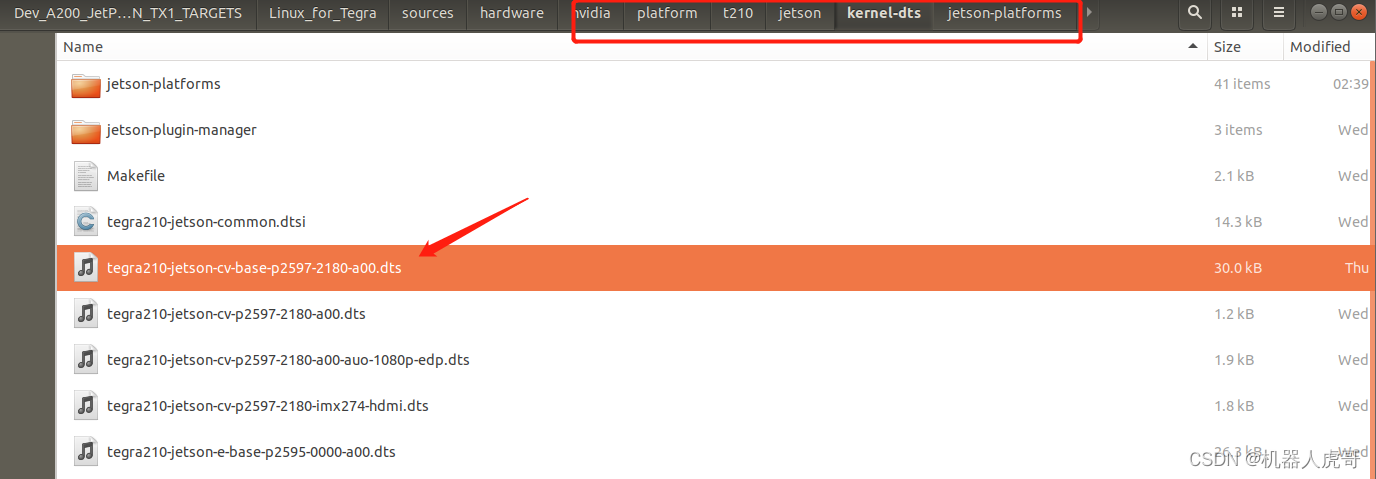

DTB文件就在hardware文件夹下。找到对应平台的,我们是TX1,所以进入t210下。

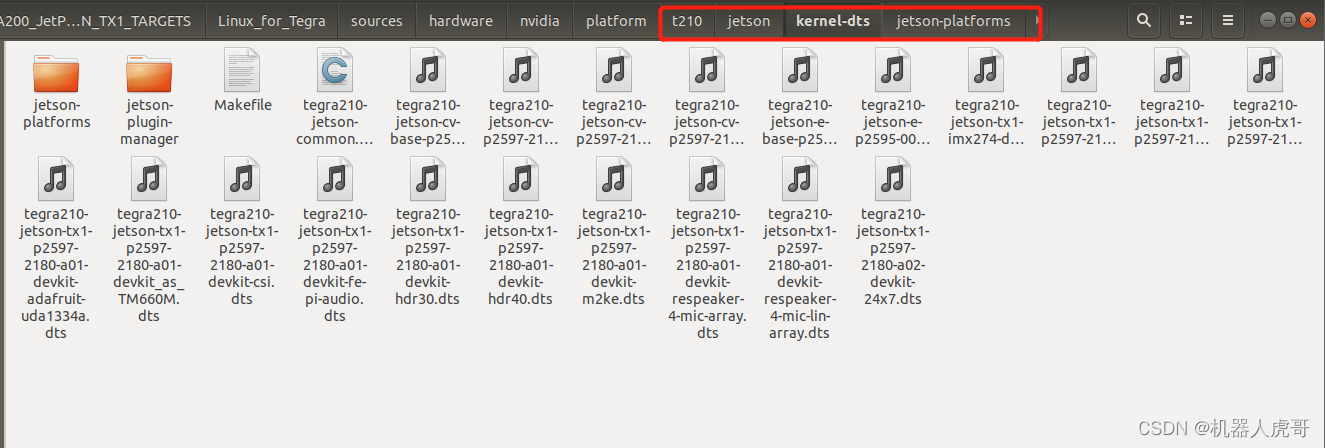

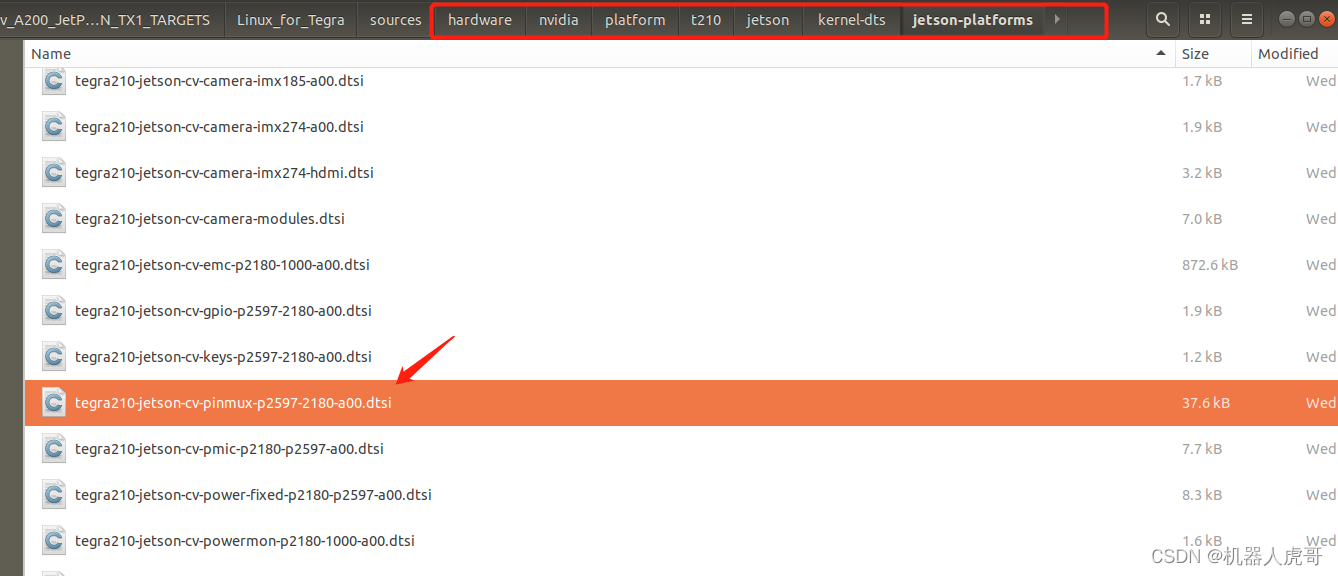

大部分我们目标要改的文件都在这个目录下:

2.1 修改所有SPI对应的引脚定义

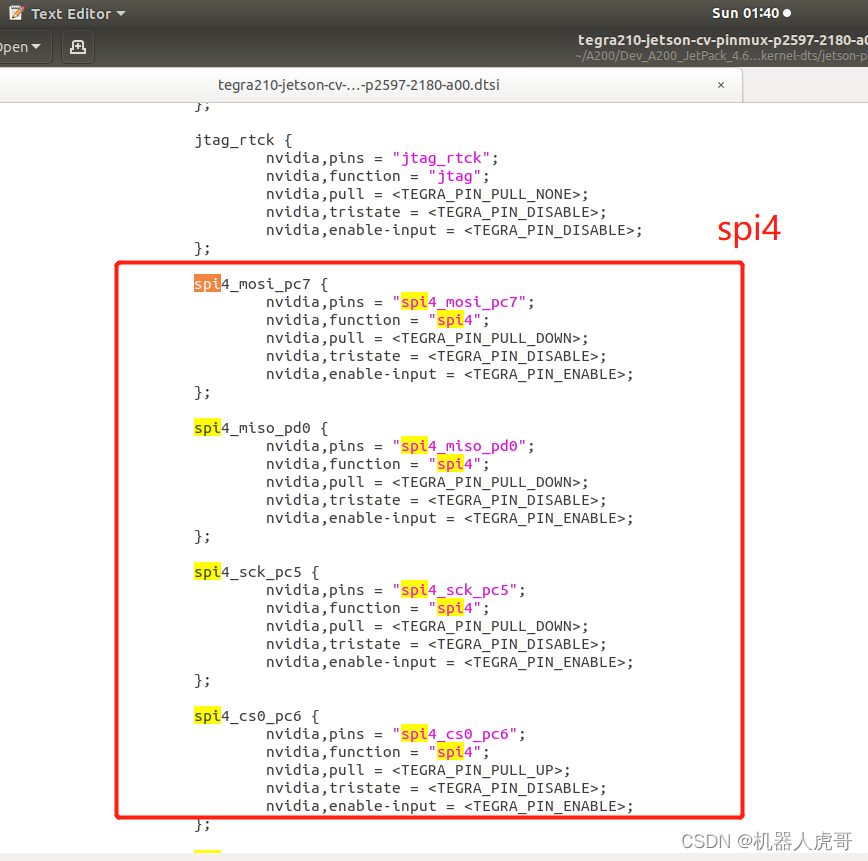

在内核中,首先要使能所在设备对应的IO管脚至,我们需要的功能上。找到这个文件:tegra210-jetson-cv-pinmux-p2597-2180-a00.dtsi

打开后搜索SPI

1、spi4 Pin原始定义:

/* spi4 Pin Configuration */

spi4_mosi_pc7 {

nvidia,pins = "spi4_mosi_pc7";

nvidia,function = "spi4";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

spi4_miso_pd0 {

nvidia,pins = "spi4_miso_pd0";

nvidia,function = "spi4";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

spi4_sck_pc5 {

nvidia,pins = "spi4_sck_pc5";

nvidia,function = "spi4";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

spi4_cs0_pc6 {

nvidia,pins = "spi4_cs0_pc6";

nvidia,function = "spi4";

nvidia,pull = <TEGRA_PIN_PULL_UP>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

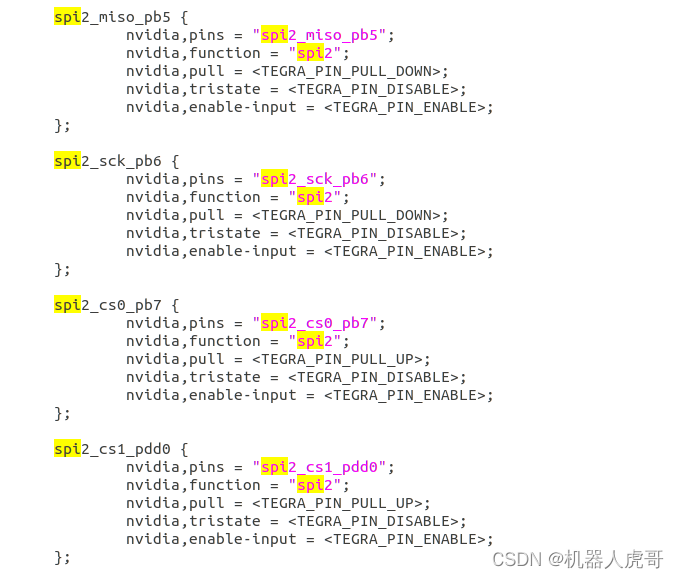

};2、spi2 Pin原始定义:

/* spi2 Pin Configuration */

spi2_mosi_pb4 {

nvidia,pins = "spi2_mosi_pb4";

nvidia,function = "spi2";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

spi2_miso_pb5 {

nvidia,pins = "spi2_miso_pb5";

nvidia,function = "spi2";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

spi2_sck_pb6 {

nvidia,pins = "spi2_sck_pb6";

nvidia,function = "spi2";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

spi2_cs0_pb7 {

nvidia,pins = "spi2_cs0_pb7";

nvidia,function = "spi2";

nvidia,pull = <TEGRA_PIN_PULL_UP>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

spi2_cs1_pdd0 {

nvidia,pins = "spi2_cs1_pdd0";

nvidia,function = "spi2";

nvidia,pull = <TEGRA_PIN_PULL_UP>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

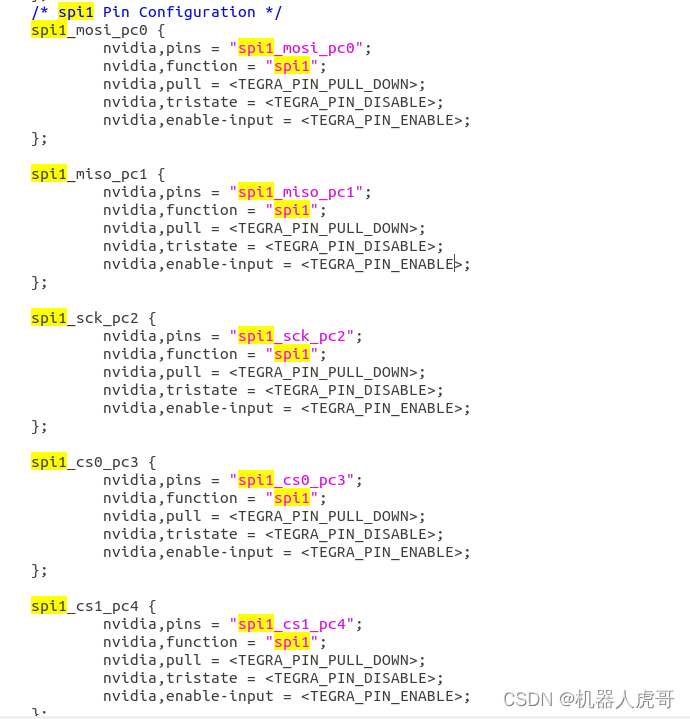

};3、spi1 Pin原始定义:

/* spi1 Pin Configuration */

spi1_mosi_pc0 {

nvidia,pins = "spi1_mosi_pc0";

nvidia,function = "rsvd1";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

spi1_miso_pc1 {

nvidia,pins = "spi1_miso_pc1";

nvidia,function = "rsvd1";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

spi1_sck_pc2 {

nvidia,pins = "spi1_sck_pc2";

nvidia,function = "rsvd1";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

spi1_cs0_pc3 {

nvidia,pins = "spi1_cs0_pc3";

nvidia,function = "rsvd1";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

spi1_cs1_pc4 {

nvidia,pins = "spi1_cs1_pc4";

nvidia,function = "rsvd1";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};3路SPI对比发现,只有套件原理图中SPI0,也就是内核描述中的SPI4,是一个片选CS信号,其余两个SPI控制器都有两个CS片选信号,意味着我们可以接不通的SPI设备在同一个SPI控制器上。这与我们再TX1模块的说明书中的说明也是一致的。

我们对比几个发现,其实只有SPI1默认是没有初始化的,所以我们需要初始化SPI1的管脚

我们对比几个发现,其实只有SPI1默认是没有初始化的,所以我们需要初始化SPI1的管脚

4、spi1 Pin初始化管脚定义修改

对于其余两路,这几个地方都需要修改,修改后:

/* spi1 Pin Configuration */

spi1_mosi_pc0 {

nvidia,pins = "spi1_mosi_pc0";

nvidia,function = "spi1";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

spi1_miso_pc1 {

nvidia,pins = "spi1_miso_pc1";

nvidia,function = "spi1";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

spi1_sck_pc2 {

nvidia,pins = "spi1_sck_pc2";

nvidia,function = "spi1";

nvidia,pull = <TEGRA_PIN_PULL_DOWN>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

spi1_cs0_pc3 {

nvidia,pins = "spi1_cs0_pc3";

nvidia,function = "spi1";

nvidia,pull = <TEGRA_PIN_PULL_UP>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

spi1_cs1_pc4 {

nvidia,pins = "spi1_cs1_pc4";

nvidia,function = "spi1";

nvidia,pull = <TEGRA_PIN_PULL_UP>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};2.2 修改所有SPI设备详细初始化定义

上一节我们修改了IO管脚定义,下面我们就要描述是设备初始化了,这个地方我们要用到SPI控制器对应内核中的地址问题,回顾一下对应关系:

#JetPack4.6.2 对应 R32.7.2中地址对应关系

#开发板上的对应 #核心模块的对应

spi0 = "/spi@7000d400"; ---------->SPI1 ---------->SPI1

spi1 = "/spi@7000d600"; ---------->SPI2 ---------->SPI2

spi2 = "/spi@7000d800"; ---------->SPI3 ---------->SPI3

spi3 = "/spi@7000da00"; ---------->SPI0 ---------->SPI4

qspi6 = "/spi@70410000";我们需要全部都使能成我们可以自由使用的SPI设备,原理图管脚上应该是SPI1、SPI2、SPI0 ,内核中的对应关系应该是SPI1、SPI2 、SPI4 ,也就是我们其实需要使用到如下地址:

#JetPack4.6.2 对应 R32.7.2中地址对应关系

#开发板上的对应 #核心模块的对应

spi0 = "/spi@7000d400"; ---------->SPI1 ---------->SPI1

spi1 = "/spi@7000d600"; ---------->SPI2 ---------->SPI2

spi3 = "/spi@7000da00"; ---------->SPI0 ---------->SPI4 1、spi0 = "/spi@7000d400"; ---------->SPI1修改:

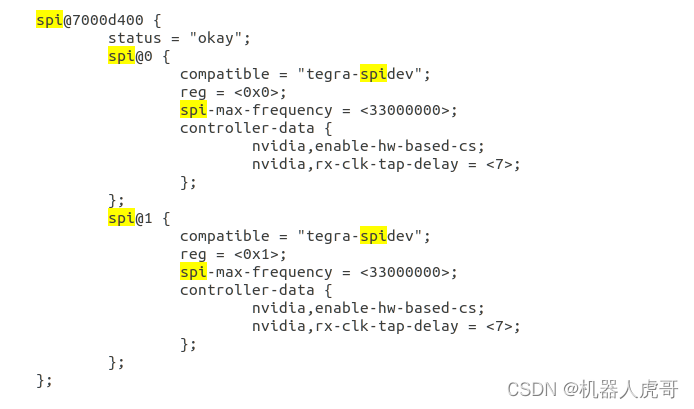

这一路是最好找的,因为,这一路内核中的管脚名称和板子上的名称是一致的,同时也是官方引出到外部40-Pin接口上的SPI,所以官方套件中肯定有关于SPI1的描述:

打开这个文件,搜索SPI,找到/spi@7000d400位置:

spi@7000d400 {

status = "okay";

spi@0 {

compatible = "tegra-spidev";

reg = <0x0>;

spi-max-frequency = <33000000>;

controller-data {

nvidia,enable-hw-based-cs;

nvidia,rx-clk-tap-delay = <7>;

};

};

spi@1 {

compatible = "tegra-spidev";

reg = <0x1>;

spi-max-frequency = <33000000>;

controller-data {

nvidia,enable-hw-based-cs;

nvidia,rx-clk-tap-delay = <7>;

};

};

};可以看到,由于有两个片选,所以增加了两个描述,CS0对应 SPI@0,CS1对应spi@1,我们由于只使用了CS0,所以只需要一个设备描述即可。

修改后:

spi@7000d400 {

status = "okay";

spi@0 {

compatible = "tegra-spidev";

reg = <0x0>;

spi-max-frequency = <33000000>;

status = "ok";

controller-data {

nvidia,enable-hw-based-cs;

nvidia,rx-clk-tap-delay = <7>;

};

};

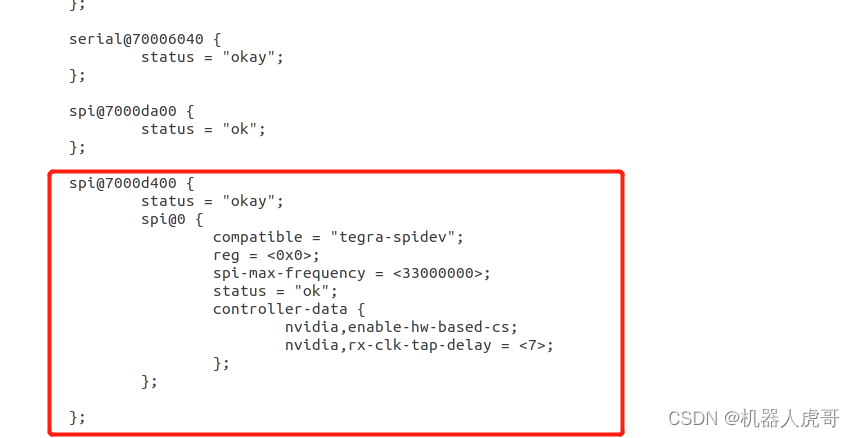

};2、spi3 = "/spi@7000da00"; ---------->SPI0---------->SPI4 修改:

原始的,并没有做设备描述,只是使能了控制器,我们也需要使用1路CS0,所以增加一路设备描述

修改后:

spi@7000da00 {

status = "ok";

spi@0 {

compatible = "tegra-spidev";

reg = <0x0>;

spi-max-frequency = <33000000>;

status = "ok";

controller-data {

nvidia,enable-hw-based-cs;

nvidia,rx-clk-tap-delay = <7>;

};

};

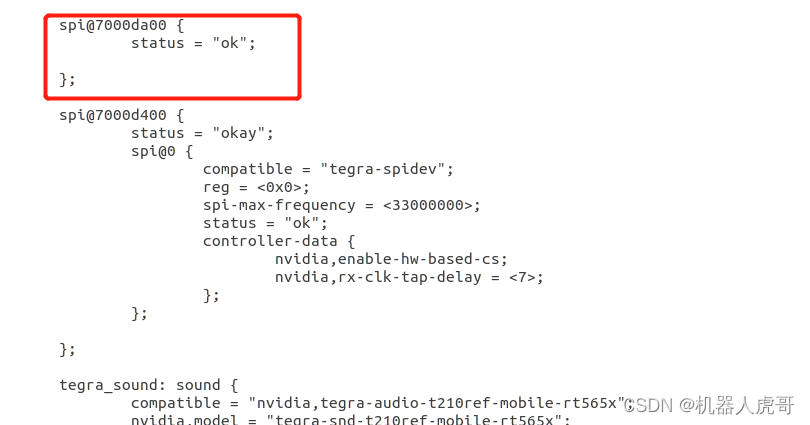

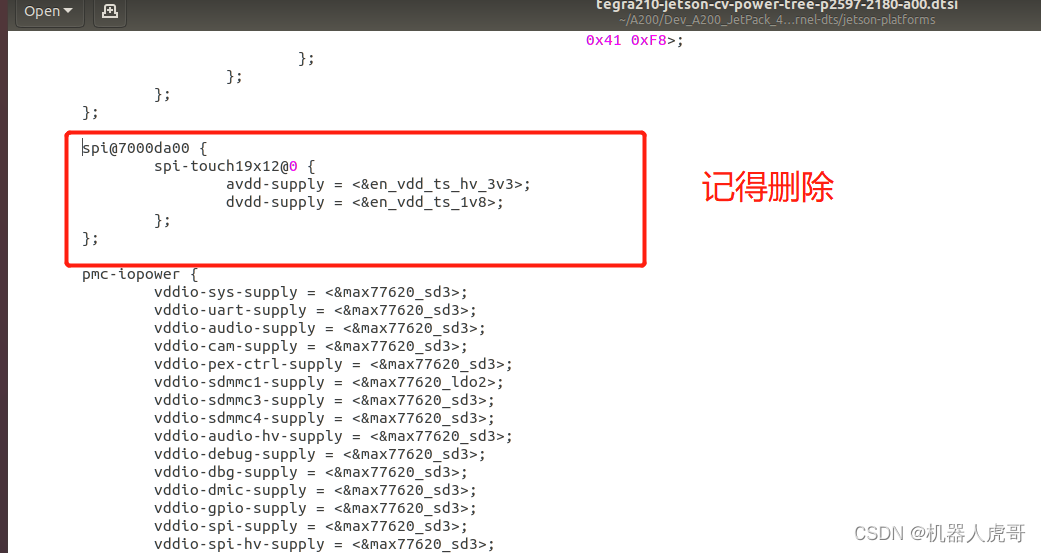

};tegra210-jetson-cv-power-tree-p2597-2180-a00.dtsi 文件中还有原来的残留描述,我们可以删除掉。

t210-common-platforms/tegra210-ers-touch-e1937-1000-a00.dtsi

spi@7000da00 {

spi-touch19x12@0 {

avdd-supply = <&en_vdd_ts_hv_3v3>;

dvdd-supply = <&en_vdd_ts_1v8>;

};

};删除后继续下一步。

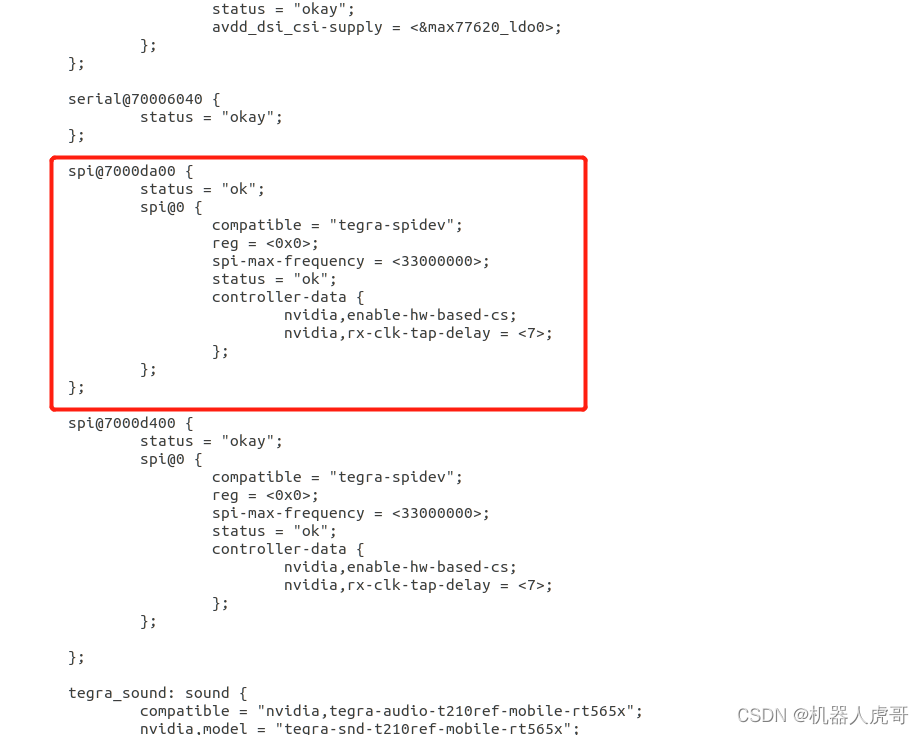

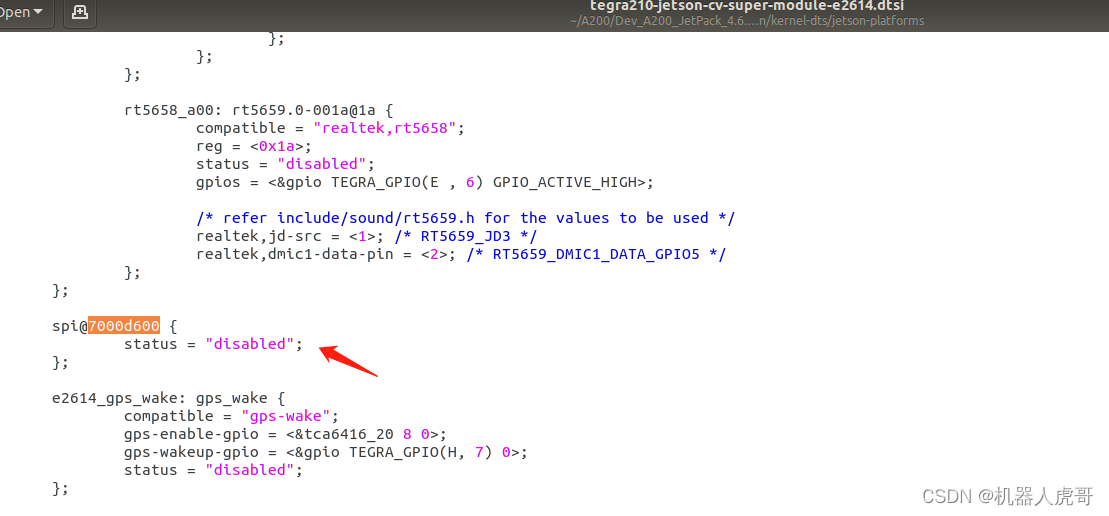

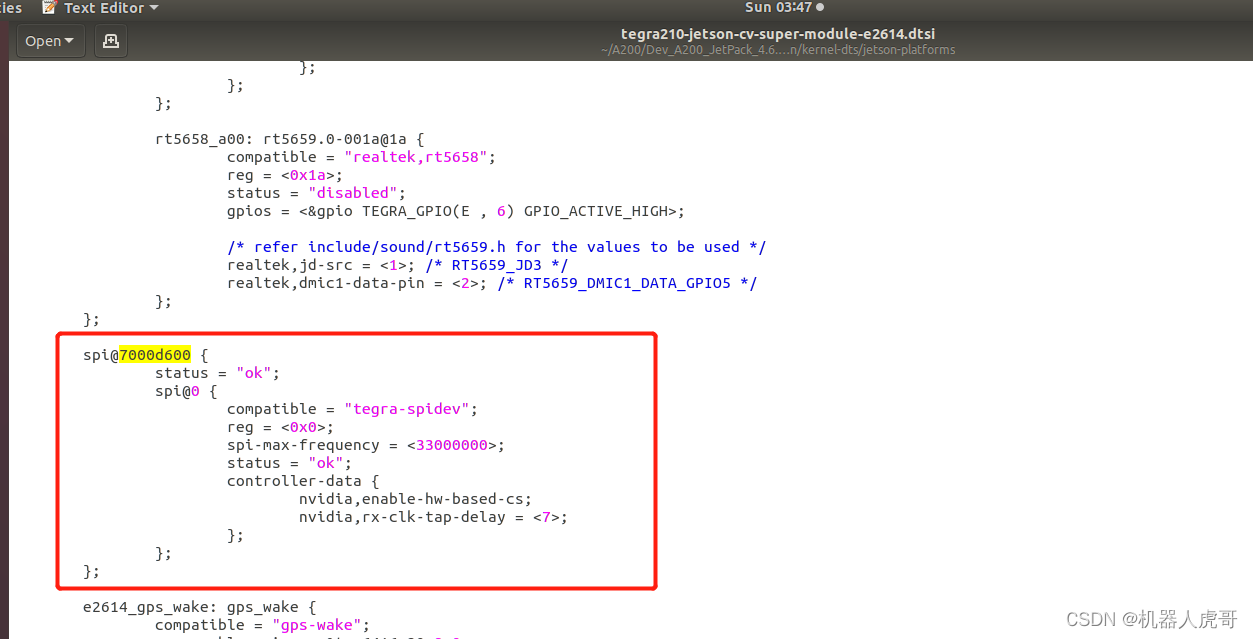

3、spi1 = "/spi@7000d600"; ---------->SPI2---------->SPI2 修改:

最后这个就比较难找了,是因为这个接口被用做了Touch的接口,修改位置在这文件:jetson-platforms/tegra210-jetson-cv-super-module-e2614.dtsi

进入后,搜索7000d600

spi@7000d600 {

status = "disabled";

};由于我们也不用touch 这类东西,我们可以修改,内核中的SPI2有两个CS引脚,我们也是只用一个:

spi@7000d600 {

status = "ok";

spi@0 {

compatible = "tegra-spidev";

reg = <0x0>;

spi-max-frequency = <33000000>;

status = "ok";

controller-data {

nvidia,enable-hw-based-cs;

nvidia,rx-clk-tap-delay = <7>;

};

};

};2.3 小技巧:

如果不确定有些内容在哪个文件内,我们可以采用模糊搜索的方法搞定

# 查找所有包含 timersub关键字的文件

find / -name '*' | xargs grep 'timersub'

#搜索当前目录

find ./ -name '*' | xargs grep 'spi'

find ./ -name '*' | xargs grep '7000d600'

find ./ -name '*' | xargs grep '7000da00'

find ./ -name '*' | xargs grep 'osc'

find ./ -name '*' | xargs grep 'tegra210-p3448-0003-p3542-0000.h'

find ./ -name '*' | xargs grep 'exp-header-pinmux'

find ./ -name '*' | xargs grep 'hdr40_spi1'

./t210/porg/kernel-dts/tegra210-porg-p3448-common.dtsi: hdr40_spi1: spi@7000d400 { /* SPI 1 to 40 pin header */

#模糊查询

sudo find ./ -iname "tegra210-p3448-0003-p3542-0000.h"

sudo find ./ -iname "*.dtbo"

sudo find ./ -iname "*overlay*"

find ./ -name '*' | xargs grep 'jetson-mcp251x.dts'

./run/udev/data/+module:overlay

./sys/module/overlay

./sys/firmware/devicetree/base/plugin-manager三、编译DTS文件至DTB文件,更新系统

3.1 编译烧写

#这是我自己的目录,大家根据自己的目录,这句要做修改

export DEVDIR=$HOME/A200/Dev_A200_JetPack_4.6.2_Linux_JETSON_TX1_TARGETS/Linux_for_Tegra

cd $DEVDIR/

#如果第一次执行,记得建立这些文件夹,后续就不需要重复这些了

mkdir -p $DEVDIR/images/modules

mkdir -p $DEVDIR/images/packages

mkdir -p $DEVDIR/images/dtb

#如果第一次执行,指定交叉编译器

export CROSS_COMPILE=/opt/gcc-linaro-7.3.1-2018.05-x86_64_aarch64-linux-gnu/bin/aarch64-linux-gnu-

export KERNEL_MODULES_OUT=$DEVDIR/images/modules

export TEGRA_KERNEL_OUT=$DEVDIR/images

export ARCH=arm64

export LOCALVERSION=-tegra

cd $DEVDIR/sources/kernel/kernel-4.9

#如果没有安装过,请安装

sudo apt-get install libncurses5 libncurses5-dev

sudo apt install make

sudo apt install make-guile

#清理系统,不用每次都清理

make mrproper

make ARCH=arm64 O=$TEGRA_KERNEL_OUT tegra_defconfig

#make ARCH=arm64 O=$TEGRA_KERNEL_OUT tegra21_defconfig

#make O=$TEGRA_KERNEL_OUT tegra18_defconfig

#配置你想要的内核,不配置也进去做一下保存推出

make O=$TEGRA_KERNEL_OUT menuconfig

#下面就是编译内核、设备树和模块,只想下面的命令。

#make O=$TEGRA_KERNEL_OUT zImage //内核

#我们只需要编译设备树

make O=$TEGRA_KERNEL_OUT dtbs //设备树

make O=$TEGRA_KERNEL_OUT zImage //内核

make O=$TEGRA_KERNEL_OUT Image //内核

make O=$TEGRA_KERNEL_OUT dtbs Image //内核

make O=$TEGRA_KERNEL_OUT dtbs //设备树

make O=$TEGRA_KERNEL_OUT modules

make O=$TEGRA_KERNEL_OUT modules_install INSTALL_MOD_PATH=$KERNEL_MODULES_OUT转移覆盖

#拷贝TX1 对应 转移文件

cp $DEVDIR/images/arch/arm64/boot/dts/tegra210-* $DEVDIR/images/dtb/

#把文件从上述目录,再拷贝到内核烧写文件夹下

mv -f $DEVDIR/images/dtb/* $DEVDIR/kernel/dtb/烧写:

#这个会重新生成system.img文件

sudo ./flash.sh jetson-tx1 mmcblk0p1

#全部重新烧写 最常用推荐,使用已经有的system.img

sudo ./flash.sh -r jetson-tx1 mmcblk0p1

#只更新设备树和内核文件,会重新烧写system

sudo ./flash.sh -r -d kernel/dtb/tegra210-jetson-tx1-p2597-2180-a01-devkit.dtb -K kernel/Image jetson-tx1 mmcblk0p1

#备份拷贝系统

sudo ./flash.sh -r -k APP -G system_JetPack_4_6_2_TX1_basic_image_20230427.img jetson-tx1 mmcblk0p1

sudo ./flash.sh -r -k APP -G system_JetPack_4_6_2_TX1_spican_image_20230504-1.img jetson-tx1 mmcblk0p1

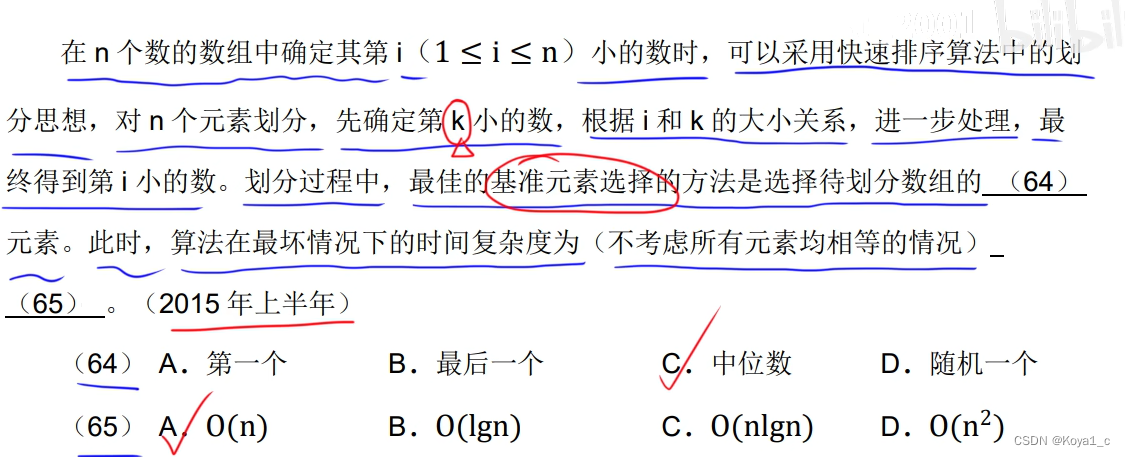

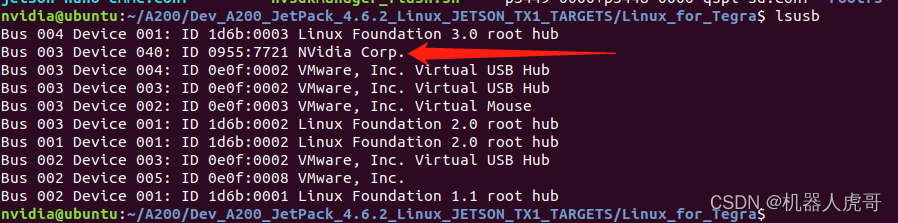

3.2 测试

1、SSH登录到板子上更新和安装

sudo apt-get update

sudo apt-get install python-pip -y

#查看默认加载设备

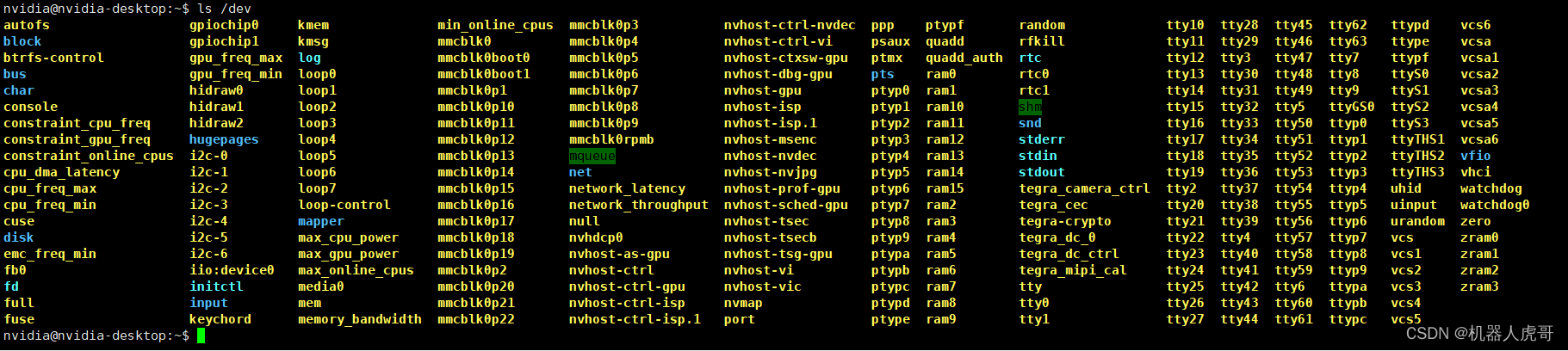

ls /dev

2、加载SPIDEV驱动

官方系统是自带SPIDEV驱动,只是启动没有加载,需要手动加载

sudo modprobe spidev

#查看加载设备

ls /dev 加载了SPI设备

加载了SPI设备

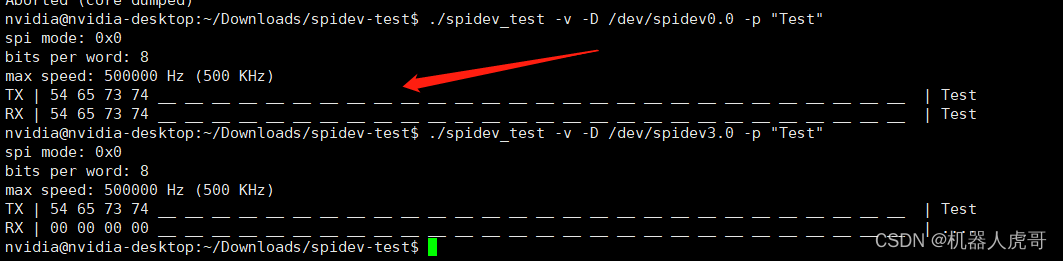

3、收发测试

git clone https://github.com/rm-hull/spidev-test

cd spidev-test/

#编译

gcc spidev_test.c -o spidev_test

#收发测试

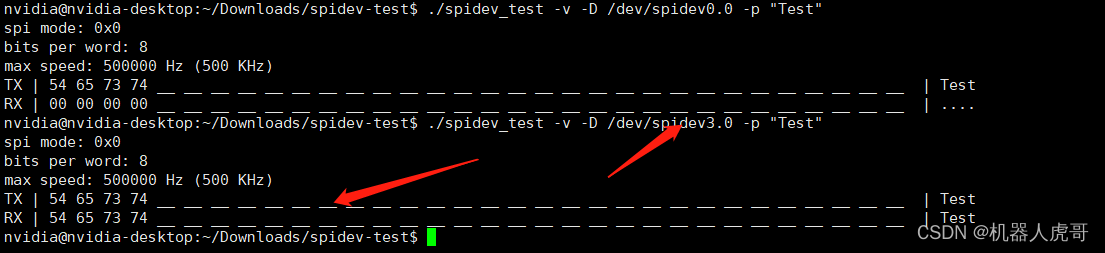

./spidev_test -v -D /dev/spidev0.0 -p "Test" 可以看到上面的是没有回复,或者没有找到设备,我们测试时需要短接MOSI和MISO管脚。短接后我们继续测试

可以看到上面的是没有回复,或者没有找到设备,我们测试时需要短接MOSI和MISO管脚。短接后我们继续测试

以上是断了了SPI1的MOSI和MISO管脚后的效果。

以上是短接了SPI4的MOSI和MISO管脚后的效果。SPI2我自己也没有引出来,所以怎么测试,以后看机会了。

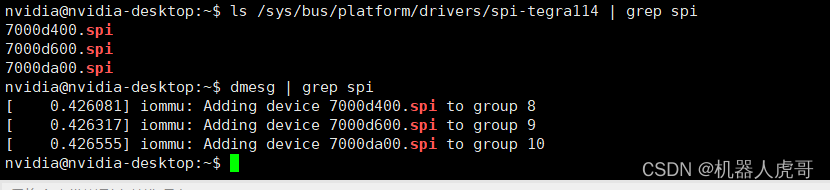

3.3 开机自动加载SPIDEV设备技巧

cd /etc/modules-load.d

#修改文件,增加一行

sudo vim modules.conf

spidev重启后,可以查看驱动是否加载:

lsmod

dmesg | grep spi

ls /sys/bus/platform/drivers/spi-tegra114 | grep spi

四、总结

整体我自己修改测试还是比较折磨人,查了很多官方资料,也实验了很多遍,折腾我3天,算是比较折磨人的一个过程,但是一旦跑通,想明白怎么回事,就有一种豁然开朗的感觉。希望大家在尝试实验的时候也玩的开心。

Have fun!

纠错,疑问,交流: 911946883@qq.com

![[架构之路-191]-《软考-系统分析师》-8-软件工程 - 解答什么是面向功能的结构化程序设计:算法+数据结构 = 程序](https://img-blog.csdn.net/20150520193305178?watermark/2/text/aHR0cDovL2Jsb2cuY3Nkbi5uZXQvc2luYXRfMjYzNDIwMDk=/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70/gravity/Center)