I.MX6U-ALPHA开发板上带有一个256MB/512MB的DDR3内存芯片,一般Cortex-A芯片自带的RAM很小,比如I.MX6U只有128KB 的 OCRAM。

如果要运行Linux的话完全不够用,所以需要外接一片RAM芯片,I.MX6U 支持 LPDDR2、LPDDR3/DDR3,I.MX6U-ALPHA开发板上选择的是 DDR3。

RAM和ROM

RAM:随机存储器,可以随时进行读写操作,速度很快,掉点以后数据会丢失。比如内存条、SRAM、DRAM、DDR等都是RAM。RAM一般用来保存程序数据、中间结果。

比如我们在程序中定义了一个变量 a,然后对这个 a 进行读写操作,示例代码如下:

int a;

a = 10;

a是一个变量,我们需要很方便地对这个变量进行读写操作,方法就是直接“a”进行读写操作,不需要在乎具体的读写过程。我们可以随意的对 RAM 中任何地址的数据进行读写操作,非常方便。

ROM:只读存储器。

比如我们买手机,通常会告诉你这个手机是 4+64 或 6+128 配置,说的就是RAM为4GB或6GB,ROM为64G或128GB。

但是这个 ROM 是 Flash,比如 EMMC 或 UFS 存储器,因为历史原因,很多人还是将Flash 叫做 ROM。但是 EMMC 和 UFS,甚至是 NAND Flash,这些都是可以进行写操作的!

只是写起来比较麻烦,要进行先擦除,然后再发送要写的地址或扇区,最后才是写入的数据。

相比于RAM,向ROM或者Flash里面写入数据要复杂很多,因为速度会变慢,但是ROM和Flash可以将容量做很大,而且掉电后数据不会丢失,适合用来存储资料,比如音乐、图片、视频信息等。

综上所述,RAM速度快,可以直接和CPU进行通信,但是掉点以后数据会丢失,不容易做大。ROM速度虽然慢,但是容量

大、适合存储数据。

对于正点原子的I.MX6U-ALPHA开发板而言,DDR3就是RAM,NANF Flash或EMMC就是ROM。

SRAM简介

static radom access memory,静态随机存储器,这里的“静态”是指只要SRAM上电,那么SRAM里面的数据就会一直保存着,直到SRAM掉电。对于RAM而言需要可以随机的读取任意一个地址空间内的数据,因此采用了地址线和数据线分离的方式。

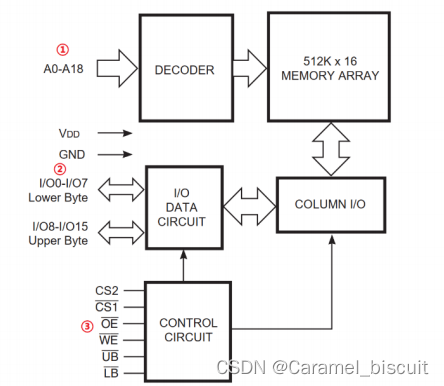

- 地址线,一共A0~A18,也就是19根地址线,因此可访问的地址大小就是2^19=524288=512KB。

- 数据线,16根数据线,一次访问可以访问16bit的数据,也就是2个字节。因此就有高字节和低字节数据之分,其中 IO0~IO7 是低字节数据,IO8~IO15 是高字节数据。

- 控制线,SRAM要工作还需要一堆的控制线,CS2和CS1是片选信号,低电平有效,在一个系统中可能会有多片SRAM,这时候就需要CS信号来选择当前使用哪片SRAM。此外,有的SRAM内部其实是由两片SRAM拼接起来的,因此就会提供两个片选信号。

OE:输出使能信号,低电平有效,主控从SRAM读取数据。

WE:写使能信号,低电平有效,主控向SRAM写数据。

UB:低电平时访问高字节。

LB:低电平时访问低字节。

SRAM价格高,SDRAM比SRAM容量大,但是价格更低。SRAM突出的特点就是无需刷新,读写速度快,所以SRAM通常作为SOC的内容RAM或Cache使用。比如 STM32 内存的 RAM 或 I.MX6U 内部的OCRAM 都是 SRAM。

SDRAM

Synchronous Dynamic Random Access Memory,同步动态随机存储器,“同步”的意思是SDRAM工作需要时钟线,“动态的意思”是SDRAM中的数据需要不断的刷新来保证数据不会丢失,“随机”的意思是可以读写任意地址的数据。

与SRAM相比,SDRAM集成度高,功耗低,成本低,适合做大量存储,但是需要定时刷新来保证数据不会丢失。SDRAM适合用来做内存条,SRAM适合做高速缓存或MCU内部的RAM。

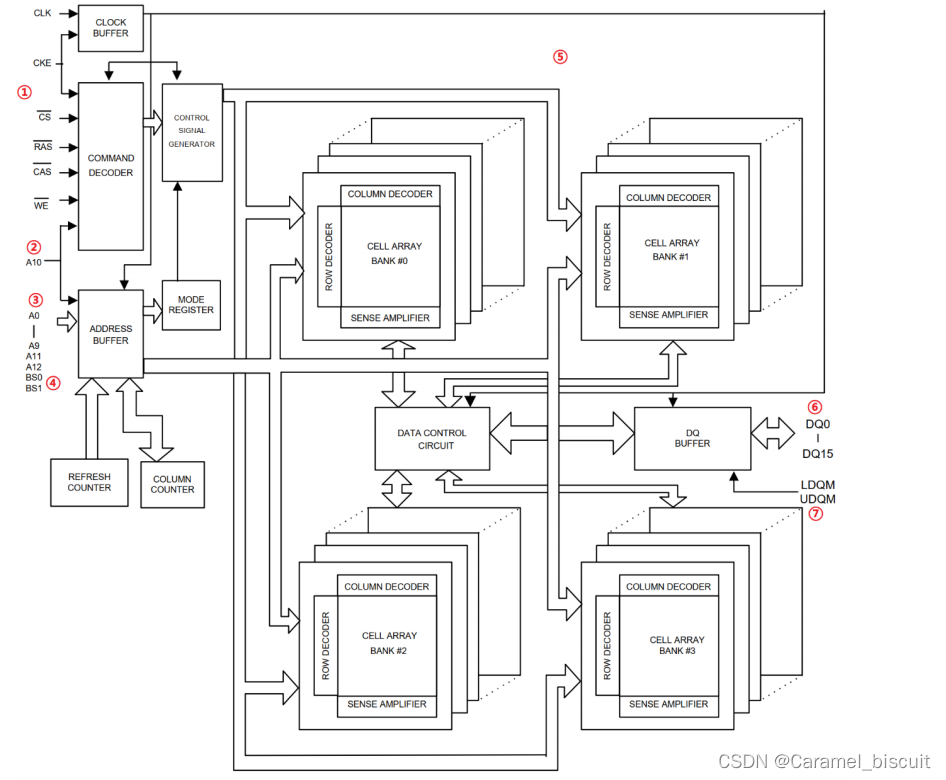

- 控制线:

CLK:时钟线,SDRAM是同步动态随机存储器,“同步”的意思是时钟,因此需要一根额外的时钟线,这和SRAM最大不同,SRAM没有时钟线。

CKE:时钟线使能信号线。

CS:片选信号

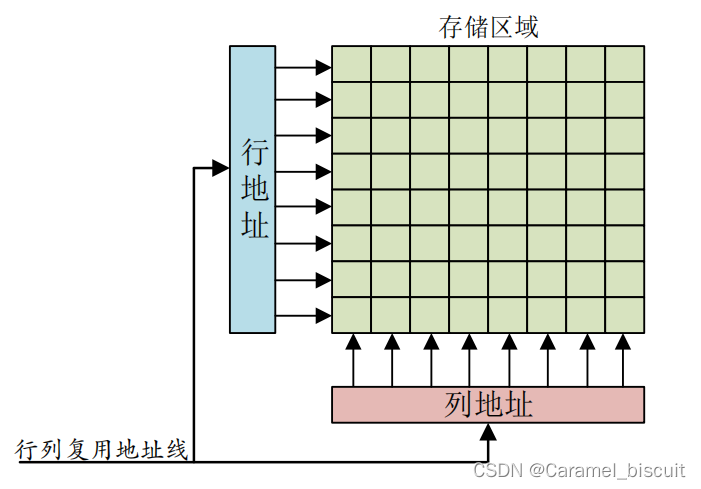

RAS:行选通信号,低电平有效,SDRAM和SRAM寻址方式不同,SDRAM按照行、列来确定某个具体的存储区域。因此就有行地址和列地址之分,行地址和列地址共同复用同一组地址线,要访问某一个地址区域,必须要发送行地址和列地址,指定要访问哪一行?哪一列?RAS是行选通信号,表示要发送行地址。

CAS:列选通信号,和RAS类似,低电平有效,选中以后就可以发送列地址了。

WE:写使能信号,低电平有效。 - A10地址线,不仅是地址线,A10还控制着Auto-precharge,也就是 预充电,SDRAM芯片内部会分为多个BANK,SDRAM在读写完成以后,如果要对同一个BANK中的另一行进行寻址操作就必须将原来有效的行关闭,然后发送新的行/列地址,关闭现在工作的行,准备打开新行的操作就叫做预充电。一般SDRAM都支持自动预充电功能。

- A0~A12 包含了行地址和列地址。不同的 SDRAM 芯

片,根据其位宽、容量等的不同,行列地址数是不同的,这个在 SDRAM 的数据手册里面会也清楚的。比如 W9825G6KH 的 A0~A8 是列地址,一共 9 位列地址,A0~A12 是行地址,一共 13位,因此可寻址范围为:29*213=4194304B=4MB,W9825G6KH 为 16 位宽(2 个字节),因此还需要对 4MB 进行乘 2 处理,得到 4*2=8MB,但是 W9825G6KH 是一个 32MB 的 SDRAM 啊,为什么算出来只有 8MB,仅仅为实际容量的 1/4。不要急,这个就是我们接下来要讲的 BANK,8MB 只是一个 BANK 的容量,W9825G6KH 一共有 4 个 BANK。 - BANK选择线:BS0和BS1是BANK选择信号线,在一片SDRAM中因为技术,成本等原因,不可能做一个全容量的 BANK。而且,因为 SDRAM 的工作原理,单一的 BANK 会带来严重的寻址冲突,减低内存访问效率。为此,人们在一片 SDRAM 中分割出多块 BANK,一般都是 2 的 n 次方,比如 2,4,8 等。图 23.1.1.2 中的⑤就是 W9825G6KH 的 4 个 BANK 示意图,每个 SDRAM数据手册里面都会写清楚自己是几 BANK。前面我们已经计算出来了一个 BANK 的大小为 8MB,那么四个 BANK 的总容量就是 8MB*4=32MB。

- BANK区域

- 数据线

- 高低字节选择

DDR

Double Data Rate SDRAM,双倍速率SDRAM,看名字就知道 DDR 的速率(数据传输速率)比 SDRAM 高 1 倍!这 1 倍的速度不是简简单单的将 CLK 提高 1 倍,

这1倍的速度不是简简单单的将CLK提高1倍,SDRAM在一个CLK周期传输一次数据,DDR在一个CLK周期传输两次数据,也就是在上升沿和下降沿各传输一次数据,这个概念叫做预取(prefetch),相当于DDR的预取为2bit。

DDR2 在 DDR 基础上进一步增加预取(prefetch),增加到了 4bit,相当于比 DDR 多读取一倍的数据,因此 DDR2 的数据传输速率就是 533~800MT/s,这个也就是大家常说的 DDR2 533、DDR2 800。当然了,DDR2 还有其他速度,这里只是说最常见的几种。