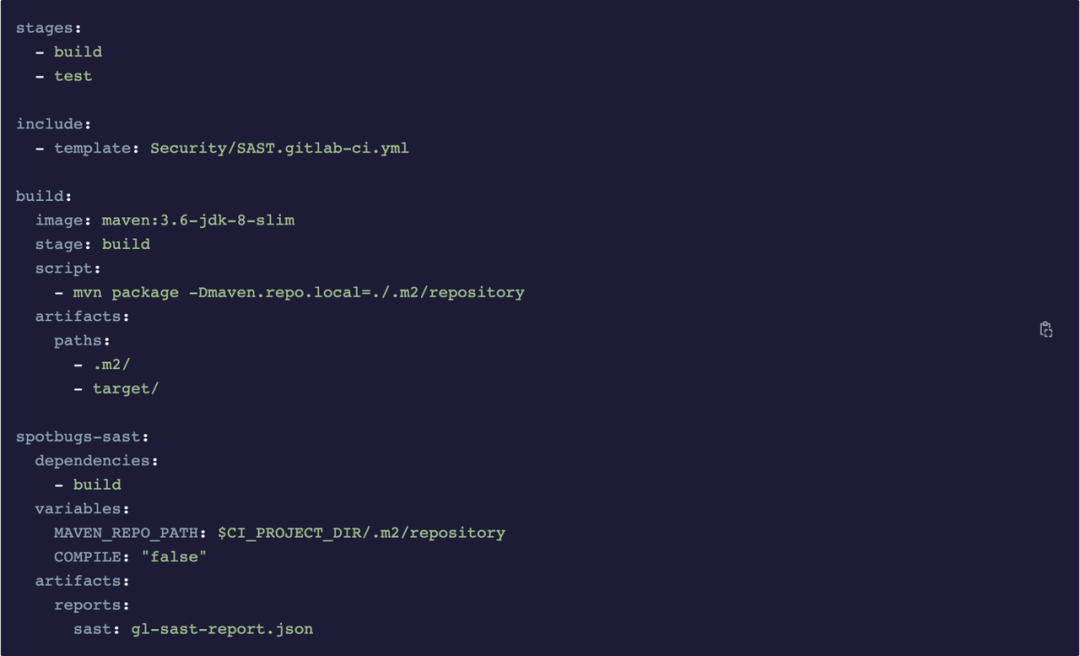

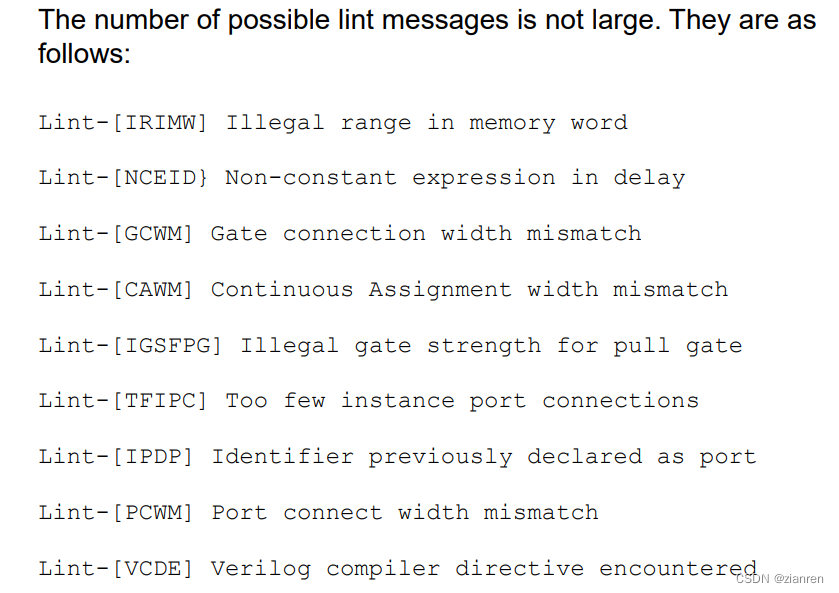

+lint

+lint=TFIPC-L

+LINT=PCWM

+lint=TFIPC-L(如果有的模块的端口定义了,但是没有连接,用这个选项,编译器会给出哪些端口没有连接)

其中CAWM貌似直接写成+lint=CAWM,vcs是不认的,得写成+lint=CAWM-L

不过CAWM的检查规则有点奇怪,等号左边(lhs)的位宽大于等号右边(rhs)的位宽时,是不报错的,有时候,等号右边(rhs)不加{ }也不报错,比如

assign cfg[1:0] = regbank[1][8:0]; 不会报错

assign cfg[1:0] = {regbank[1][8:0]}; 会报错

想要把lint的所有检查加上,可以用+lint=all

https://blog.csdn.net/weixin_49410207/article/details/124847642

ASIC中IP核的使用——包括VCS和DC

http://t.csdn.cn/0qFjz

vcs +define+

在vcs编译过程中可以通过+define+来进行传递参数或者一些控制操作,具体如下:

module test;

`ifdef A

parameter num = 123;

//XXX

`elsif B

parameter num = 456;

//XXX

`else

parameter num = 789;

//XXX

`endif

initial begin

$display("num is %0d",num);

end

endmodule

在编译命令行中加入+define+A时,num打印值为123,+define+B时为456,定义其他或者不加+define+时打印789,XXX可以为自己的一些代码。通过这种方式,可以实现定义不同参数编译不同代码的功能。

module test;

`ifdef A

parameter num = 123;

//XXX

`elsif B

parameter num = 456;

//XXX

`else

parameter num = 789;

//XXX

`endif

initial begin

$display("num is %0d",num);

$display("A is %0d",`A);

end

endmodule

在编译命令中还可以+define+A=666,实现参数的传递,num打印123,A打印666,如果此时不加=666或者不加+define+,display就会报错,miss or empty argument,因为没有数据。

module test;

`ifndef A

`define A 100

`else

`define A 200

`endif

initial begin

$display("A is %0d",`A);

end

endmodule

如果+define+进行了对A的定义,代码内部又进行了对A的定义,情况会如何呢?

首先是不加+define+的情况,A的打印结果是100(用的是`ifndef,命令行没有定义A的话就进入这一条语句);然后试试+define+A,打印出错,miss or empty argument;再试试+define+A=300,打印结果是300。

这个结果说明,通过+define+定义的参数优先级最高,会覆盖代码内部的同名定义。

原文链接:https://blog.csdn.net/Kizuna_AI/article/details/130103029

覆盖率收集

vcs 覆盖率收集2——覆盖率选项 + 合并覆盖率

http://t.csdn.cn/VWyAK

-parallel:并行merge

VCS支持的多核仿真有两种方式:ALP DLP

EX.ALP

-parallel+vpd+tgl+assert

EX.DLP

-parallel+autopart=[core_numbers]

-parallel+design=part.cfg