电流偏置、电压偏置

电压偏置:

1、对走线电阻引起的IR压降敏感

2、对噪声干扰敏感

3、器件相隔较远,匹配较差

电流偏置:

1、对走线电阻引起的IR压降不敏感

2、抗干扰能力强

3、需要匹配的器件可以放在一起,匹配更好。

模拟IC设计中,电流偏置的应用场景远远多于电压偏置。

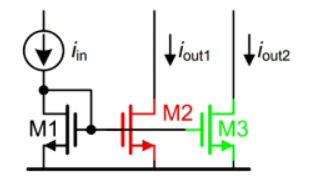

基本电流镜

两个MOS都必须工作在饱和区

电流镜设计中需要考虑的因素

1、电流镜像精度(系统失配、随机失配)

2、输出阻抗

3、输出电压范围

4、噪声

系统失配

系统失配(温度梯度、湿度梯度、应力梯度)

设计准则(unit cell based、版图共中心,dummy)

随机失配

饱和区电流公式

对电流失调有影响的三个因子:K、Vt、W/L

归一化

平方差

折中

过驱动电压很大,K和W/L决定失配

过驱动电压很小,Vt决定失配

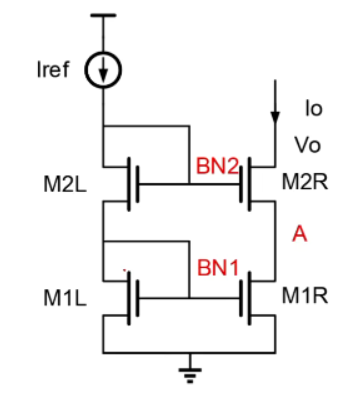

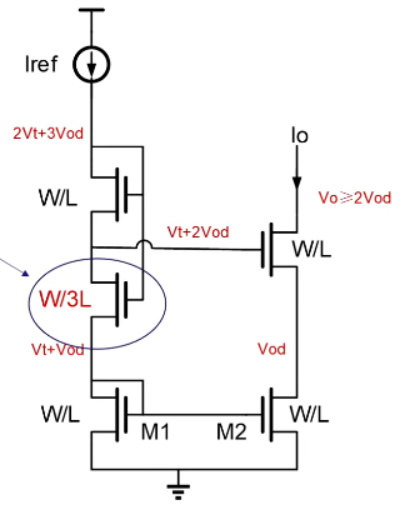

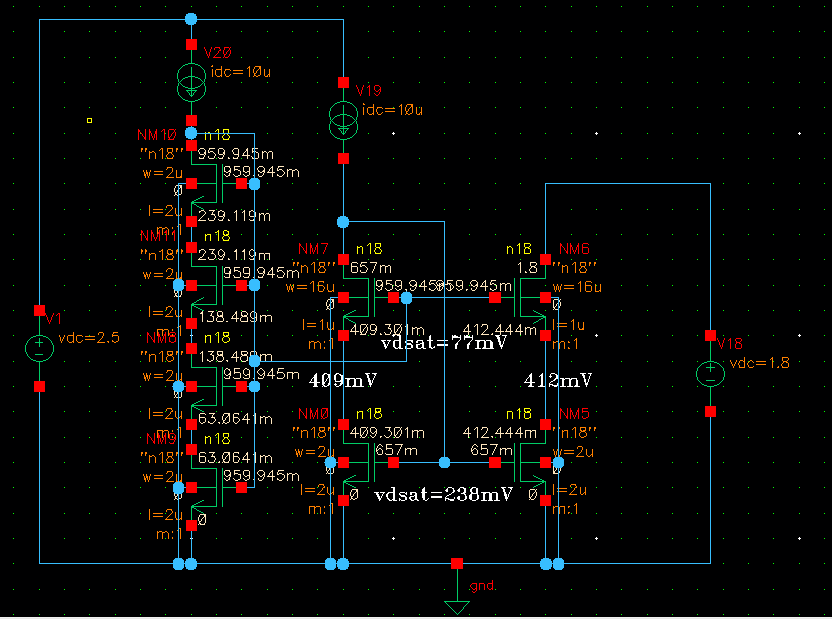

基本Cascode偏置

DC分析:

VBN1=vgs=vod+vth

VBN2=2vgs=2vod+2vth

Vo_min=VA+vod=2vod+vth

不适用于低压设计

AC分析:

Rout=gm2ro2ro1+ro2+ro1

优缺点:

优点:输出阻抗高

缺点:输出摆幅受限

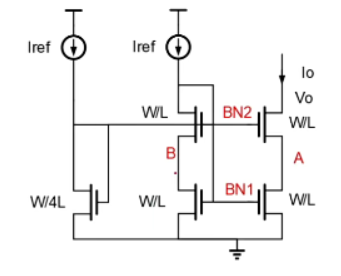

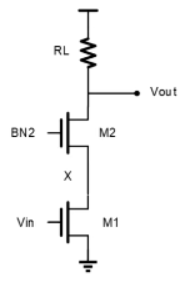

2支路偏置

DC偏置:

VA=VB=vod

BN1=vth+vod

BN2=vth+2vod

vo_min=2vod

多一条支路,功耗会增加

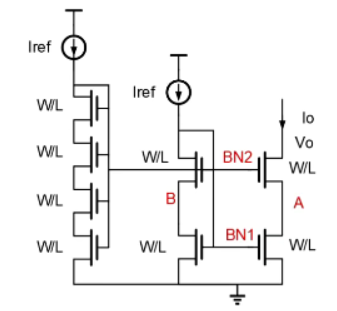

单支路偏置

W/3L管子vds=vod,vgs=vt+2vod,处于线性区,相当于一个电阻。

M1和M2漏极电压不相等,故存在系统失配。

共源共栅噪声

M1管噪声为主要噪声贡献,M2管噪声可忽略。

电流偏置的设计

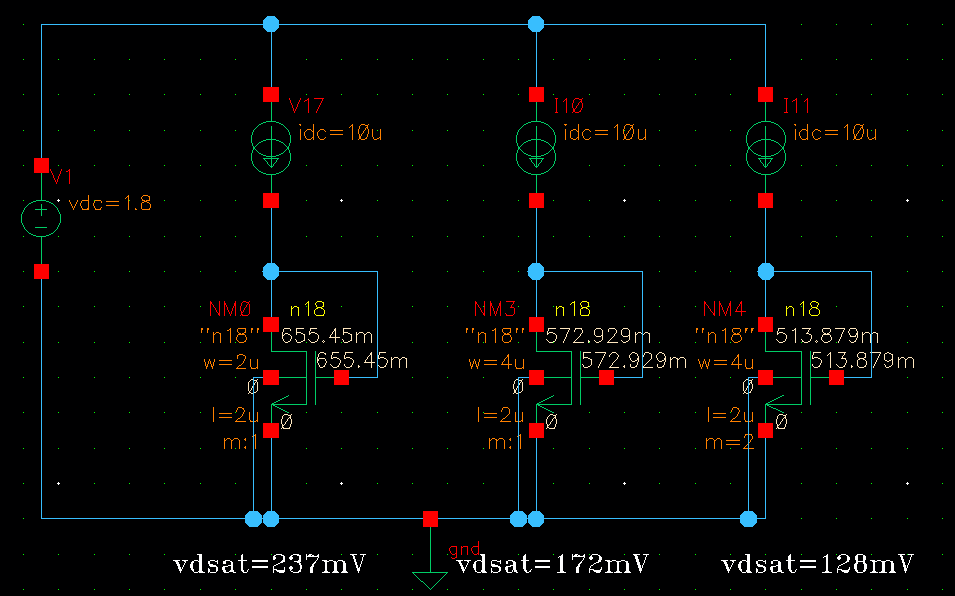

第一步:确定current source尺寸

在W/L为1:1,2:1和4:1的情况下查看vdsat的变化,可以看出W/L增加4倍的时候,vdsat大致减半。

从随机失配的角度,vdsat越大越好

从噪声角度,vdsat越大越好

但是vdsat越大,意味着电压裕度变小。取2u/2u。

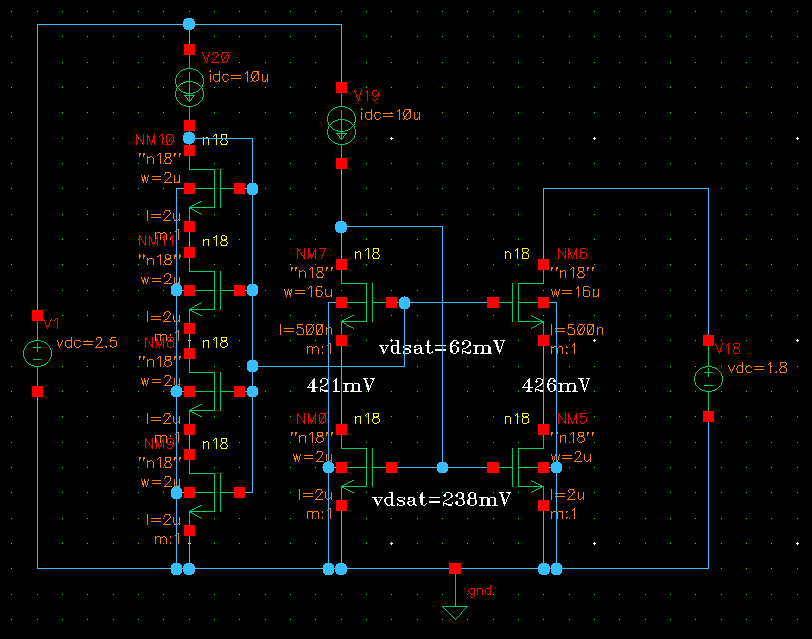

第二步:确定Cascode尺寸

Cascode管几乎不贡献噪声和失配,只需考虑输出阻抗。

Rout=gm2ro2ro1,输出阻抗和M2管本征增益成正比

gm2ro2正比于,需要WL乘积大。

需要gm2大,即vdsat2小,需要W/L大。

因此需要大的W和小的L,取W/L=16u/0.5

仿真结果,Cascode管vdsat=62mV,管子工作在亚阈值区

可以适当增加W/L,使管子工作在饱和区,Cascode管不贡献失配和噪声,因此要使电压裕度的消耗最小,可以将cascode管的vdsat控制在100mV以内,留出更多的电压裕度给current source MOS管。

![windows下Ubuntu保姆级安装教程 [附VMware资源]](https://img-blog.csdnimg.cn/45d82d890f154f76b51780f8d6524666.png)