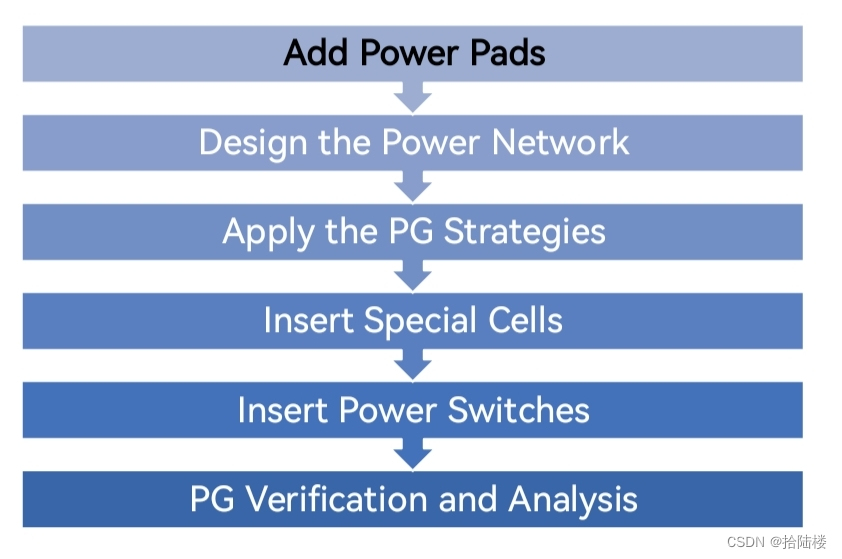

在shape block之后,接下来可以做pg规划。power network creation可以分为如下几个部分:

1.Add Power Pad

在规划power mesh之前需要先插power pad,所以要在create abstract阶段load upf,如果规划power mesh时没有power pad,也需要设置虚拟的power pad,power pad的place与signal IO一样使用place_io命令。

1.1 Setting Power I/O Constraints

插入power io可以使用插signal io的方法,也可以使用插power io独立的命令set_power_io_constraints+place_io

1) set_power_io_constraints+place_io

set_power_io_constraints \

-io_guide_object <io guide>

-reference_cell <io library cell name>

-ratio <连续power io之间最多signal io的数量> ;#只看signal io,不算power io

-offset <io guide起点与最近的power io的最大距离>

-spacing <power io之间最大距离>

-share <一个bump能接最大数量的power io>

举例如下:

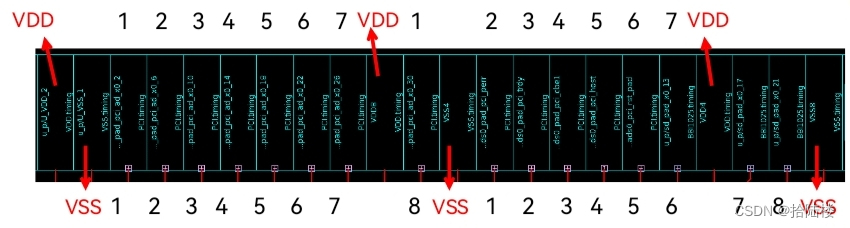

set_power_io_constraints -io_guide_object [get_io_guides "*bottom *top"] { {reference: VDD_NS} {ratio: 7} }

set_power_io_constraints -io_guide_object [get_io_guides "*bottom *top"] { {reference: VSS_NS} {ratio: 8} }

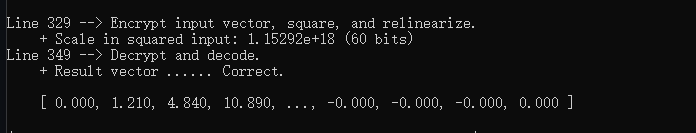

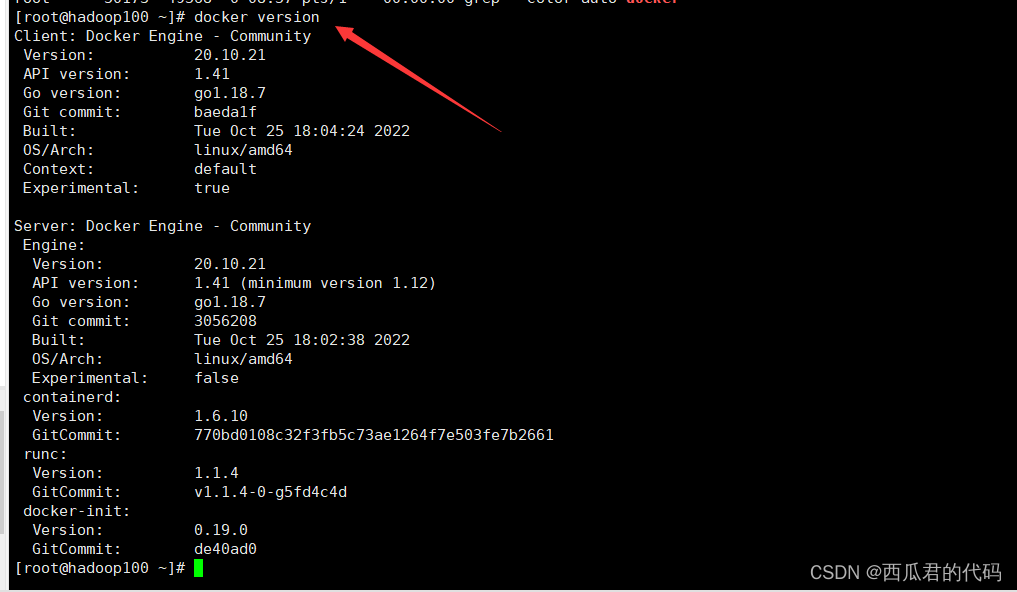

如上图,VDD_NS radio为7两个power io之间放了七个signal io,而VSS_NS ratio为8,对应两个ground io之间有8个signal io。

2) set_signal_io_constraints+place_io

用户可以手动设置power io与signal io的相对位置和数量。举例如下:

create_cell pg_vddh_left1 [get_lib_cells */VDD_EW]

create_cell pg_vddh_left2 [get_lib_cells */VDD_EW] ... set_signal_io_constraints –file all_pads.io

## all_pads.io

...

pad_iopad_13

} {{40}

pg_vss_left_1

pg_vddh_left_1

}

{{order_only}

pad_iopad_14

...

1.2 Insert Physical Only I/O Cells

在power io和signal io都放置好了,可以放physical only的I/O cell了,包括如下三种:

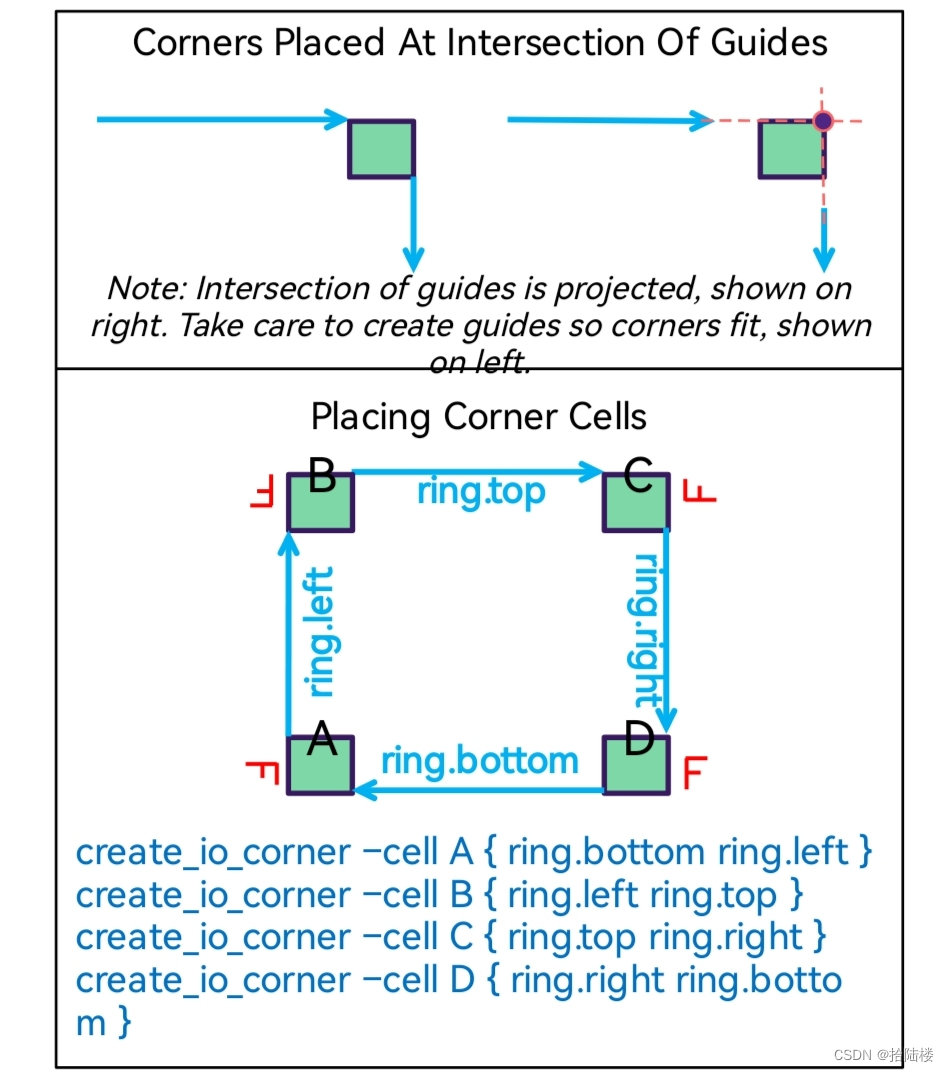

1) create_io_corner_cell

在两个io guide之间插corner cell,一般在芯片的四个角,corner cell的方向跟着第一个io guide走。

添加方式有两种,一种指定inst name一种指定ref cell name,前者需要网表里有corner cell。

create_io_corner_cell \

-cell <inst> \

{ <io_guide1 io_guide2> }

create_io_corner_cell \

-reference_cell <lib_cell> \

{ <io_guide1 io_guide2> }

举例如下:

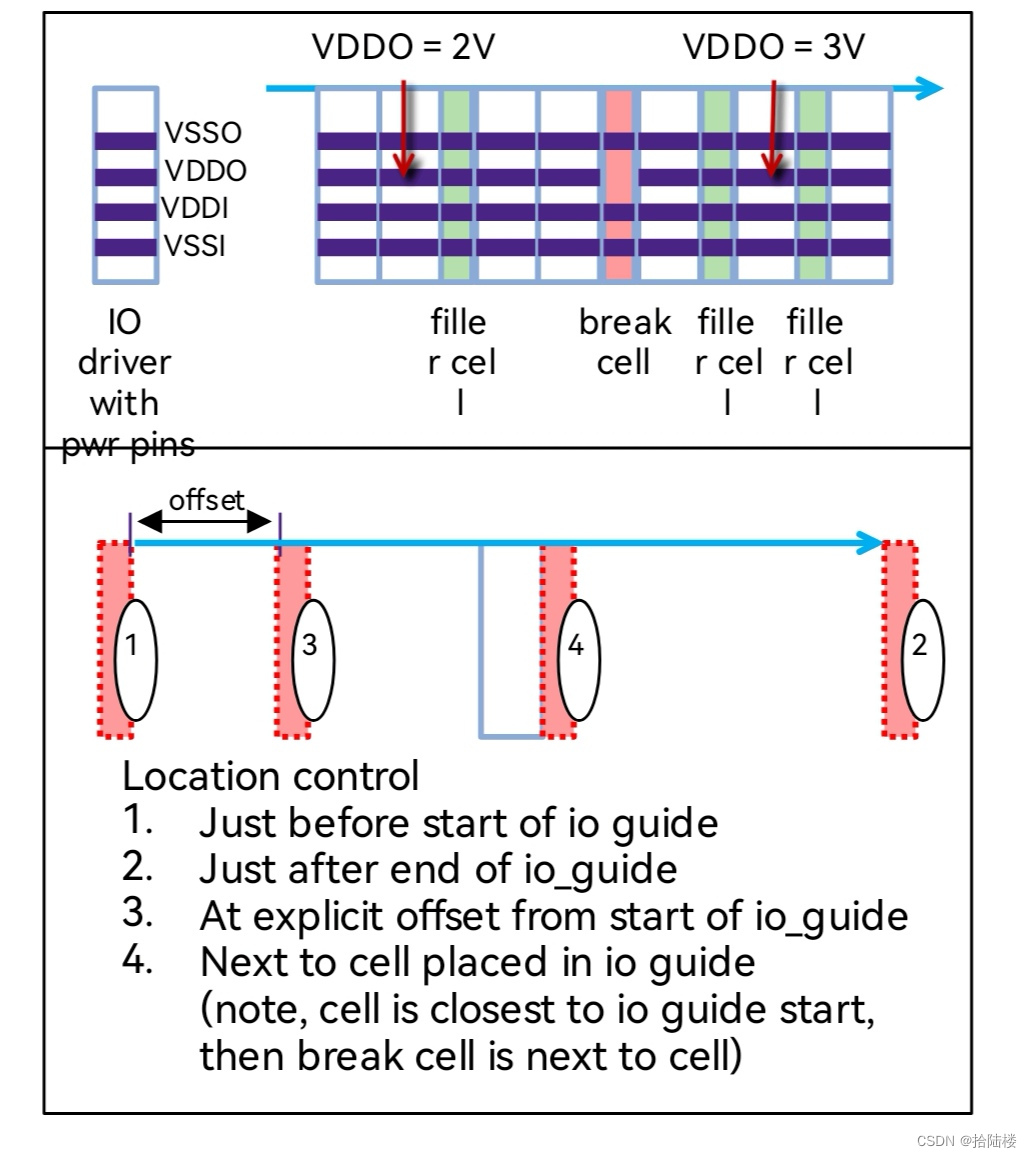

2) create_io_break_cells

把电压不同的io ring切断开。

create_io_break_cells

[-reference_cells lib_cell_name_list]

[-cells cell_name_list]

[-location start | end | both | offset | cell]

io_guide_list

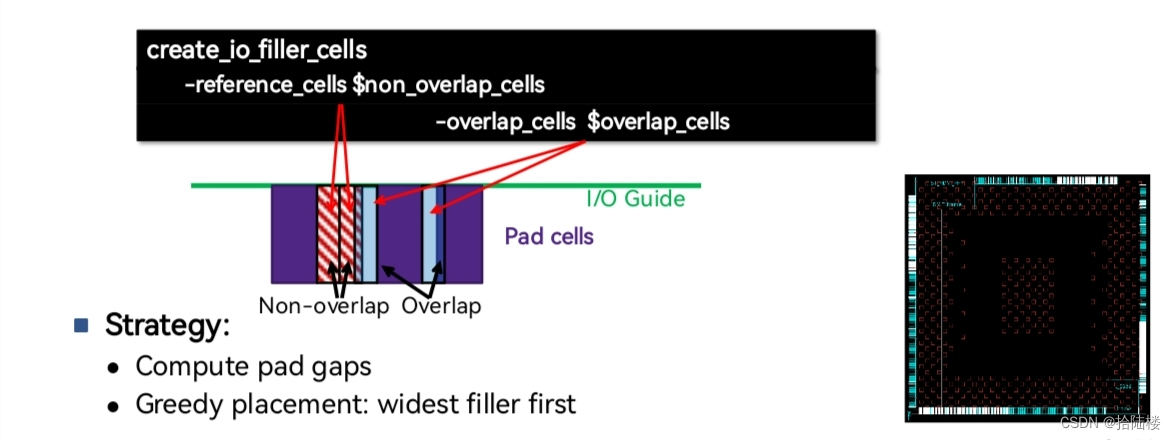

3) Add I/O Filler Cell

填补IO之间的空隙。

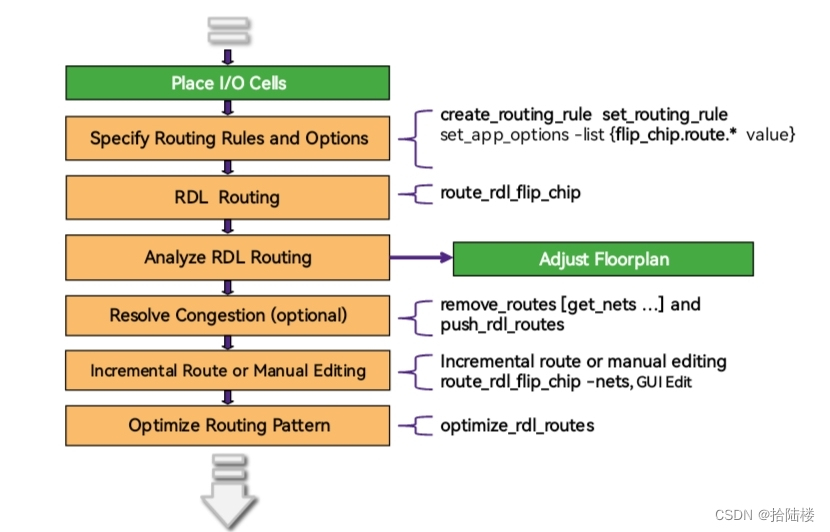

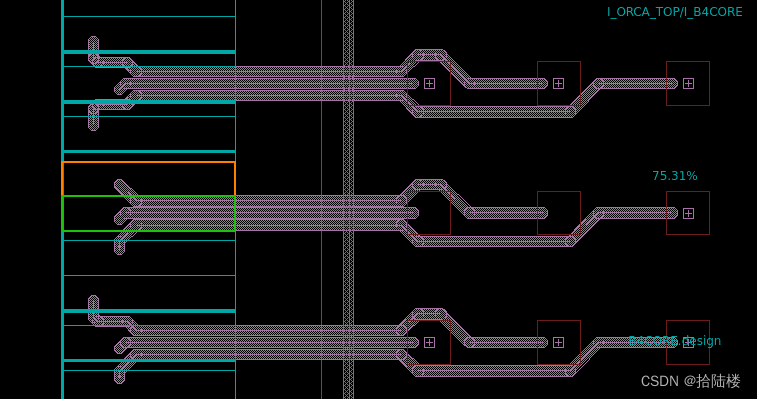

1.3 Route Flip Chip Nets

RDL 绕线用来连接IO和bump。

1) Set routing rule for the RDL nets

create_routing_rule RDL -widths {MRDL 12}

set_routing_rule -rule RDL \

[get_nets -of_objects [get_pins -of_objects \

[get_cells -filter "ref_name == BUMP"]]]

2) Route the RDL nets

route_rdl_flip_chip -layers {MRDL} \ [-nets <nets> | -nets_in_file <nets_file>]

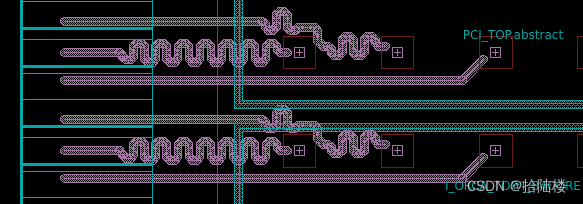

3) optional,remove or reduce the amount of U and Z routing shape。

optimize_rdl_routes -layer RDL -reserve_power_resources true

4) optional,route a collection of nets and match their length

route_rdl_differential -layer RDL -nets [get_nets "A B C"]

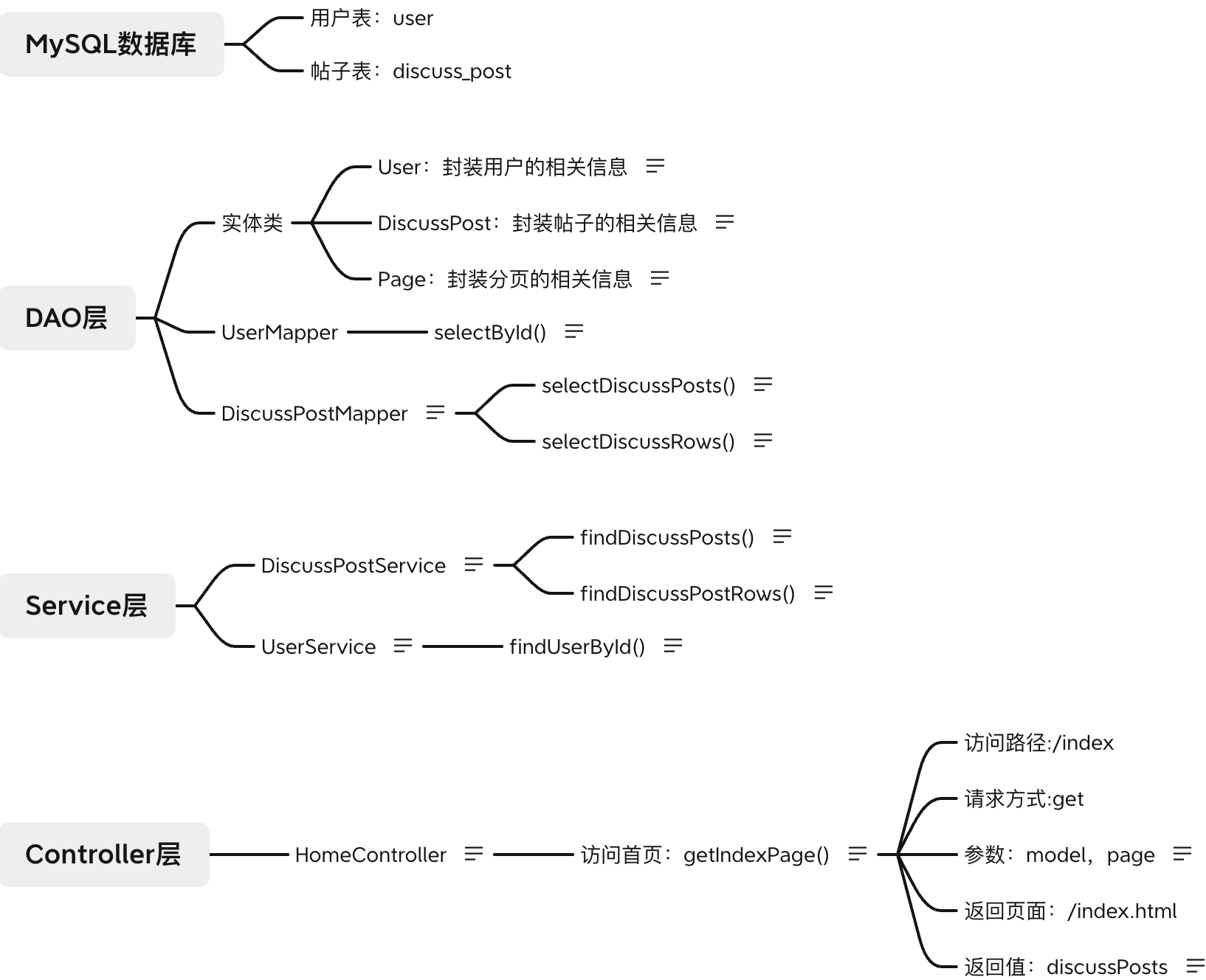

2.Design the Power Network

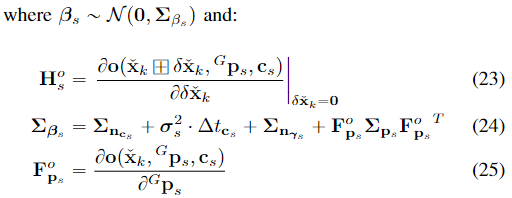

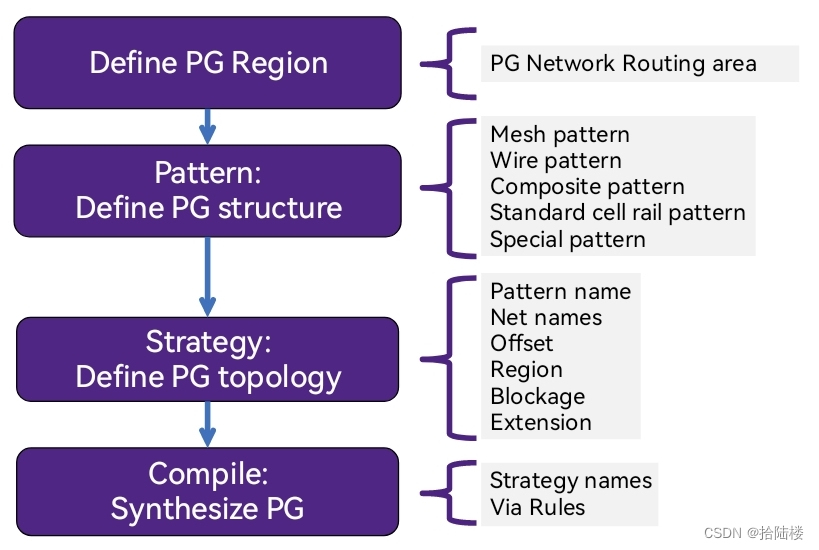

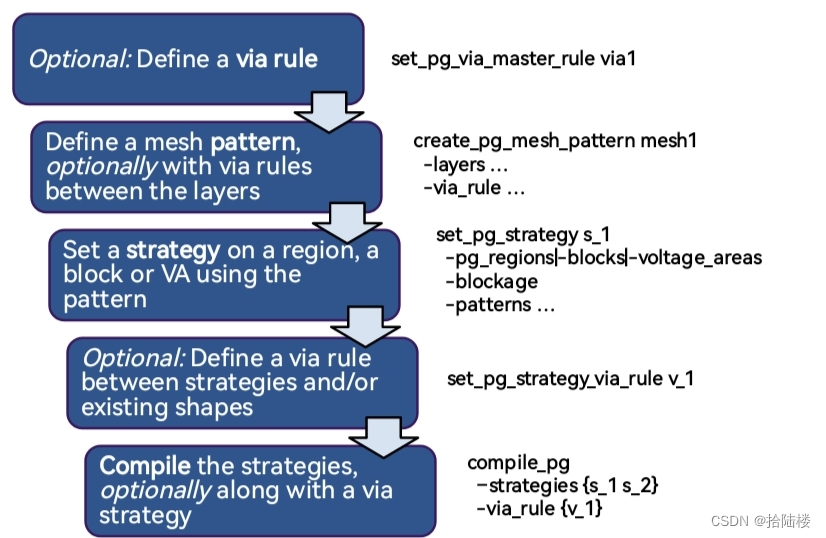

Pattern Based Power Network Synthesis(PPNS) 流程如下:

2.1 PG Regions

pg region可以依托于core area,block,voltage area,macro/groups of macros ,groups of regions ,polygon创建。

示例:

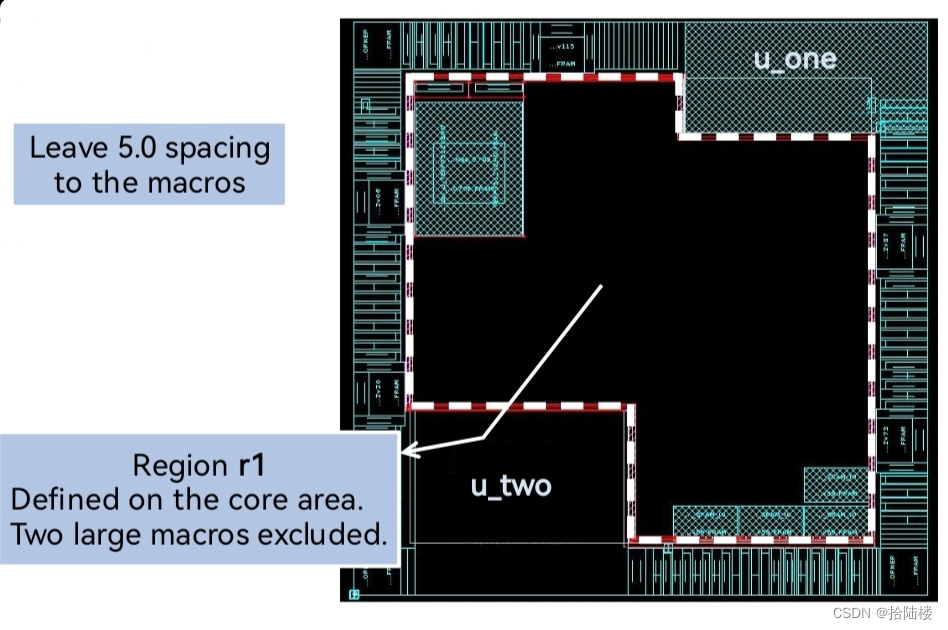

create_pg_region r1 -core -exclude_macros {u_one u_two } -macro_offset 5.0 ;#依托于core area创建pg region,但是要排除两个macro,并与macro之间留有5.0um的间距。

2.2 PG Ring

定义pg ring需要指定水平和纵向layer,以及间距,宽度和via rule等条件,也可以针对每条边单独设置宽度和间距。

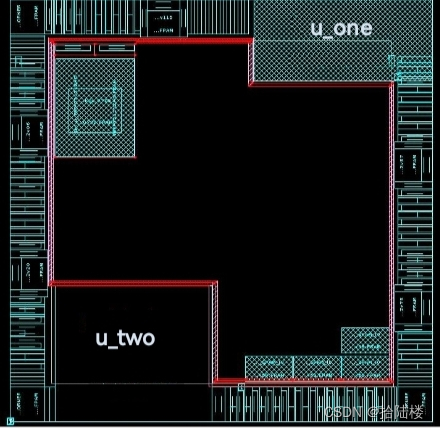

承接上面的例子:

create_pg_region r1 -core -exclude_macros {u_one u_two } -macro_offset 5.0

create_pg_ring_pattern ring1 -horizontal_layer M5 -vertical_layer M4 -horizontal_width 2.0 -vertical_width 2.0

set_pg_strategy s1 -pg_regions {r1} -pattern { {name: ring1} {nets:{vdd vss}} }

compile_pg -strategies s1

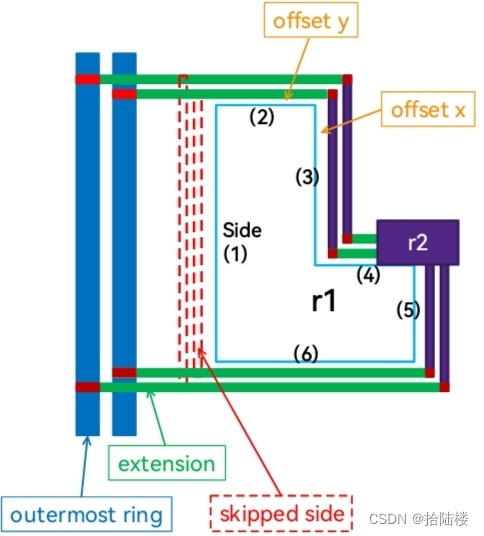

pattern还有blockage,parameters,extension的拓展用法,分别代表屏蔽,参数,延伸。用法可以看如下示例:

create_pg_ring_pattern ring1 -parameters {hw vw} -horizontal_layer M5 -vertical_layer M4 -horizontal_width {@hw} -vertical_width {@vw} :#@hw和@vw就是参数,需要在pg strategy中用parameters声明。

set_pg_strategy s2 -pg_regions {r1} -blockage {voltage_areas: r2} -pattern { {name: ring1} {nets: {vdd vss}} {parameters:{3 2}} {offset: {4 2}} {skip_sides: 1} } -extension { {side: 2 6} {direction: L} {stop: outermost_ring} } ;#blockage意味着屏蔽voltage area r2,extension意思是延伸,side指定边都是最左边为1号边。

2.3 PG Mesh

pg mesh pattern使用流程如下:

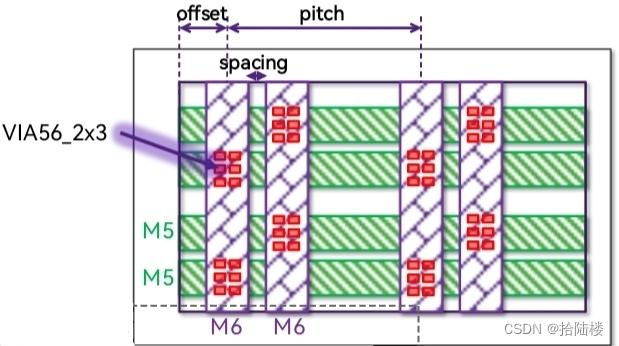

create_pg_mesh_pattern mesh1 \

-layers { { {horizontal_layer: M5} {width: 6} {spacing: 1} {pitch: 12} {offset: 5} } { {vertical_layer: M6} {width: 6} {spacing: 2} {pitch: 20} {offset: 6} } } \

-via_rule { { {layers: M5} {layers: M6} {via_master: VIA56_2x3} } }

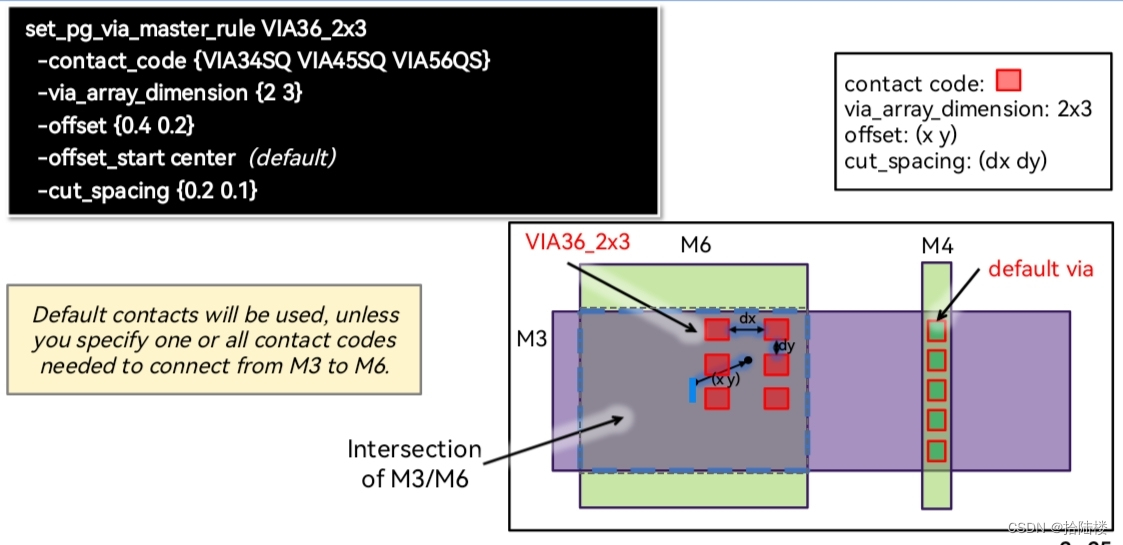

2.4 Define Custom PG Vias

set_pg_via_master_rule VIA36_2x3 -contact_code {VIA34SQ VIA45SQ VIA56QS} -via_array_dimension {2 3} -offset {0.4 0.2} -offset_start center (default) -cut_spacing {0.2 0.1}

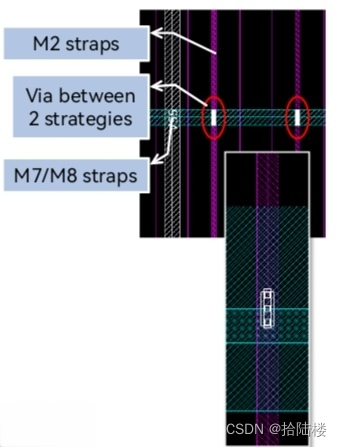

2.5 Define Via Rule between Objects

设置via rule规则用来连接不同的strategy的strap或者strategy与存在的shape。

set_pg_strategy_via_rule S_via_m2_m7 -via_rule { { { {strategies: {S_m2}} {layers: { M2 }} } { {strategies: {S_m7m8}} {layers: { M7 }} } {via_master: {pgvia_1x3}} } } ;#让两个strategy的M2和M7之间打孔,如果不想让二者打孔via master可以写“NIL”。

如果没有用set_pg_strategy_via_rule或者compile_pg没用-via_rule选项的情况下,via会插在所有相同pg net的不同层相交shape上。

如果只想用一个via rule strategy可以使用compile_pg -via_rule rule_name选项。

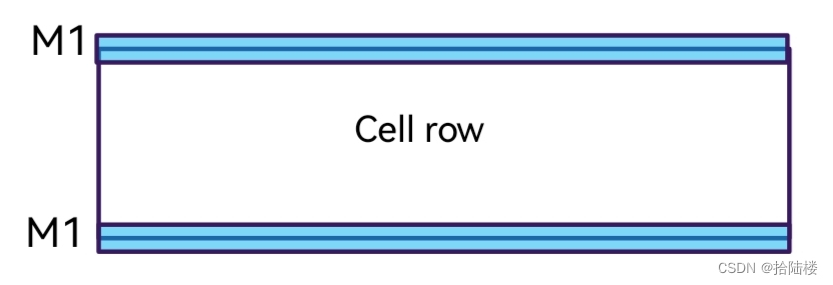

2.6 Standard Cell Connection Pattern

create_pg_std_cell_conn_pattern std_pat1 -layers {M1}

set_pg_strategy S_std_cells -core -pattern { {{name: std_pat1} {nets: {VDD VSS}} } -extension {{stop: innermost_ring}}

compile_pg –strategies S_std_cells

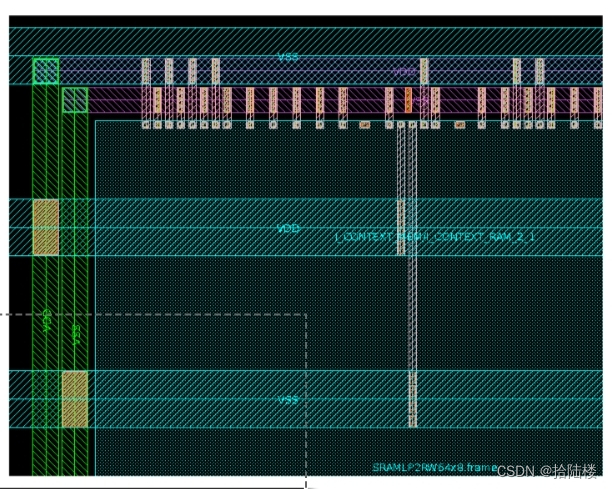

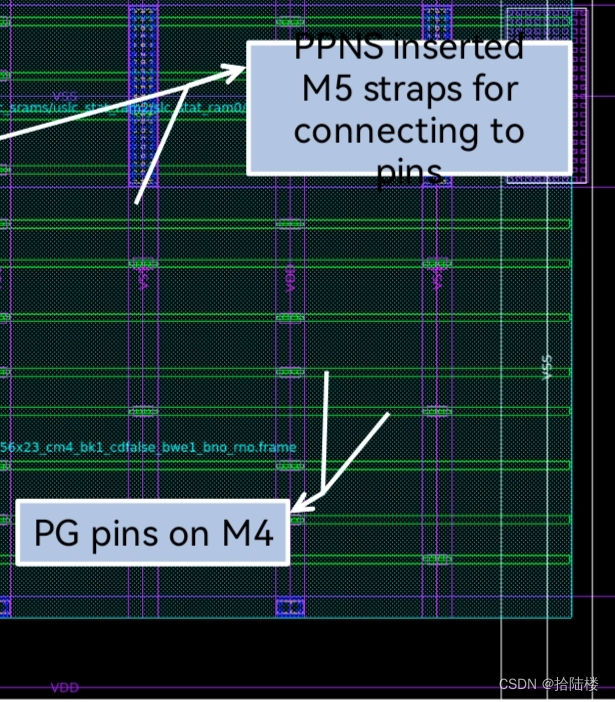

2.7 Macro Connections

连接macro pin的pg mesh方案。

create_pg_macro_conn_pattern

通过-pin_conn_type控制三种模式

1) scattered_pin

延伸不规则的pg pin到外部的pg mesh。

create_pg_macro_conn_pattern P_HM_pins \

-pin_conn_type scattered_pin -layers {M4 M5}

set_pg_strategy S_HM_pins -macros $hardmacros \

-pattern { {pattern: P_HM_pin} {nets: {VSS VDD}}}

compile_pg -strategies {S_HM_ring S_HM_pins}

2) long_pin

pg pin是长条形的,pg mesh与pg pin相交。

create_pg_macro_conn_pattern macro_long_pins \

-pin_conn_type long_pin \

-direction vertical \

-spacing interleaving \

-pitch $M5_pitch \

-width $M5_width \

-layers M5

set macros [get_cells -hier -filter "is_hard_macro"]

set_pg_strategy S_macros -macros $macros \

-pattern { {name: macro_long_pins} {nets: VDD VSS} }

3) ring_pin

macro内部的环形pin,指型连接到strap或macro ring。

3.Apply the PG Strategies

1) 测试阶段ignore drc

compile_pg -strategies s1 -ignore_drc

2) 检查mesh,移除mesh

compile_pg -undo

3) 最后调整好strategies

compile_pg -strategies s1

compile_pg -strategies {s1 s2} -via_rule v1

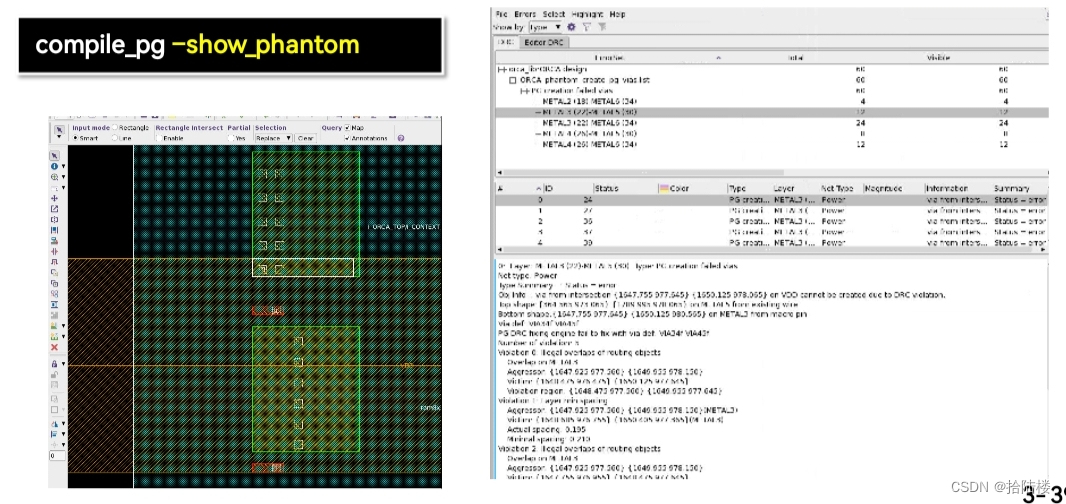

3.1 Report of Missing Vias Due to DRC

因为drc问题没有插入via的情况可以使用compile_pg报告

compile_pg -show_phantom

3.2 Specify Block-Level Power Nets

PNS创建的pg net部门直接应用于top level,例如要给block指定pg strategies需要给出他完整的hierarchy名字。

set_pg_strategy s_top \

–blocks I_TOP/I_SWITCHED \

-pattern {{name: sw_strap} {nets: {I_TOP/I_SWITCHED/VDD_SW}} }

如果不指定-block,那么I_TOP/I_SWITCHED/VDD_SW在top就会是一条dummy net。要避免这个问题就需要pg characterize。

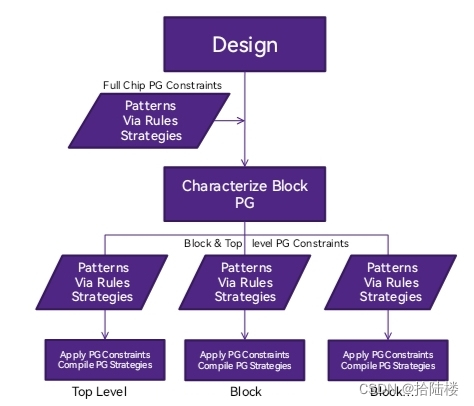

3.3 Characterize Block PG Flow

1) Design input

定义full chip的pg 约束。

2) Characterize Block PG

characterize_block_pg: 提取top level和每个block的pg约束。

3) Create PG for each block and top level

应用pg 约束compile pg。

4.Insert Special Cells

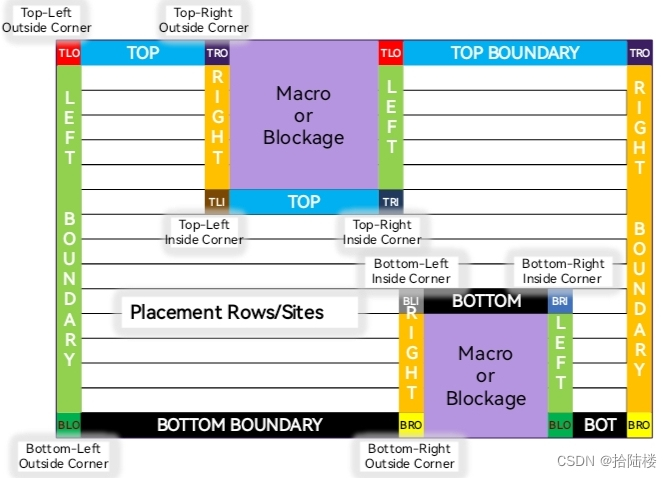

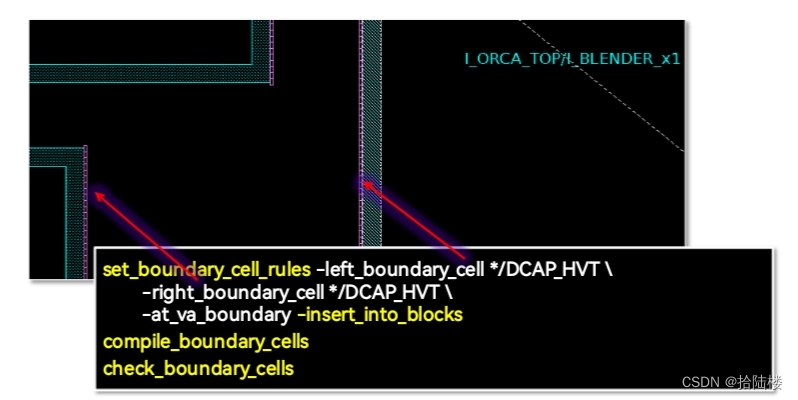

4.1 Boundary Cell

给boundary/macro/blockage/voltage area的内角或外角加boundary cell。

举例如下,给block加boundary Cell。默认只给top level加。

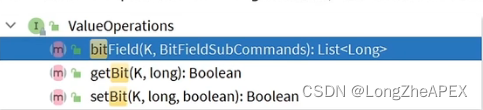

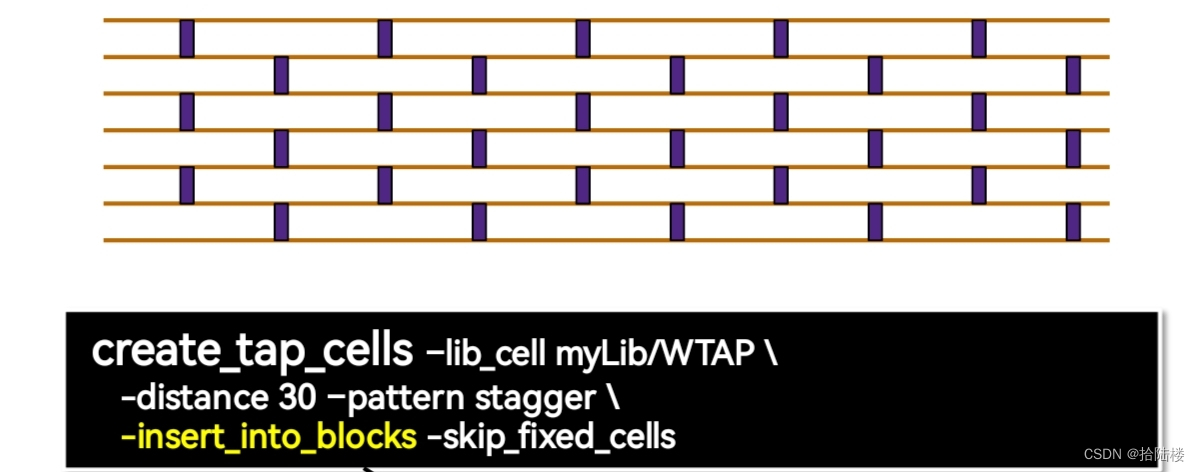

4.2 Tap Cell

给block level和top level加tap cell。

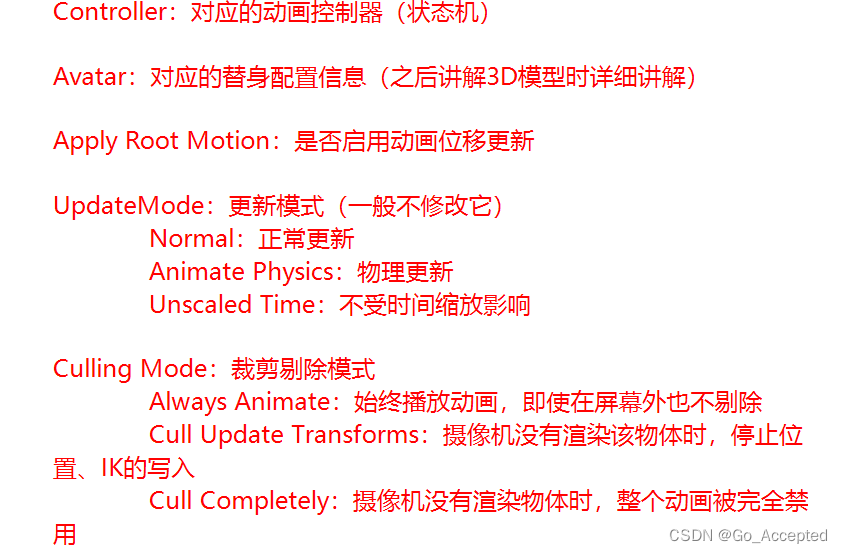

其中stagger如上图所示是交错的形式,一般应用的也是这种形式,能减少tap cell数量。

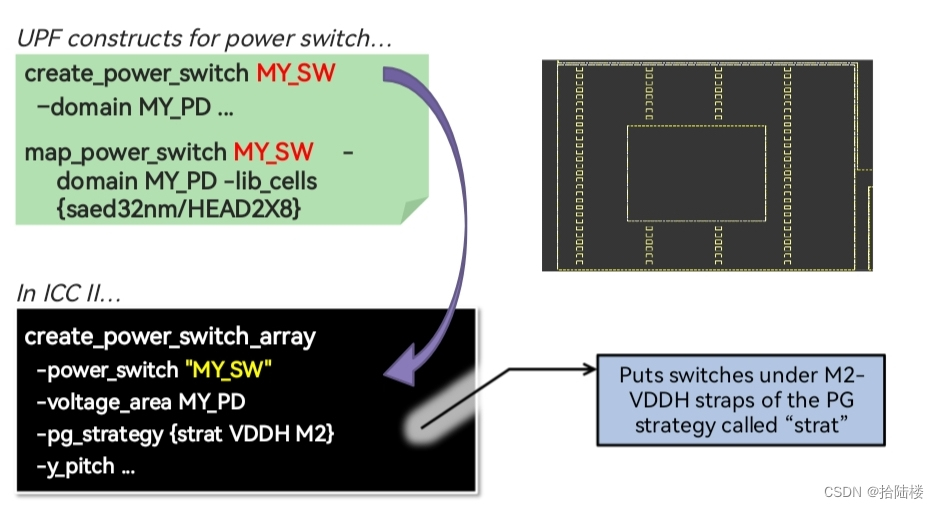

5.Insert Power Switch

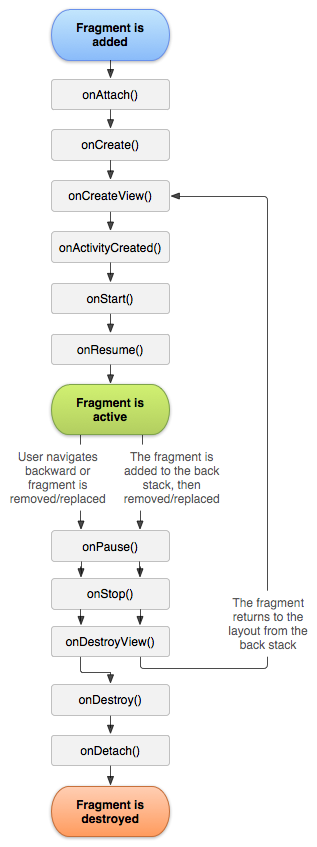

关断power domain/block可以起到节省漏电的作用,power switch加在main supply和可关断的switched supply之间,swtitched supply连接standard cell的power rail。

按照切断power/ground来分的话,可以分为切断power的Header类型和切断ground的Footer类型,前者使用pmos晶体管同等大小漏电更低,然后使用nmos晶体管的后者往往ir drop和面积都要更小。

使用示例如下:

摆放方式上,switch cell多摆放在main supply的strap下面方便打孔连接。

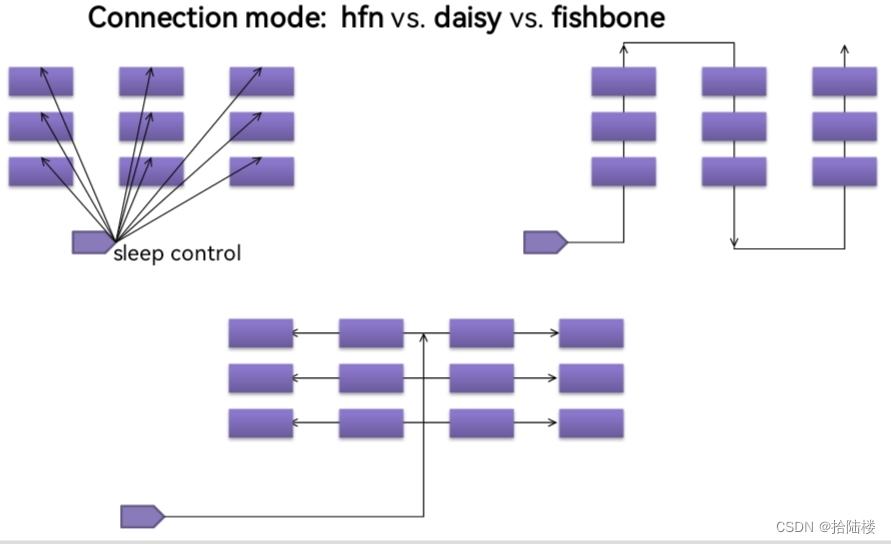

sleep信号连接方式上多采用菊花(daisy)链的方式,除此之外还有hfn和fishbone两种形式。

示例如下:

connect_power_switch -mode fishbone \

-direction horizontal -start_point lower_left

6.PG Verification and Analysis

1) check_pg_drc

检查违反technology design rule的drc问题。

2) check_pg_missing_vias

检查pg 网络缺失via的问题。

3) check_pg_connectivity

检查pg pin/shape/via的连接情况(floating)