第一节课 linux命令

文件命令

man 查询指令的作用 如 man cd

ls 列出当前文件和文件夹的名字(list the directory and files)

ls -a 把隐藏的文件和文件夹也显示出来 (list all)

ls -l 把文件的属性(读写),所有者,创建时间等列出来

ll -a 把隐藏的也列出来

cd 进入目录,默认是user目录

pwd 显示目录路径

mkdir dir 创建一个文件夹 (make directory)

touch file 创建一个文件

vi file 编辑文件

gvim file 编辑一个文件

chmod 777 dir 改变文件的读/写/可执行语句 777是可读可写可执行

cat file 查看文本内容

cat > file 写文本到file

more file 查看文本内容

less file 查看文本内容用gvim 或vim看

cp file1 file2 拷贝file1 to file2

cp -r dir1 dir2 拷贝dir1 to dir2 ,包含文件夹里的文件,即递归拷贝

mv file1 dir 移动文件到文件夹下

mv file1 file2 对文件1重命名

wc file 统计文本里面行 单词,字符的统计 (word count)

wc -w file 只统计单词个数

wc -l file 只统计行数

删除文件

rm file 删除文件

rm -r dir 删除文件夹(递归删除)

rm -f file 强制删除文件(force)

rm -rf dir 强制递归删除文件夹

ln -s file line 创建文件的软链接 (快捷方式)

查找文本

grep pattern file 在文件中搜查文本pattren

如 grep error sim.log

grep error cmp.log > error.log 在cmp.log中将有error的行存到error.log中

grep string cmp.log >> error.log 在cmp.log中将有string的行追加到error.log中

grep -r pattern dir 递归的方式去查文件夹

find / -name file_name 从/目录下查找文件

fine / -size +100M 找大于100M的文件

打包和解压

tar -cvf file.tar files / dir 把文件或文件夹下面的文件打包成.tar c是创建

tar -xvf file.tar 解压文件 extract x是解压

tar -czvf file.tar.gz files 创建一个gzip file

tar -cjvf file.tar.bz2 files 创建一个gzip 文件

gzip file 打包一个 file.gz 文件

gzip -d file.gz 解压一个fie.gz 文件

rpm -qa 查询已经安装的所有rpm包 query all installed rpm packages

rpm -ivh rpm.rpm 安装rpm 包

安装一些源文件时

./configure

make

make install

| 管道命令

前面的输出是后面的输入

如 rpm -qa | grep vim 查找安装包中有vim的安装包

进程

process manage

ps 显示当先活动的进程 process show

top 显示操作系统所有的进程

kill pid 停止pid 号对应的进程

killall proc 停止所有的proc的进程

bg 列出后台运行的工具和命令 job background

fg 把后台的job放到前台 foreground

系统信息

date 查看系统时间

date +%Y%m%d 用20230426 显示时间

cal 显示当前月日历

uptime 当前运行时间长度

whoami 当前用户

uname -a 显示系统信息

which cmd 显示cmd路径

su root 切换用户

echo $PATH 显示变量

history 显示历史命令

df 显示系统硬盘容量

du -b/k/m file/dir 显示文件多大

du -s file|dir 总的信息 summary

ping host/IP

hostname 显示本机地址

ifconfig -a 显示本机网络信息

第二节课 数字ASIC设计流程介绍

数字IC设计流程

1、确定项目需求 制定芯片的具体指标 封装

物理指标 制作工艺•裸片面积

性能指标 • 速度 功耗

功能指标 功能描述 接口定义

2、系统级设计 用系统建模语言对各个模块描述

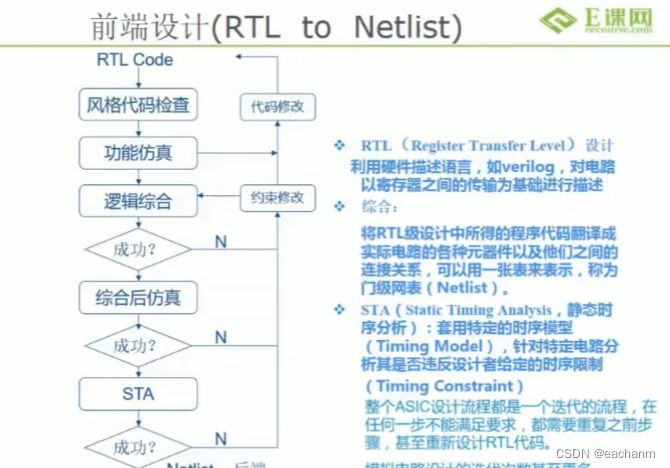

算法模型 -------> RTL设计 (综合工具根远基本单元库的功能时序模型,将行为级代码译成具体的电路实现结构)------------> 网表生成 (布局布线工具根据基本单元库的时序几何模型将电路单元布局布线成为实际电路版图)-----------> layout

3、前端 RTL设计、RTL仿真、硬件原型验证、电路综合

形式(功能)验证 :从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查(Equivalence Check)方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能,常用工具synopsys, formality

时序验证:检查电路是否存在建立时间和保持时间上的违规

4、后端设计 版图设计、物理验证、后仿真等

PR 版图验证, PD版图设计