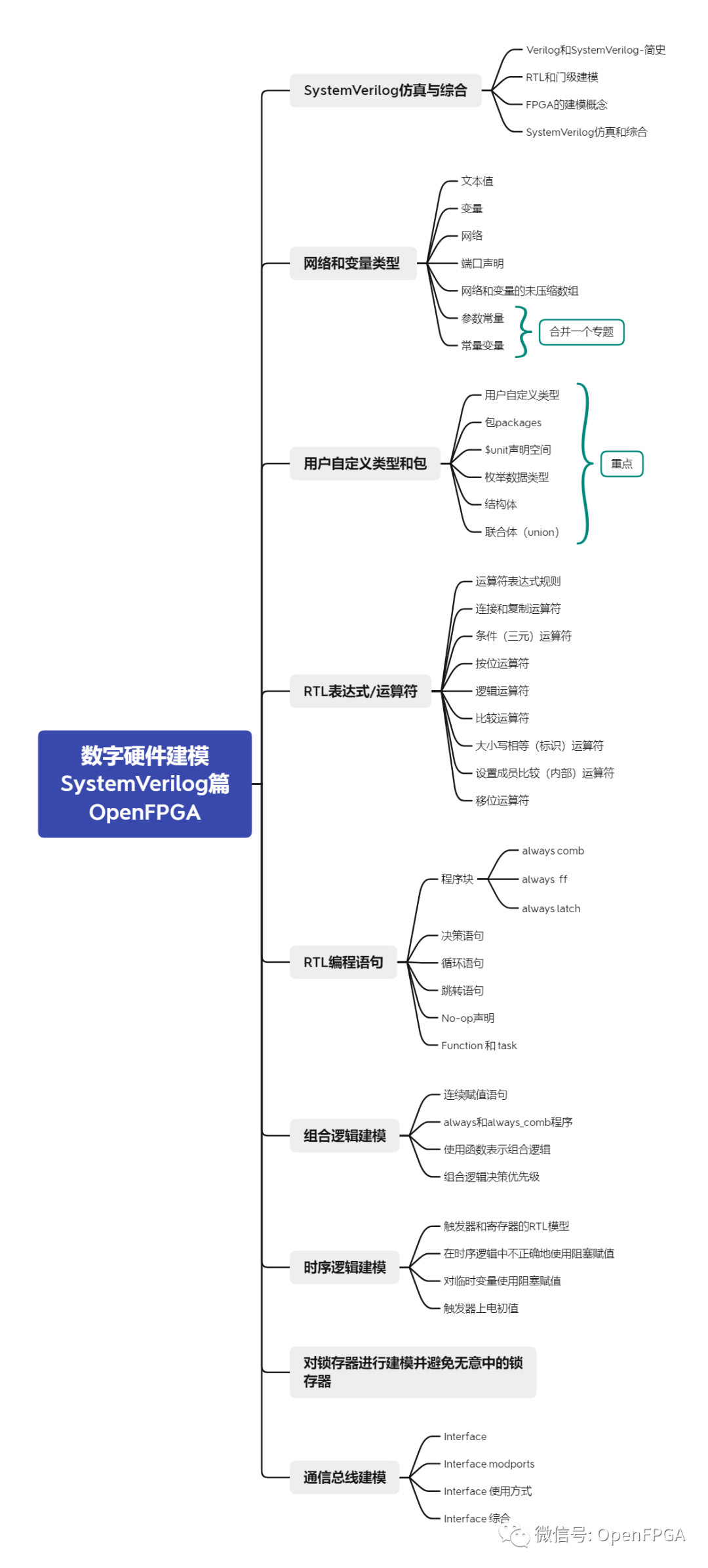

来到了SV最后一部分,预计三篇文章,两周更完,所有的思维导图如下:

概述

SystemVerilog Interface是modport的一种,但比简单的输入、输出或输入输出端口的功能更多。在其最简单的形式中,Interface端口将相关的信号捆绑在一起作为一个单一的复合端口。例如,构成AMBA AXI总线的所有单个信号都可以被归纳为一个Interface端口。一个Interface可以做的不仅仅是封装总线信号。SystemVerilog Interface为设计者提供了一种集中总线功能的方法,而不是将功能分散在设计中的几个模块中。这就模拟了设计工程师在RTL层面的工作,并让综合工作在整个设计中适当地分配门级总线硬件。

当遵循特定的建模准则和限制时,Interface是可以综合的。Interface也可以用在不可综合级别的建模,并作为验证测试平台的一部分。先进的验证方法,如UVM 、OVM和VMM,都使用Interface。

使用Interface作为modport

interface:定义interface模块以关键字interface和endinterface结尾,内部通过定义输入输出信号和对应的logic信号,注意,双态信号不可以定义为logic。定义好了interface后,需要在top层将interface进行例化。

modport:使用modport来对上述信号接口进行一个分组和方向指定,这样会使得接口更加条理清晰。在顶层top中例化test时参数还是接口(模块内部是modport)

一个模块的端口可以被声明为一个Interface类型,而不是传统的输入、输出或inout端口。一个模块可以有任意数量的interface,interface可以与其他端口以任意顺序连接。本书中的例子将Interface端口列在前面,只是为了强调Interface端口的作用。

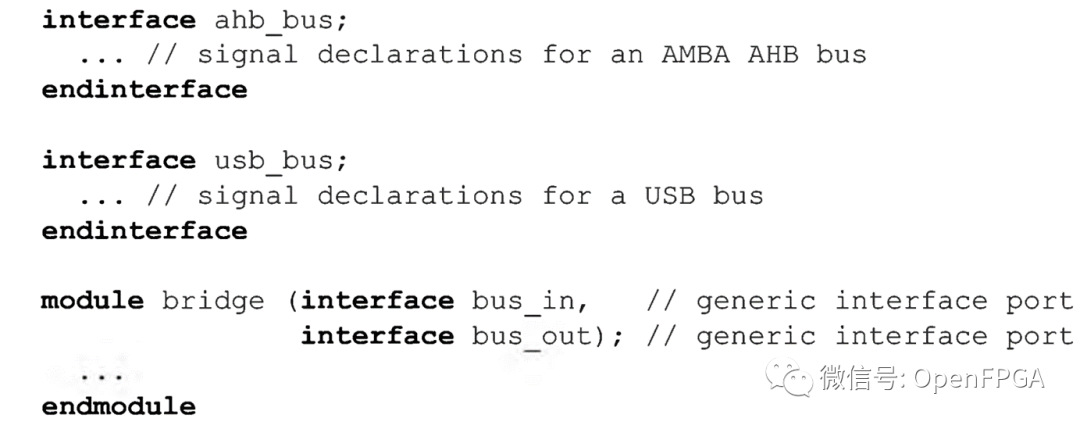

有两种风格的Interface端口声明--通用和特定类型。这两种风格都是可以综合的。

通用Interface端口

一个通用的Interface端口通过使用关键字interface来定义端口的类型。而不是使用一个特定的Interface类型的名称。语法是:

module <module name>(Interface<port_name>)当module被实例化时,任何类型的Interface都可以被连接到通用Interface端口。这就提供了灵活性,同一个模块可以用多种方式使用,不同的Interface连接到模块上。在下面的例子中,模块bridge被定义为有两个通用Interface端口。每个通用Interface端口可以有一个ahb_bus Interface实例或一个Interface端口。

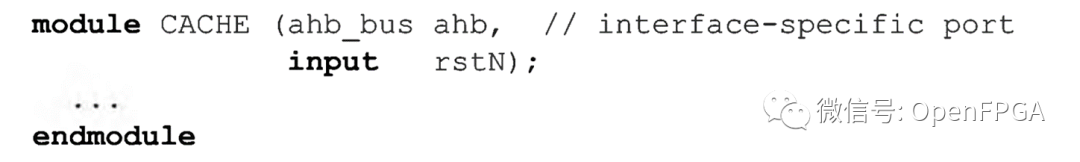

特定类型的Interface端口

一个modport可以被明确地声明为一个特定类型的Interface。一个特定类型的接口端口是通过使用一个Interface的名称作为端口类型来声明的。语法是:

module <module name> (<interface name><port_name>)。比如说:

一个特定类型的Interface端口只能连接到同一类型的Interface实例上。在上面的例子中,高层网表可以实例化CACHE模块并连接一个ahb_bus Interface的实例,但不能连接一个usb_bus Interface的实例。如果错误的Interface实例类型被连接到特定类型的Interface端口,仿真器或综合工具将发出一个阐述错误。特定类型的Interface端口确保错误的Interface不会被无意中连接到端口上。明确命名可以连接到端口的Interface类型,也使端口类型对其他需要审查或维护模块的人更加明显。有了特定类型的Interface端口,就更容易看清端口的确切使用方式。

| 最佳实践指南10-2 |

|---|

| 为RTL模型使用特定类型的Interface端口。不要在设计模块中使用通用的interface。 |

一个模块的功能需要引用Interface内的信号。对于特定类型的Interface,Interface内的信号名称在编写模块的时候就已经知道了,可以毫无顾虑地引用。对于通用Interface端口,不能保证连接到模块Interface端口的每个Interface实例都有相同的信号名称。

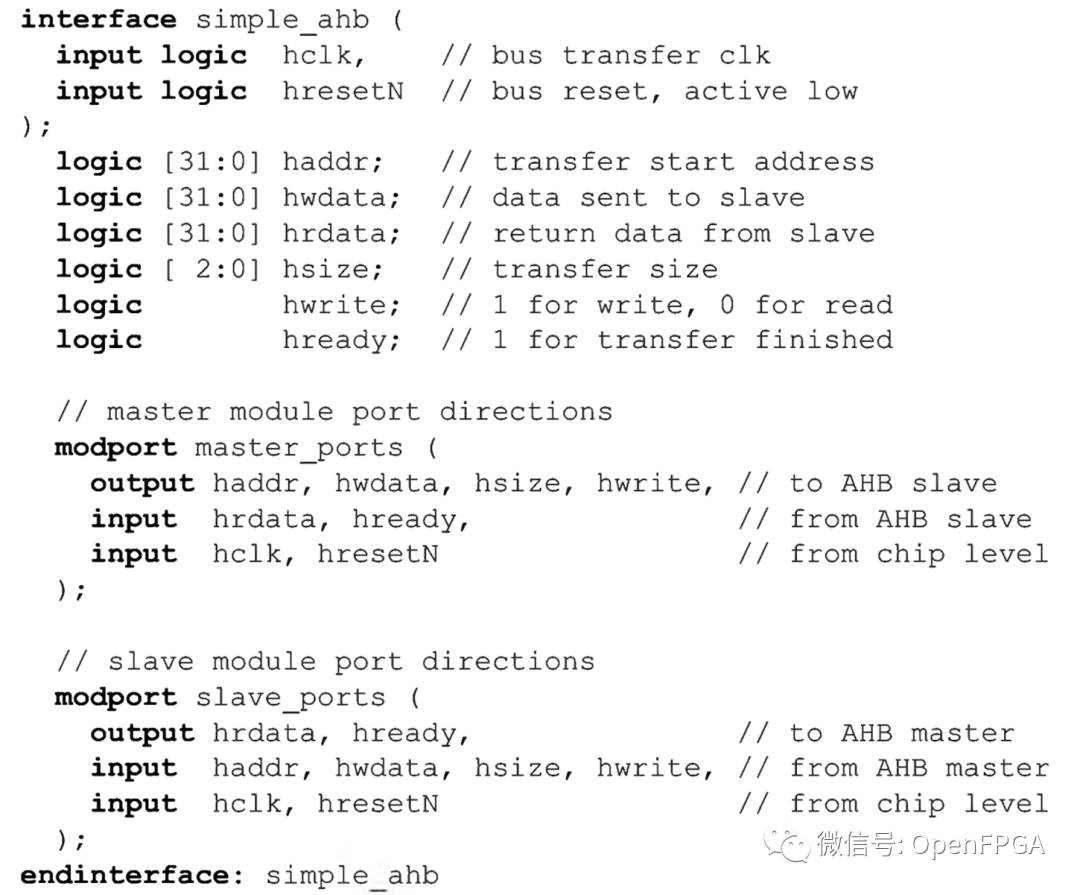

Interface modports

Interface为简化模块间的连接提供了一种实用而直接的方法。然而,连接到一个Interface的每个模块可能需要看到Interface内信号的独特视图。例如,在AHB总线上,hwdata信号是主模块的输出,而同样的hwdata是同一总线上从属模块的输入。

SystemVerilog Interface提供了一种方法来定义Interface信号的不同视图,这样每个模块都能看到具有正确端口方向的Interface端口。这个定义是在Interface中使用modport关键字进行的。Modport描述了Interface所代表的modport。一个Interface可以有任意数量的modport定义,每个定义都描述了一个或多个其他模块如何看待Interface内的信号。

一个modport定义了模块在Interface中看到的信号的端口方向。modport的定义并不重复已经在Interface信号声明中定义的向量大小和类型信息。一个modport只定义连接模块是否将一个信号视为输入、输出、inout端口。

下面的界面中显示了两个modport声明的例子。

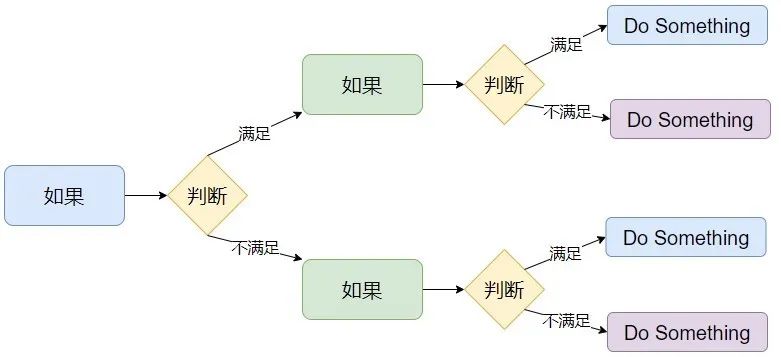

指定使用哪种modport

SystemVerilog提供了两种方法来指定一个模块Interface端口应该使用哪种modport。

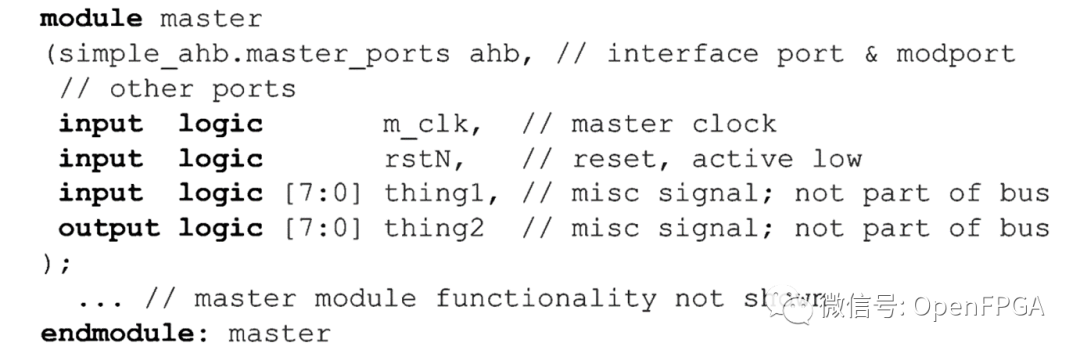

作为模块定义中Interface端口声明的一部分

作为与模块实例的接口连接的一部分

这两种方式都是可以综合的,但将modport作为modport定义的一部分来指定有一些优势,这将在下面几段中讨论。

在模块的interface声明中选择modport。要从一个Interface使用的特定调制端口可以直接指定为模块内Interface端口声明的一部分。要连接到Interface的modport被指定为:

<interface_name>.<modport_name>比如说。

只有特定类型的Interface端口可以指定一个modport作为端口声明的一部分。通用Interface端口不能指定一个modport。

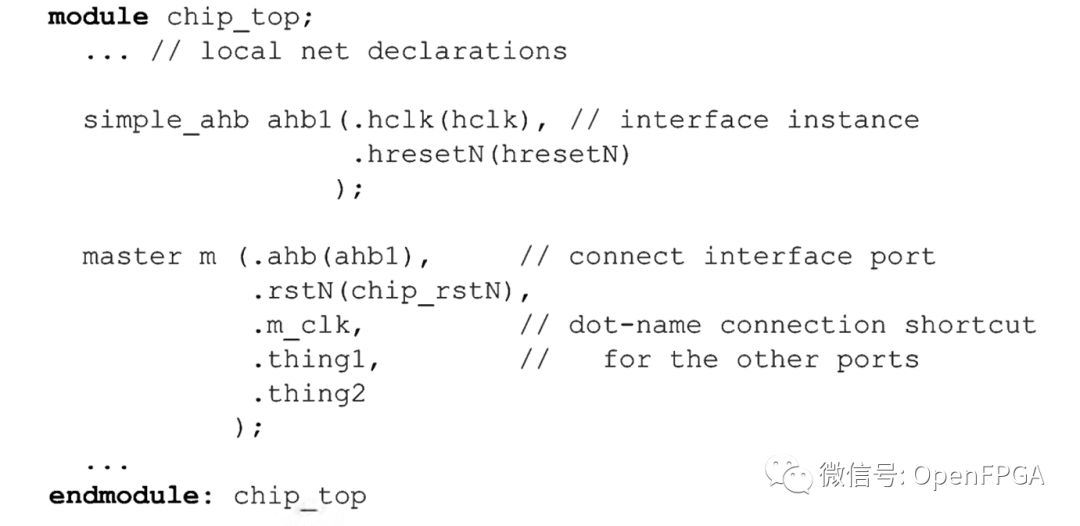

在实例化和连接这个主模块的上级模块,Interface的一个实例被连接到modport,而不指定modport的名称。例如:

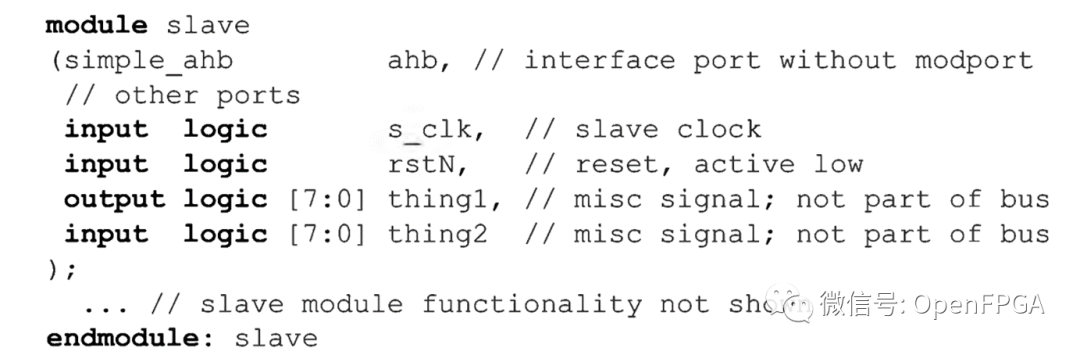

在module实例中选择modport。另一种编码方式是不在模块定义中选择modport,而是将modport的选择推迟到模块实例化时进行。下面的例子声明了第一个从属模块的端口作为simple_ahb Interface端口,但没有指定使用哪个modport定义。

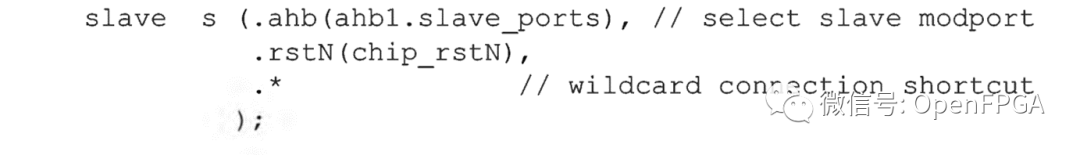

然后可以在模块实例化时指定Interface的具体模口,将一个Interface的实例连接到一个模块实例。该连接被指定为:

<interface instance_name>.<modport_name>比如说。

当在模块实例中指定要使用的modport时,模块定义可以使用特定类型的Interface端口或通用Interface端口类型。

| 注意事项 |

|---|

| 一个modport可以在模块端口定义或模块实例中选择,但不能同时选择。 |

| 最佳实践指南10-3 |

|---|

| 选择模块使用的modport作为模块的Interface端口声明的一部分。不要在网表级别选择modport。 |

将modport作为端口声明的一部分来指定,还可以使模块独立于其他模块进行综合。它还有助于使模块更加自我记录。阅读或维护该模块的工程师可以立即看到哪一个modport将被用于该模块。

在不指定modport的情况下连接到Interface。模块Interface端口可以连接到一个Interface实例,而不需要指定具体的modport定义。当没有指定modport时,Interface中的所有wire都被假定为有一个双向的inout方向。在仿真中,Interface中的变量被假定为ref类型。(ref端口允许端口的两边都可以读取和修改变量。ref端口是不可综合的,在本书中没有讨论)。综合编译器将没有指定modport的Interface端口中的所有信号视为inout双向端口。

使用modports来定义不同的连接集

在一个由几个不同模块使用的比较复杂的Interface中,可能不是每个模块都需要看到Interface中的同一组信号。Modports使得为每个使用该Interface的模块创建一个自定义的Interface视图成为可能。

一个模块只能访问其modport定义中列出的信号。这使得Interface中的一些信号有可能被完全隐藏,不被某些模块看到。例如,Interface可能包含一些信号,只有通过master_ports modport连接到Interface的模块才能使用,而通过s1ave_ports modport连接的模块不能使用。

完整的AMBA AHB总线有19个信号,其中有几个信号只由总线主机使用,而不是由总线从机使用。

下面的例子说明了一个自定义版本的simple_ahb Interface,增加了3个额外的AMBA AHB信号-hprot ,hburst和htrans,只被主模块使用。master_ports和slave_ports的modport声明确保主模块和从模块看到各自模块的正确信号集。

例10-5: 用modports的Interface来定制Interface信号的视图///

// Simple AMBA AHB Interface

///

//`begin_keywords "1800-2012"

interface simple_ahb (

input logic hclk, // bus transfer clk

input logic hresetN // bus reset, active low

);

logic [31:0] haddr; // transfer start address

logic [31:0] hwdata; // data sent to slave

logic [31:0] hrdata; // return data from slave

logic [ 2:0] hsize; // transfer size

logic hwrite; // 1 for write, 0 for read

logic hready; // 1 for transfer finished

// additional AHB signals only used by bus master

logic [ 3:0] hprot; // tranfer protection mode

logic [ 2:0] hburst; // transfer burst mode

logic [ 1:0] htrans; // transfer type

// master module port directions

modport master_ports (

output haddr, hwdata, hsize, hwrite, // to AHB slave

input hrdata, hready, // from AHB slave

input hclk, hresetN, // from chip level

// additional AHB signals only used by bus master

output hprot, hburst, htrans

);

// slave module port directions

modport slave_ports (

output hrdata, hready, // to AHB master

input haddr, hwdata, hsize, hwrite, // from AHB master

input hclk, hresetN // from chip level

);

endinterface: simple_ahb

//`end_keywords使用 simple_ahb .master_ports modport 的模块可以使用 hprot, hburst和 htrans 信号。一个使用simple_ahb.slave_ports modport的模块不能访问这3个信号。因为这些信号没有在slave_ports modport中列出,就好像这些信号根本不存在一样。

也有可能在一个Interface内有内部信号,这些信号通过任何modport都不可见。这些内部信号可能被lint检查器或Interface中的其他功能所使用。