摘要

本文分享了一种通用的Uart收发模块,可实现Uart协议所支持的任意波特率,任意位宽数据(5~8),任意校验位(无校验、奇校验、偶校验、1校验、0校验),任意停止位(1、1.5、2)的数据传输。此模块需要搭配FIFO使用,以消除发送端和接收端波特率不一致导致的累计误差。此模块经过多次测试与实际使用验证,可实现连续10万+数据无间隔连续发送与接收无错误。

关键词:Uart,FIFO,Verilog模块,校验位,停止位

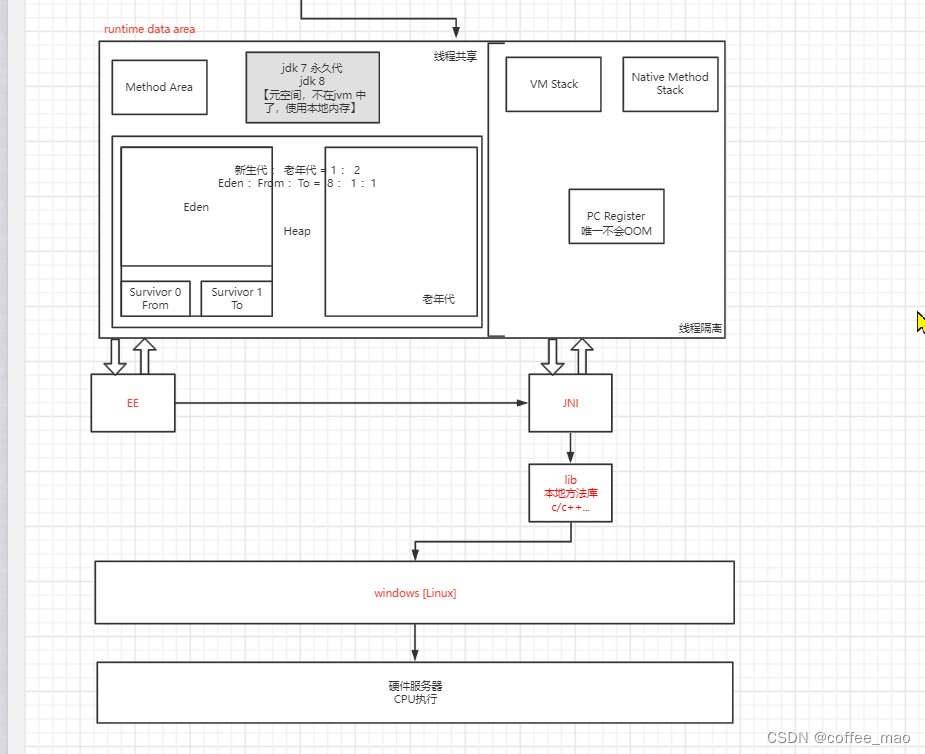

一. 什么是UART

UART,Universal Asynchronous Receiver/Transmitter,通用异步收发器,它将并行数据转换成串行数据进行传输。我们通常说的UART有两种意思,一种是UART协议,是串口通信采用的通用协议;一种是UART串口通信,指的是TTL电平的串口通信。关于UART和串口通信的关系的详细介绍可参考我的另一篇博客:

串口通信简介——发展历史与基本概念_徐晓康的博客

二. UART协议详解

UART协议由三根线组成,Tx,Rx,Gnd即发送、接收与地,不包含时钟线,属于全双工异步串行通信协议。

UART协议的波特率,Buad,表征数据传输的速率,因为UART协议用3.3V/5V表示逻辑1,用0V表示逻辑0,只有两个有效电平,所以UART协议的波特率与比特率是相等的。这部分属于数据通信的基本概念,可参考我的另一篇博客:数据通信的基本概念_徐晓康的博客。

需要注意的是, UART协议的数据传输双方需要预先约定好使用相同的波特率,这样发送端发出的数据才能被接收端正确出来。

UART协议的时序图:

空闲位:高电平,表示此刻Tx线或Rx线处于空闲状态,没有进行数据传输。

开始位:一个传输时钟周期的低电平,表示数据传输开始。

数据位:UART协议支持一次传输5、6、7或8位,每位占用一个传输时钟周期。

校验位:UART协议共支持五种校验方式:

-

无校验,即NONE,不进行校验,此时没有校验位;

-

奇校验,即ODD校验,指的是如果数据位中1的个数为奇数,奇校验值为0,否则为1;

-

偶校验,即EVEN校验,指的是如果数据位中1的个数为偶数,偶校验值为0,否则为1;

-

1校验,即MARK校验,校验位固定为1;

-

0校验,即SPACE校验,校验位固定为0。

停止位:停止位表示单次传输结束,停止位可占1 / 1.5 / 2个传输时钟周期。

一帧字符与下一帧字符间可间隔任意个空闲位,也可以完全没有间隔,即停止位后紧跟下一帧的开始位,但这样的话可能在连续传输大量数据时接收数据出错。因为Uart是无时钟的,发送端和接收端的波特率必然存在微小偏差,这导致接收端每一位的长度和发送端是不一样的,所以大量数据的无间隔传输会使得位长误差累加,最终导致接收错位。

三. uart收发模块框图与使用说明

参数:

| 参数名 | 说明 | 可选值 |

|---|---|---|

| CLK_FREQ_MHZ | 此模块的工作时钟频率,以MHz为单位 | 任意正数,默认100 |

| BAUD | 串口波特率,注意根据板卡uart收发芯片支持的波特率来设置 | 任意正数,默认115200 |

| DATA_BITS | 串口一帧包含的数据位的位宽,一般的串口芯片只支持数据位宽5/6/7/8 | 5,6,7,8(默认) |

| PARITY | 校验类型,无校验(默认),奇校验,偶校验,1校验,0校验 | “NONE”(默认),“ODD”, “EVEN”, “MARK”, “SPACE” |

| STOP_BITS | 停止位位宽,1/1.5/2 | 1(默认),1.5,2 |

信号:

| 信号分组 | 信号名 | 方向 | 说明 |

|---|---|---|---|

| 与发送FIFO连接的接口 | tx_cclk_fwft_fifo_8wxxd_empty | input | 发送FWFT 8bit任意深度FIFO空接口 |

| tx_cclk_fwft_fifo_8wxxd_dout[7 : 0] | input | 发送FWFT 8bit任意深度FIFO数据输出接口 | |

| tx_cclk_fwft_fifo_8wxxd_rd_en | output | 发送FWFT 8bit任意深度FIFO读取使能接口 | |

| 与接收FIFO连接的接口 | rx_cclk_fwft_fifo_8wxxd_full | input | 接收FWFT 8bit任意深度FIFO满接口 |

| rx_cclk_fwft_fifo_8wxxd_din[7 : 0] | output | 接收FWFT 8bit任意深度FIFO数据输入接口 | |

| rx_cclk_fwft_fifo_8wxxd_wr_en | output | 接收FWFT 8bit任意深度FIFO写入使能接口 | |

| 接收错误指示 | rdata_error | output | 指示接收数据错误,高电平有效, 当根据接收数据计算得到的校验位与实际接收的校验位不同时, 置高一个时钟周期 |

| 物理引脚 | uart_tx | output | uart发送线 |

| uart_rx | input | uart接收线 | |

| 时钟与复位 | clk | input | 模块工作时钟,应输入频率与参数CLK_FREQ_MHZ相等的时钟 |

| rstn | input | 同步复位信号,不连接也可正常工作 |

使用说明:

此模块需要外接一个发送FWFT 8bit任意深度FIFO和一个接收FWFT 8bit任意深度FIFO,FIFO位宽固定为8,即使要发送的数据位宽为5~7,也可以直接写入FIFO,如设定的Uart数据位宽为5,那么将5bit数据写入8bit FIFO中,发送模块也会相应的只取低5位的数据。

当要发送数据时,上层模块只需往发送FIFO中写数据即可,此模块检测到发送FIFO非空时,就会将FIFO中数据发送出去;

此模块会将Uart接收到的数据写入到接收FIFO中,上层模块需要去接收FIFO中读数据以拿到Uart接收到的数据。

四. Uart IP框图与参数设置

可将Uart收发模块封装为IP。

五. 顶层模块代码

/*

* @Author : Xu Xiaokang

* @Email : XudaKang_up@qq.com

* @Date : 2022-05-05 11:11:22

* @LastEditors : Xu Xiaokang

* @LastEditTime : 2022-11-09 11:17:24

* @Filename :

* @Description :

*/

/*

! 模块功能: 在uart收发模块外层再封装一层FIFO,包含发送FIFO与接收FIFO,以解决波特率误差导致接收位偏移的问题

* 思路:

1.

*/

module uartRTUseFIFO

#(

parameter CLK_FREQ_MHZ = 100,

parameter BAUD = 115200, // 波特率, 9600, 19200, 38400, 57600, 115200, 230400, 460800, 921600

parameter DATA_BITS = 8, // 数据位宽度, 可选5, 6, 7, 8

parameter PARITY = "NONE", // 校验 "NONE", "ODD", "EVEN", "MARK", "SPACE"

parameter STOP_BITS = 1 // 停止位宽度可选1, 1.5, 2

)(

// 发送数据 FWFT FIFO

input wire tx_cclk_fwft_fifo_8wxxd_empty,

input wire [7 : 0] tx_cclk_fwft_fifo_8wxxd_dout,

output wire tx_cclk_fwft_fifo_8wxxd_rd_en,

// 接收数据 FWFT FIFO

input wire rx_cclk_fwft_fifo_8wxxd_full,

output wire [7 : 0] rx_cclk_fwft_fifo_8wxxd_din,

output wire rx_cclk_fwft_fifo_8wxxd_wr_en,

output wire rdata_error, // 接收错误

output wire uart_tx,

input wire uart_rx,

input wire clk,

input wire rstn

);

//++ 实例化串口收发模块 ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

wire [DATA_BITS - 1 : 0] rdata; // 接收到的数据

wire rdata_valid; // 指示接收数据有效; 高电平有效

wire [DATA_BITS - 1 : 0] tdata; // 要发送的数据

wire tdata_valid; // 指示发送数据有效; 此信号上升沿有效

wire uart_tx_ready; // 发送准备就绪

uartTx #(

.CLK_FREQ_MHZ (CLK_FREQ_MHZ ),

.BAUD (BAUD ),

.DATA_BITS (DATA_BITS ),

.PARITY (PARITY ),

.STOP_BITS (STOP_BITS )

) uartTx_dut (

.tdata (tdata ),

.tdata_valid (tdata_valid ),

.uart_tx_ready (uart_tx_ready ),

.uart_tx (uart_tx ),

.clk (clk ),

.rstn (rstn )

);

uartRx #(

.CLK_FREQ_MHZ (CLK_FREQ_MHZ ),

.BAUD (BAUD ),

.DATA_BITS (DATA_BITS ),

.PARITY (PARITY ),

.STOP_BITS (STOP_BITS )

) uartRx_dut (

.rdata (rdata ),

.rdata_valid (rdata_valid ),

.rdata_error (rdata_error ),

.uart_rx (uart_rx ),

.clk (clk ),

.rstn (rstn )

);

//-- 实例化串口收发模块 ------------------------------------------------------------

//++ 发送数据FIFO接口连接 ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

assign tdata = tx_cclk_fwft_fifo_8wxxd_dout[DATA_BITS - 1 : 0];

reg tx_cclk_fwft_fifo_8wxxd_rd_en_temp;

always @(posedge clk) begin

tx_cclk_fwft_fifo_8wxxd_rd_en_temp <= uart_tx_ready && tdata_valid;

end

assign tx_cclk_fwft_fifo_8wxxd_rd_en = ~tx_cclk_fwft_fifo_8wxxd_empty && tx_cclk_fwft_fifo_8wxxd_rd_en_temp;

assign tdata_valid = ~tx_cclk_fwft_fifo_8wxxd_empty;

//-- 发送数据FIFO接口连接 ------------------------------------------------------------

//++ 接收数据FIFO接口连接 ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

reg rdata_valid_r1;

always @(posedge clk) begin

rdata_valid_r1 <= rdata_valid;

end

assign rdata_valid_pedge = rdata_valid && ~rdata_valid_r1;

assign rx_cclk_fwft_fifo_8wxxd_wr_en = ~rx_cclk_fwft_fifo_8wxxd_full && rdata_valid_pedge;

assign rx_cclk_fwft_fifo_8wxxd_din = rdata;

//-- 接收数据FIFO接口连接 ------------------------------------------------------------

endmodule

六. 回环测试示例

回环测试顶层模块代码:

/*

* @Author : Xu Xiaokang

* @Email : xuxiaokang_up@qq.com

* @Date : 2022-10-31 16:53:45

* @LastEditors : Xu Xiaokang

* @LastEditTime : 2022-11-09 11:13:46

* @Filename :

* @Description :

*/

/*

! 模块功能: uart收发,实现环路测试,即将接收到的数据发出来

* 思路:

1.

*/

module uartLoopTop

(

input logic uart_rx,

output logic uart_tx,

input logic fpga_input_clk_p,

input logic fpga_input_clk_n,

input logic rstn

);

//++ 时钟与复位 ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

logic clk;

clk_wiz_0 clk_wiz_0_u0 (

.clk_in1_p (fpga_input_clk_p),

.clk_in1_n (fpga_input_clk_n),

.clk_out1 (clk )

);

//-- 时钟与复位 ------------------------------------------------------------

// ++ 参数设置 ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

localparam CLK_FREQ_MHZ = 100;

localparam BAUD = 115200; // 波特率, 9600, 19200, 38400, 57600, 115200, 230400, 460800, 921600

localparam DATA_BITS = 8; // 数据位宽度, 可选5, 6, 7, 8

localparam PARITY = "ODD"; // 校验 "NONE", "ODD", "EVEN", "MARK", "SPACE"

localparam STOP_BITS = 2; // 停止位宽度, 可选1, 1.5, 2

// -- 参数设置 ------------------------------------------------------------

//++ 实例化uart模块 ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

(* mark_debug *) logic rx_cclk_fwft_fifo_8wxxd_full;

(* mark_debug *) logic [7 : 0] rx_cclk_fwft_fifo_8wxxd_din;

(* mark_debug *) logic rx_cclk_fwft_fifo_8wxxd_wr_en;

(* mark_debug *) logic rdata_error;

(* mark_debug *) logic tx_cclk_fwft_fifo_8wxxd_empty;

(* mark_debug *) logic [7 : 0] tx_cclk_fwft_fifo_8wxxd_dout;

(* mark_debug *) logic tx_cclk_fwft_fifo_8wxxd_rd_en;

uartRTUseFIFO #(

.CLK_FREQ_MHZ (CLK_FREQ_MHZ),

.BAUD (BAUD),

.DATA_BITS (DATA_BITS),

.PARITY (PARITY),

.STOP_BITS (STOP_BITS)

) uartRTUseFIFO_u0 (

.rx_cclk_fwft_fifo_8wxxd_full (rx_cclk_fwft_fifo_8wxxd_full ),

.rx_cclk_fwft_fifo_8wxxd_din (rx_cclk_fwft_fifo_8wxxd_din ),

.rx_cclk_fwft_fifo_8wxxd_wr_en (rx_cclk_fwft_fifo_8wxxd_wr_en),

.rdata_error (rdata_error ),

.tx_cclk_fwft_fifo_8wxxd_empty (tx_cclk_fwft_fifo_8wxxd_empty),

.tx_cclk_fwft_fifo_8wxxd_dout (tx_cclk_fwft_fifo_8wxxd_dout ),

.tx_cclk_fwft_fifo_8wxxd_rd_en (tx_cclk_fwft_fifo_8wxxd_rd_en),

.uart_tx (uart_tx ),

.uart_rx (uart_rx ),

.clk (clk ),

.rstn (rstn )

);

//-- 实例化uart模块 ------------------------------------------------------------

//++ 实例化FWFT FIFO ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

cclk_fwft_fifo_8w1024d cclk_fwft_fifo_8w1024d_u0 (

.clk (clk ), // input wire clk

.srst (~rstn ), // input wire srst

.din (rx_cclk_fwft_fifo_8wxxd_din ), // input wire [7 : 0] din

.wr_en (rx_cclk_fwft_fifo_8wxxd_wr_en), // input wire wr_en

.full (rx_cclk_fwft_fifo_8wxxd_full ), // output wire full

.rd_en (tx_cclk_fwft_fifo_8wxxd_rd_en), // input wire rd_en

.dout (tx_cclk_fwft_fifo_8wxxd_dout ), // output wire [7 : 0] dout

.empty (tx_cclk_fwft_fifo_8wxxd_empty) // output wire empty

);

//-- 实例化FWFT FIFO ------------------------------------------------------------

endmodule

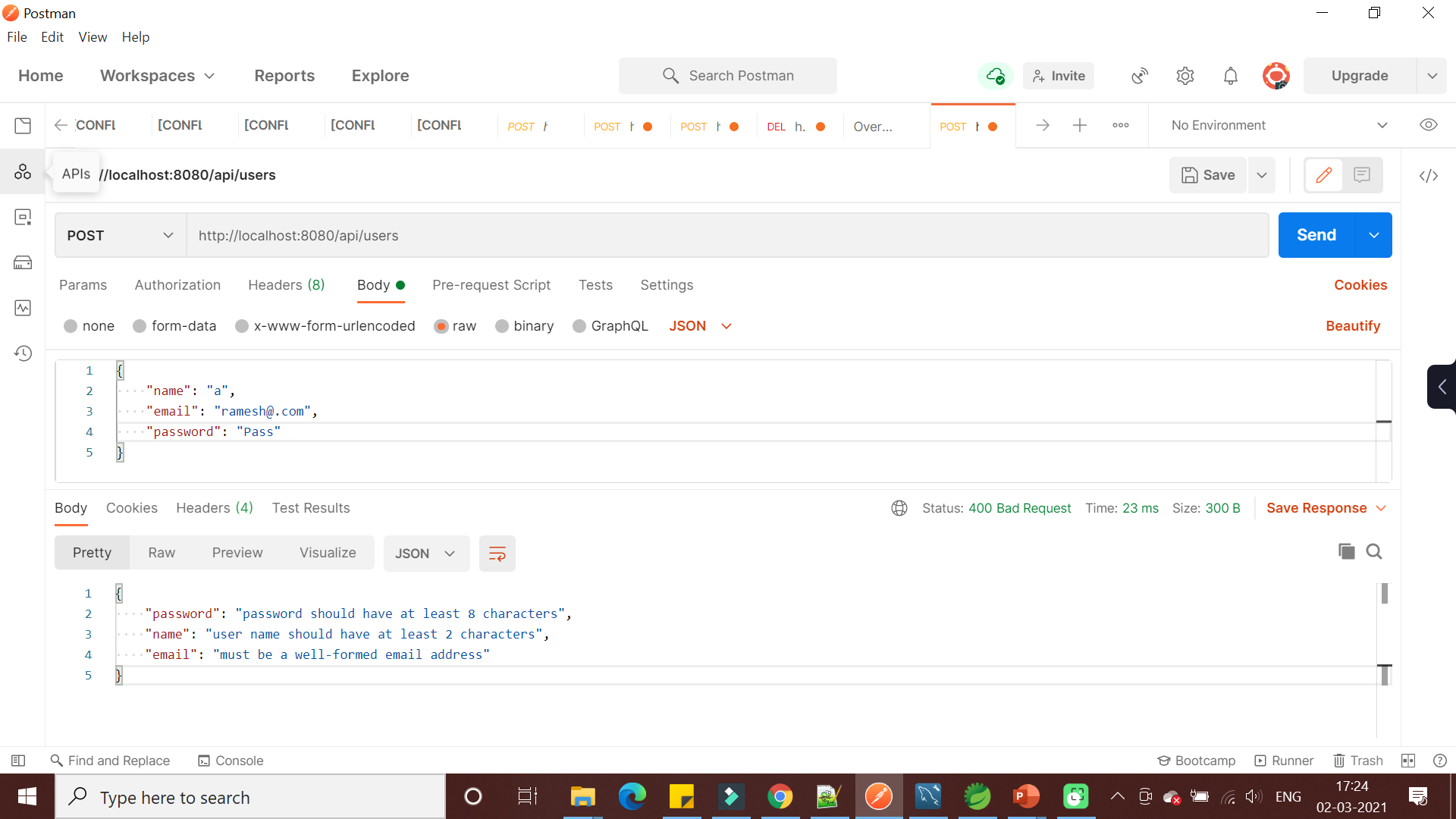

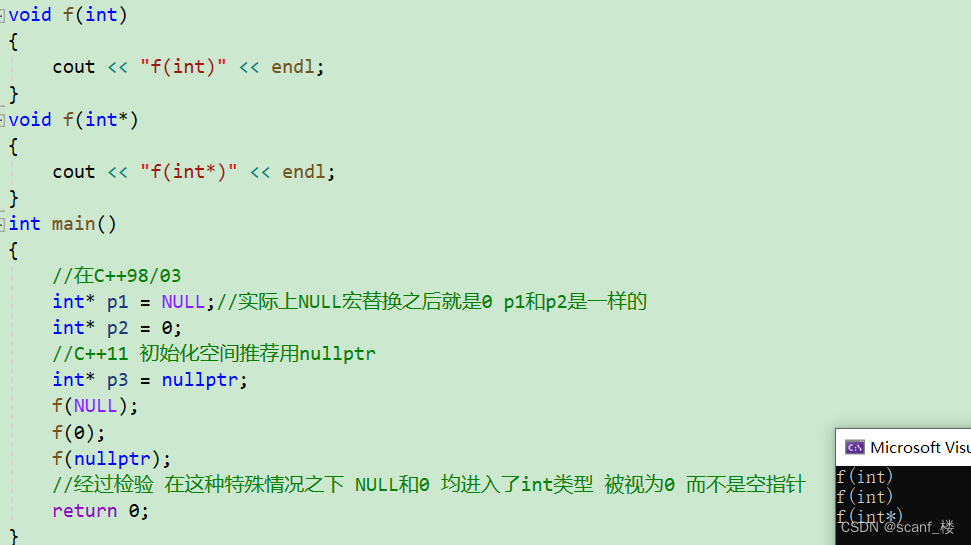

测试用的FPGA板卡:明德扬MP5620,板上串口转USB芯片为SILICON LABS公司的CP2102-GM,其支持的串口协议如下图所示:

使用的串口上位机工具:正点原子XCOM V2.6。

需要特别注意的是:上位机的波特率与Verilog模块设置的波特率是有一定差距的,这个差距的原因可能是上位机设置的波特率不准,也可能是因为波特率设置是整数时钟分频得到的,无法精确到小数位,所以上位机和Verilog模块间uart的波特率并不是严格一致的,可能是115200与115201的区别,正常情况这么小的差距数据也能被正常识别。但是XCOM在一次性发送多帧时,两帧之间是没有任何间隔的,这使得在连续传输多帧后,接收数据错位。

测试界面如下:

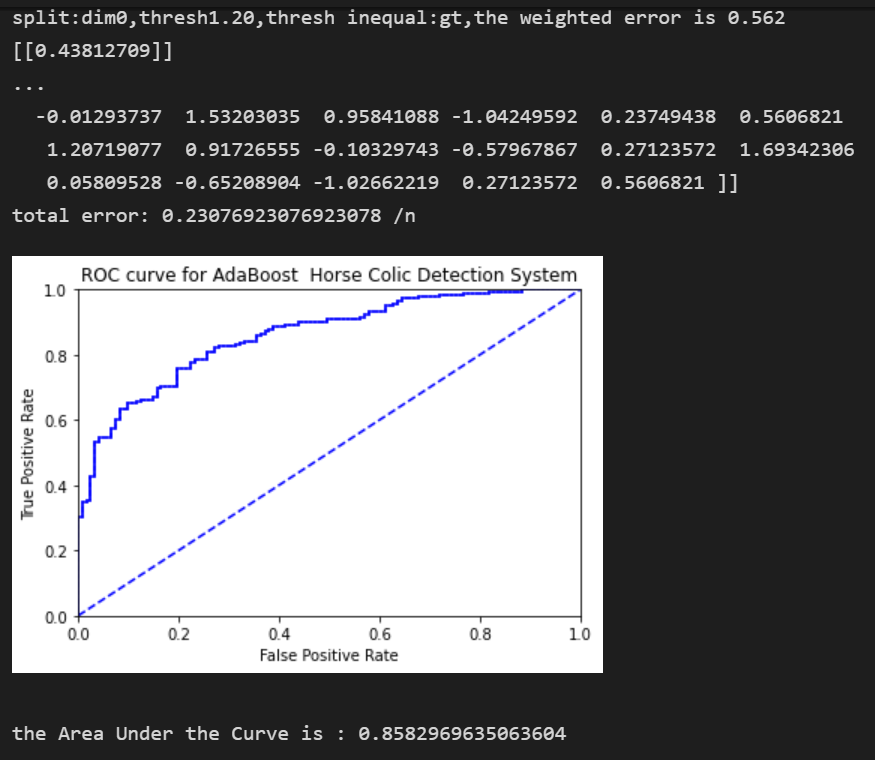

在115200波特率,8数据位,ODD校验,2停止位的条件下,回环测试通过。接着更改参数(需要USB转串口的芯片支持该组参数),进行其它条件下的试验,均无问题。

在连续发送10万个字节数据时,仍能返回正确的数据,这是因为加入了FIFO,波特率误差被FIFO缓冲消除了,如果不加FIFO且无间隔的发送数据,则连续发送10几个数据就可能发生接收错位,使得返回数据与发送数据不一致。

七. 模块代码与工程分享

模块代码自取:Verilog功能模块——Uart收发 · 徐晓康/Verilog功能模块 - 码云 - 开源中国 (gitee.com)

工程分享(内含所有模块代码):

K7TryUart. Uart回环测试 Vivado2021.2工程。

欢迎大家关注我的公众号:徐晓康的博客,回复以下代码获取。

下载|4623

建议复制过去不会码错字!

徐晓康的博客持续分享高质量硬件、FPGA与嵌入式知识,软件,工具等内容,欢迎大家关注。