AXI4 总线是 ARM 公司开发的一种总线,广泛应用于 Xilinx 的 IP 核中,比如笔者近期涉及 DDR 的读写控制,需要用到 MIG IP 核,这个 IP 核就通过 AXI4 总线进行控制。

AXI4 共有 5 种通道:读地址通道 ARC,读数据通道 DRC,写数据通道 AWC,写数据通道 DWC,写回复通道 RC。以上 5 种通道都是单向通道,通过 Valid/Ready 握手机制实现读写控制。

AXI 握手机制

AXI 通过两个信号(valid、ready)实现握手,发送方(主)通过置高 vaild 信号表示地址/数据/控制信息已准备好,并保持在消息总线上;接收方(从)通过置高 ready 信号表示接收方已做好接收的准备。在 ACLK 上升沿,若 vaild、ready 同时为高,则进行数据传输。

需要注意,valid 信号必须是独立的,而 ready 信号可以是独立的也可以依赖于 valid 信号。否则若 valid 依赖于 slave 给出的 ready 信号,而 ready 又依赖于 master 给出的 valid 信号,将出现死锁。上述谈及的依赖不止组合逻辑,时序逻辑乃至 FIFO 也是。(所以其实 ready 信号独立,而 valid 依赖于 ready 信号也是可行的),然而强烈建议 ready、valid 完全独立,这样主从端将均具有中止通信的能力,从而可以从主从双向控制通信速度。若想要从机接收全部的来自主机的数据,可径设 ready = H 。

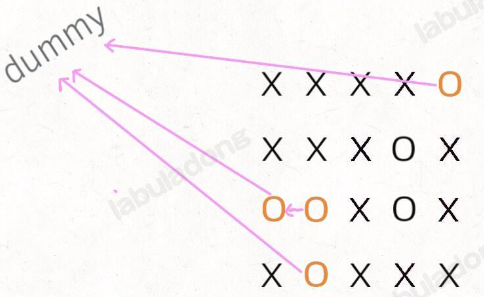

根据 valid、ready 到达时间,可以分为 3 种情况,分别如下图

应当注意到,在 valid 置高的同时,发送方就应该给出有效数据,并将有效数据保持在总线,而在之后的 ACLK 上升沿,若 valid、ready 均有效,则应更新有效数据。

读写通信流程

写流程如上图,涉及写地址通道 AWC、写数据通道 DWC、写回复通道 RC 三个通道。首先 master 在 AWC 上给出写地址和控制信息,然后在 DWC 上传输数据,AXI 的数据传输是突发性的,一次可传输多个数据,在传输最后一个数据时,须同步给出 last 信号以表示数据传输即将终止,之后 slave 将在 RC 上给出写回复消息,对本次数据传输表示确认。

读流程如上图,涉及读地址通道 ARC、读数据通道 DRC 两个通道。首先 master 在 ARC 上给出读地址和控制消息,slave 将在 DRC 上给出数据。值得注意的是,DRC 集成了读回复功能,且是从 slave 发送给 master 的,在 slave 完成数据传输后,会在 DRC 上给出回复消息,标志一次读取结束。

AXI 可以连接成多对多的拓扑,这可以借助 AXI Interconnect IP 来实现。

各个通道的信号说明

全局信号

- ACLK,全局时钟信号,所有读写操作均发生在 ACLK 上升沿。

- RESETn,全局同步复位信号,低电平有效。

AWC 通道

- AWID,写事务 ID,源自 master,标识本次写事务。

- AWADDR,写地址,源自 master,突发传输第一个数据的写入地址,注意该地址是字节地址。

- AWLEN,源自 master,突发传输长度,Length = AxLength + 1,即设为 0 时表示本次传输只传输一个数据。在 INCR 模式可以传输 1~256 个数据,其他类型只能传输 1~16 个,在WRAP 模式下,则只支持 2,4,8,16 个的数据个数。

- AWSIZE,写过程突发传输宽度,源自 master,标识每个数据的大小, 2 a w s i z e B y t e s 2^{awsize}Bytes 2awsizeBytes ,若 AWSIZE=0,表示每次传输 2 0 = 1 B y t e 2^0=1 Byte 20=1Byte ,如数据位宽为 64 bit(8 Byte),则 awsize 应为 3 。突发传输数据宽度不能超过数据总线本身的位宽,当数据总线位宽大于突发传输宽度时,根据协议的相关规定,将数据在部分数据线上传输。

- AWBURST,设置突发传输类型,有 FIXED(0b00)、INCR(0b01)、WRAP(0b10)三种。FIXED 模式中所有数据都使用起始地址;INCR模式中后续数据地址依次递增,递增值为 2 a w s i z e 2^{awsize} 2awsize ;WRAP 模式下,根据起始地址获得绕回边界地址(wrap boundary)和最大地址,绕回地址与起始地址相同,而最大地址 = wrap boundary + (N_bytes x burst_len),当当前地址大于最大地址时,将回到绕回地址。

- AWLOCK,设置是否进行独占传输,默认 0,置高时表示独占

- AWCACHE,Memory attributes,bit0:Bufferable,bit1:Modifiable,bit2:Other Allocate,bit3:Allocate。具体详见官方手册。

- AWWPROT,Access attributes,用于避免内存受意外事务影响,具体详见官方手册。

- AWQOS,Quality of Service identifier,详见官方手册。

- AWVALID,略

- AWREADY,略

DWC 通道

- WDATA,略

- WSTRB,写有效字段,WSTRB[n] 为高时表示 WDATA 的第 n 个字节有效,即 WDATA[8n+7 : 8n] 有效;WSTRB 必须仅在对应 Byte 通道有效时置高,当 WVALID = L 时,WSTRB 可以任意值,但强烈建议保持为低。

- WLAST,标识最后一个 transfer,master 发出。

- WVALID,略

- WREADY,略

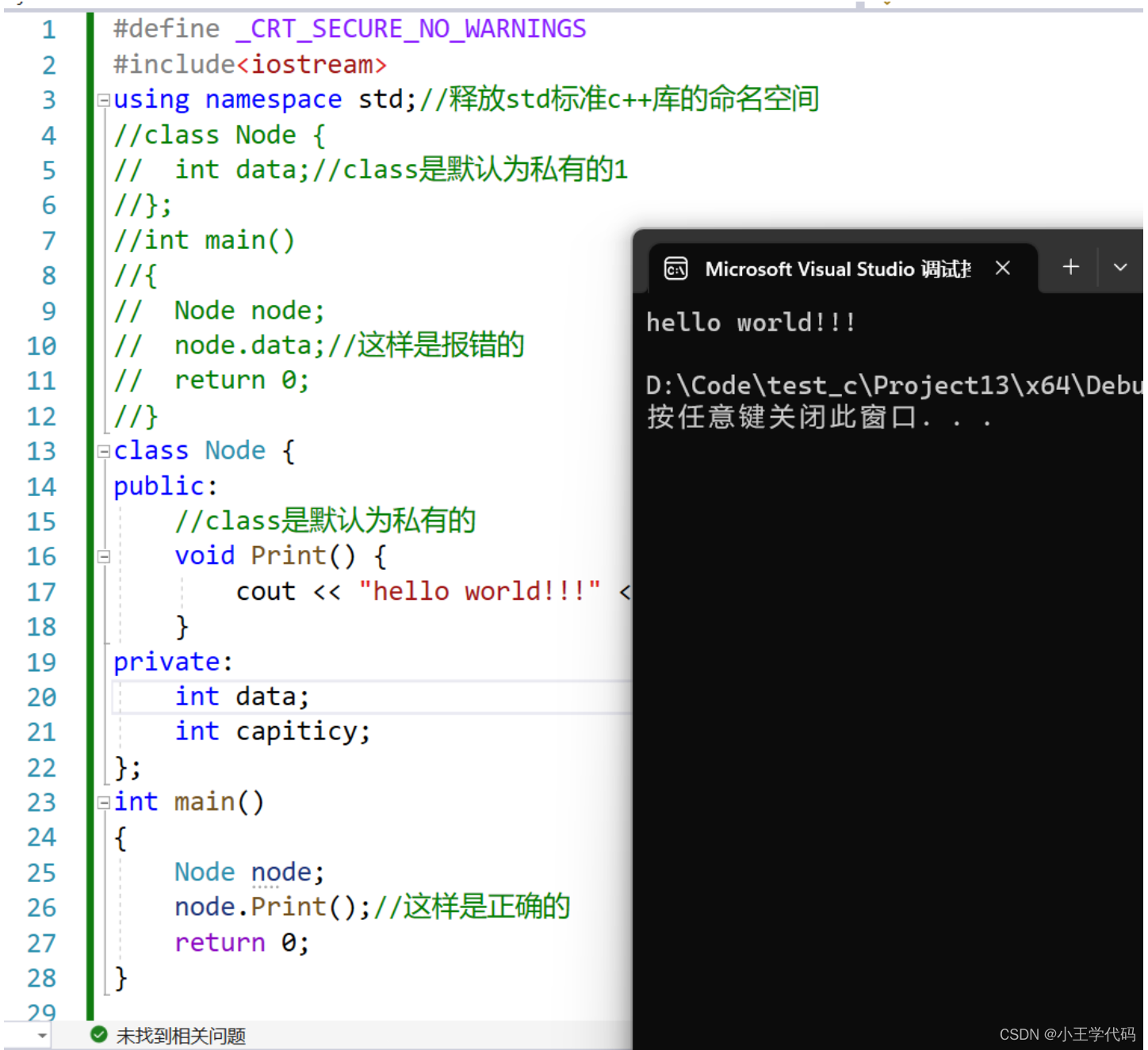

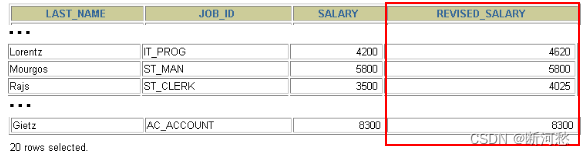

注意,AXI 读写地址是与数据位宽对齐的,如下图所示的窄传输(单次 transfer 的位宽小于用户数据位宽)例子,用户数据 size 为 8 Byte,而起始地址设为了 4,则会先将高 4 字节写入,而低 4 字节将在地址 8 进行写入。

有时候会遇到起始地址与突发传输的数据位宽不对齐的情况,这时可以通过填充无效数据并将对应字节的 WSTRB 置零来对齐数据,读操作时遇到非对齐情况也做同样处理。如下图所示

RC 通道

- BID,写事务 ID,slave 发出,应答给出相同事务 ID 号的写事务。

- BRESP,写应答,slave 发出,0b00 表示 Okey,其他详见 AMBA 官方手册。

- BVALID,略

- BREADY,略

ARC 通道

- ARID,读事务 ID。

- ARADDR,读事务首地址。

- ARLEN,同 AWLEN

- ARSIZE,同 AWSIZE

- ARBURST,同 ARBURST

- ARLOCK,同 AWLOCK

- ARCACHE,设置内存属性,bit0:Bufferable,bit1:Modifiable,bit2:Allocate,bit3:Other Allocate。注意 Allocate、Other Allocate 在 ARLOCK 和 AWLOCK 中的位置不同。

- ARPROT,同 AWPROT

- ARQOS,同 AWQOS

- ARVALID,略

- ARREADY,略

DRC 通道

- RID,读事务 ID,应答信号。

- RDATA,略

- RRESP,读应答,slave 发出,0b00 表示 Okey,其他详见 AMBA 官方手册。

- RLAST,slave 发出,标识最后一个读数据。

- RVALID,略

- RREADY,略

后记

更具体的 AXI 信息详见 ARM 的 AMBA AXI Protocol 手册,下载地址 。

![[计算机图形学]辐射度量学、渲染方程与全局光照(前瞻预习/复习回顾)](https://img-blog.csdnimg.cn/b8143a8ba19a477baa8e1d0c5d20c69c.png)