目录

QPSK调制解调使用参数:

调制:

解调:

FPGA工程架构:

仿真参数:

仿真展示:

调制:

解调:

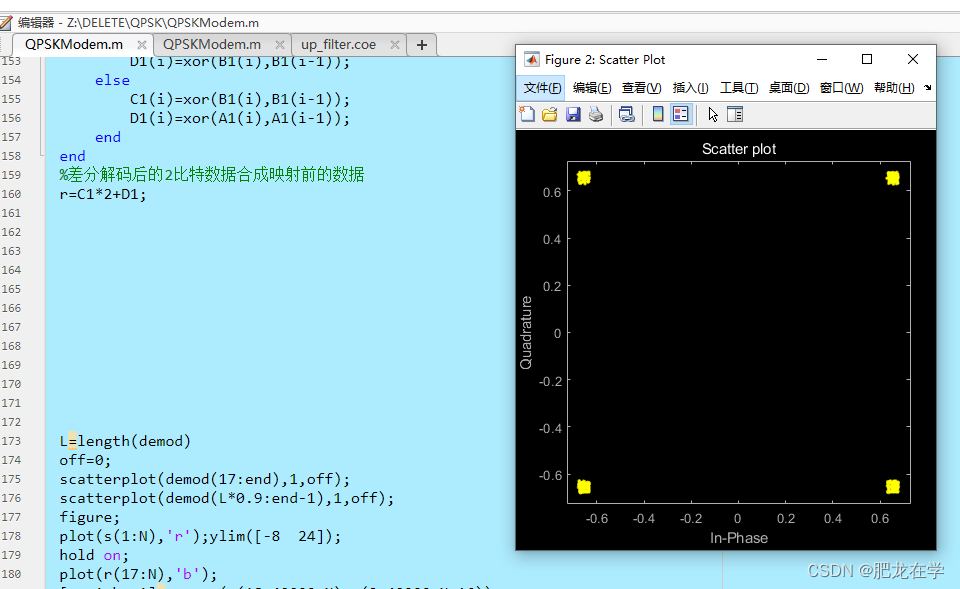

MATLAB星座图展示:

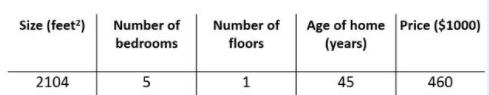

QPSK调制解调使用参数:

采样率为4M,符号速率为1M,载波速率为1M,即一个符号采四个点

无噪声!

调制:

1.对二进制码元进行串并转换分为IQ两路

2.对IQ两路码元进行4倍上采样

3.对2中处理后的数据进行成型滤波

4.对3中处理后的IQ两路数据与载波相乘并相加得到调制信号

解调:

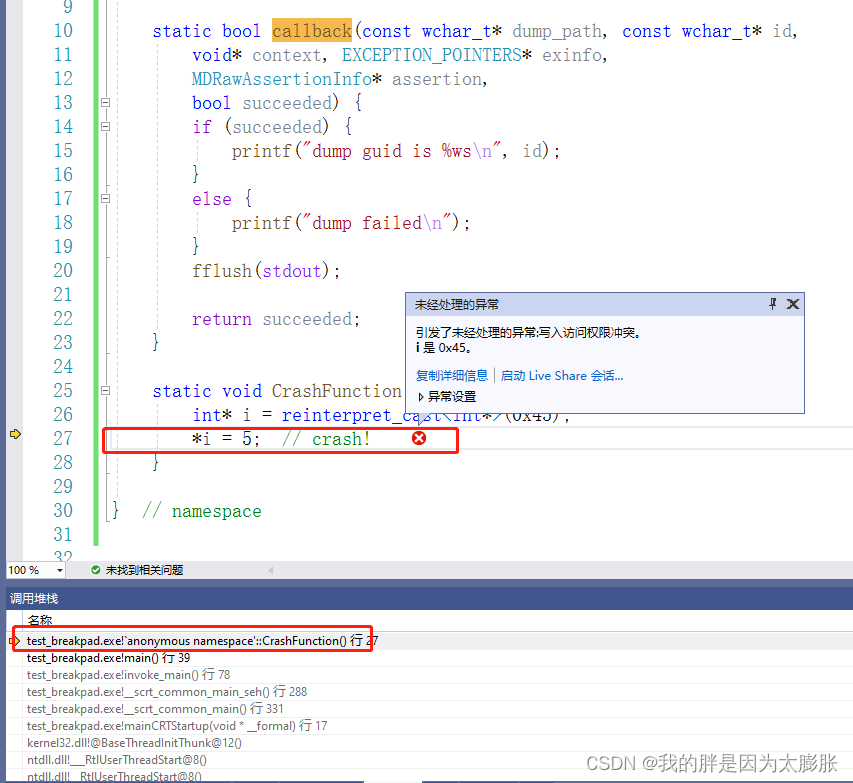

1.对调制信号进行数字下变频,然后经过低通滤波得到基带信号

2.对1处理后的数据进行符号同步(Gardner环)并得到同步时钟

3.在同步时钟下对2处理后的数据进行载波同步以及相差恢复处理

4.进行硬判决得到4进制码元

5.进行并串转换得到二进制码元

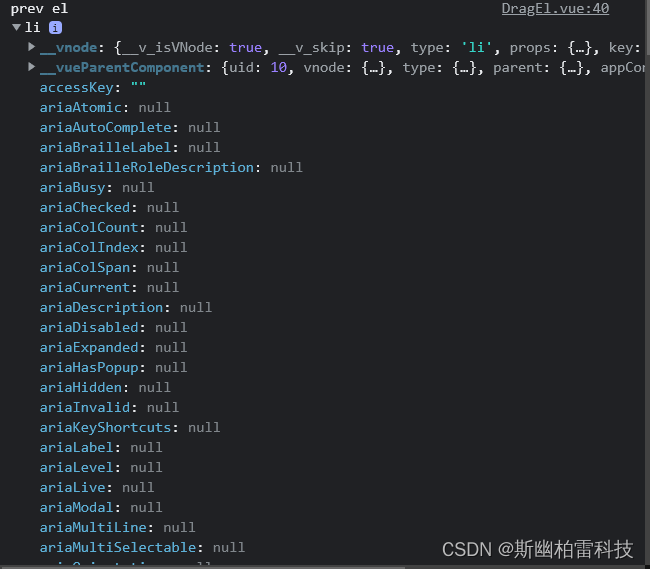

FPGA工程架构:

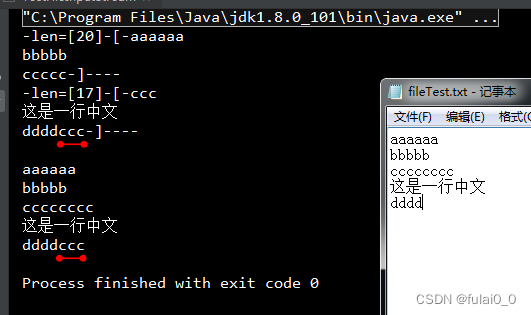

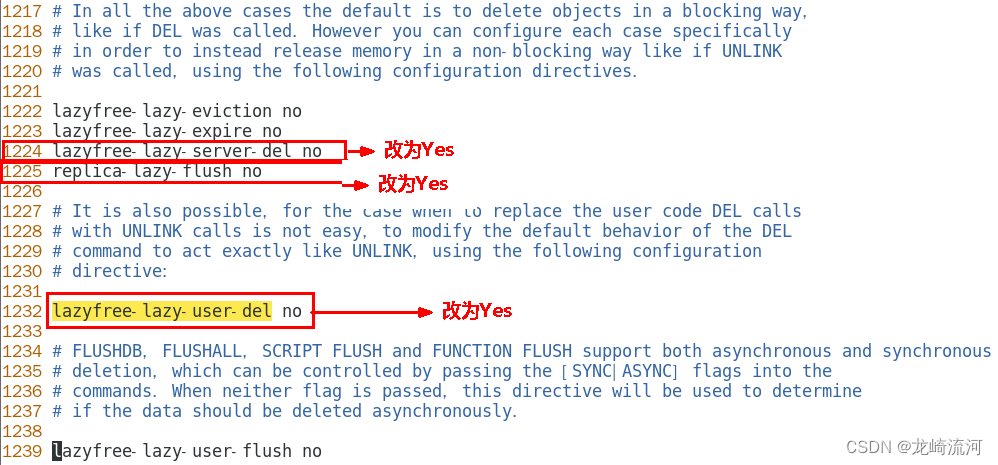

仿真参数:

1.仿真文件中给了5000个随机二进制01码元

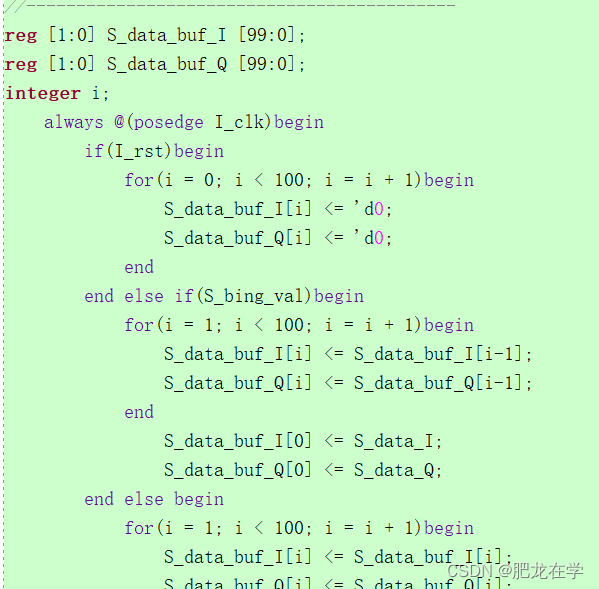

2.该工程可以保证连续100个码元正确解调!当然也可以更多,但是不能无限连续(因为要对数据进行上采样),如图1中将99扩为999那么就可以保证连续1000个码元正确解调,但这样会占用更多的寄存器资源

图1

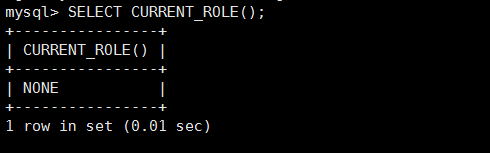

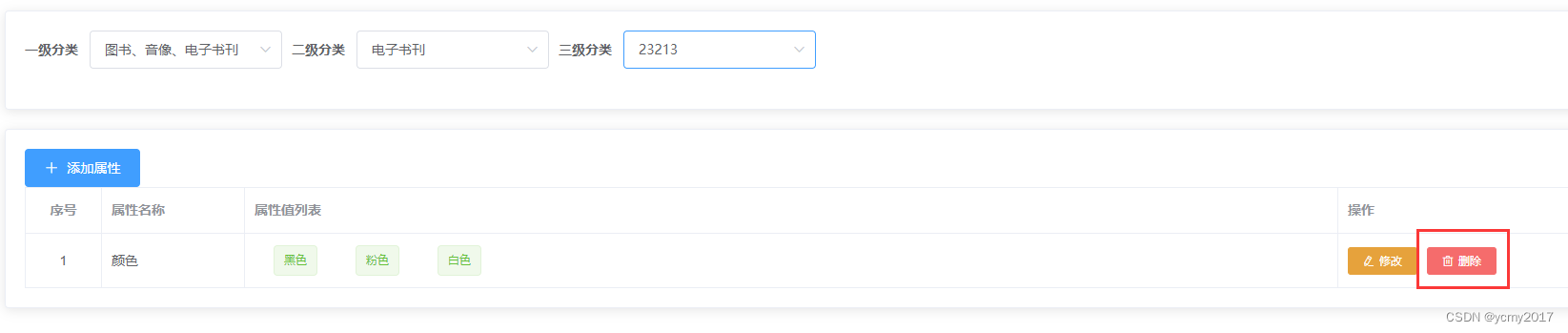

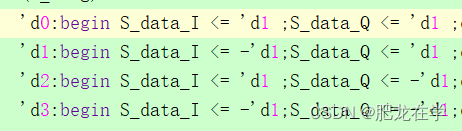

3.映射关系如图2所示:

图2

仿真展示:

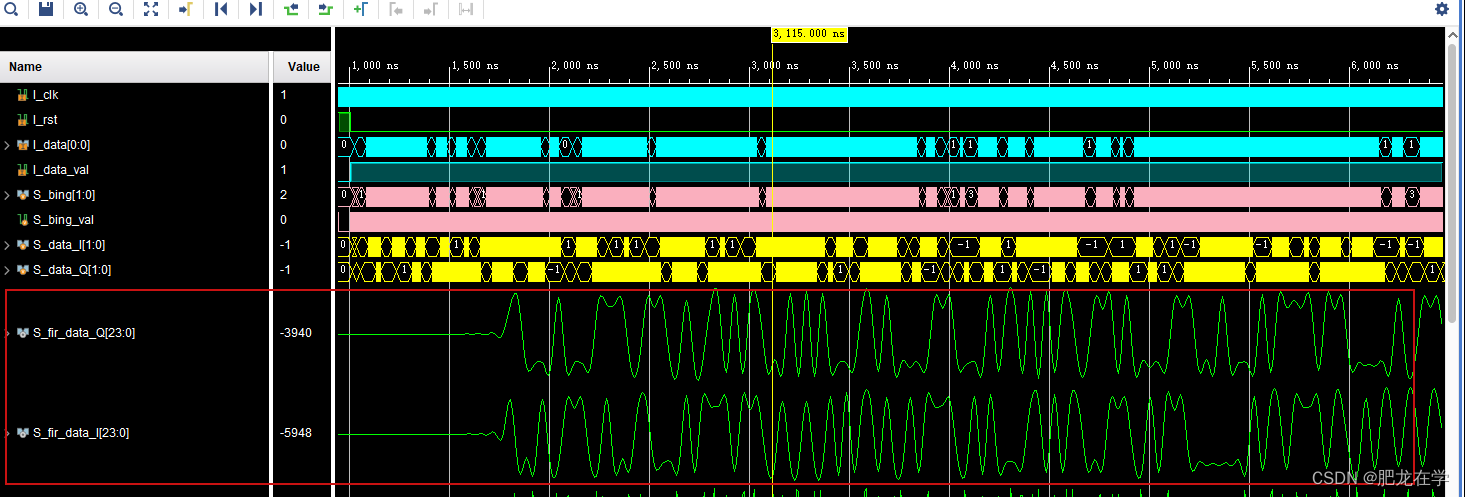

调制:

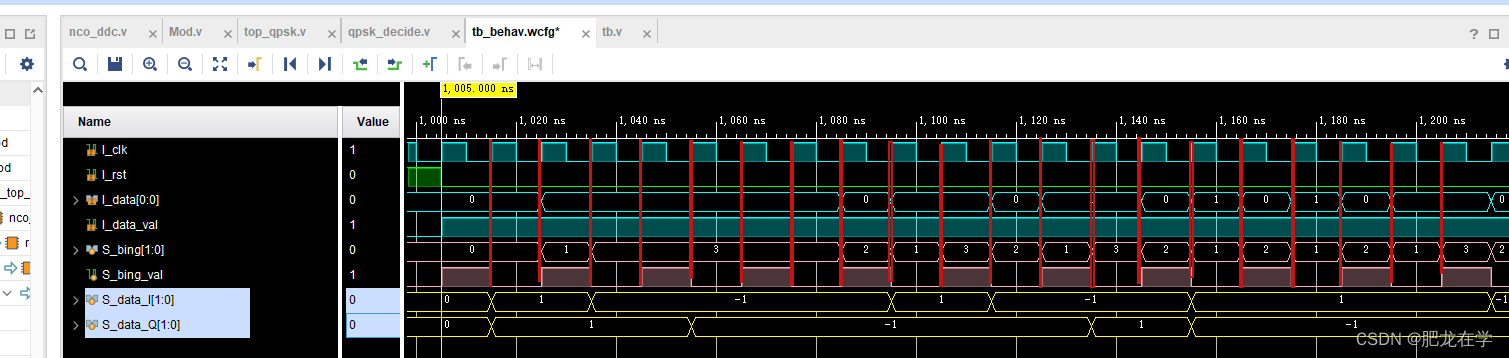

1005ns系统复位结束,开始运行

1005ns之后,可以看到发送码元数据I_data[0:0]为001111110110110101011(图3)

S_bing[1:0]为串并转换之后的数据,S_bing_val代表当前时钟并行数据是有效的(图3)

S_data_i与S_data_q是串并转换之后经过映射的iq两路数据(对应坐标轴四个象限星座点)

经过上采样后的IQ两路数据(4倍)经过成型滤波后波形:

IQ两路与载波相乘之后再相加生成调制信号:

解调:

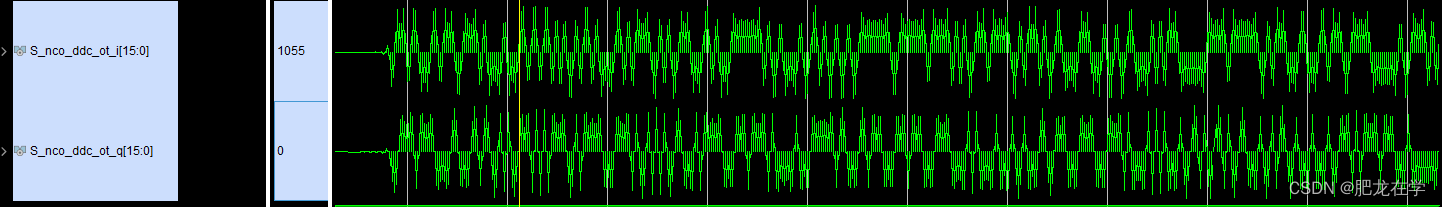

先经过数字下变频将信号搬到基带:

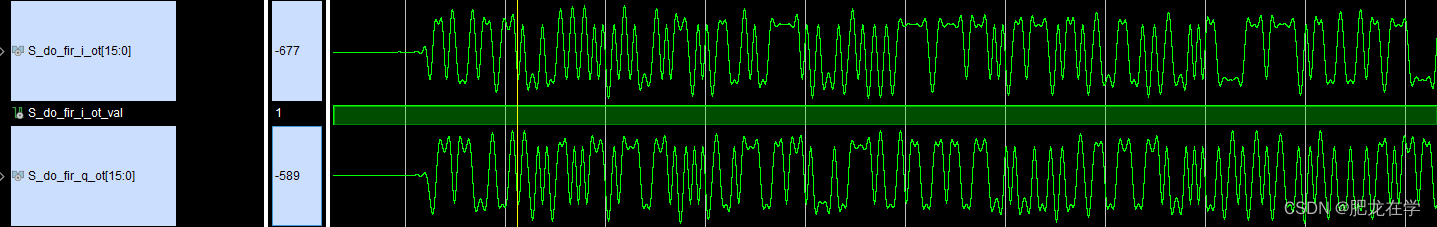

再经过低通滤波滤除高频分量得到基带信号

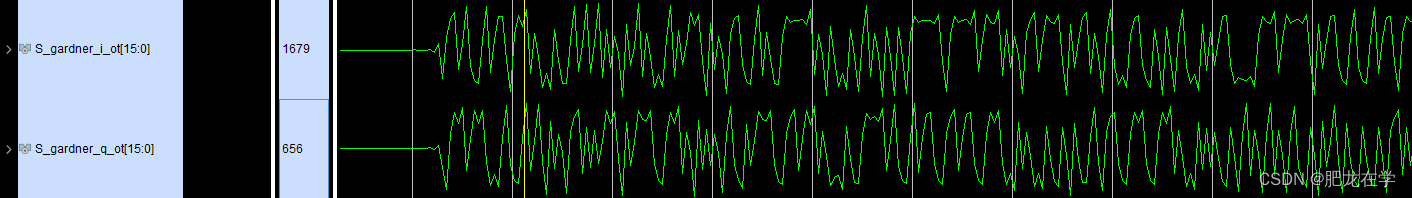

再经过Gardner环进行符号同步:

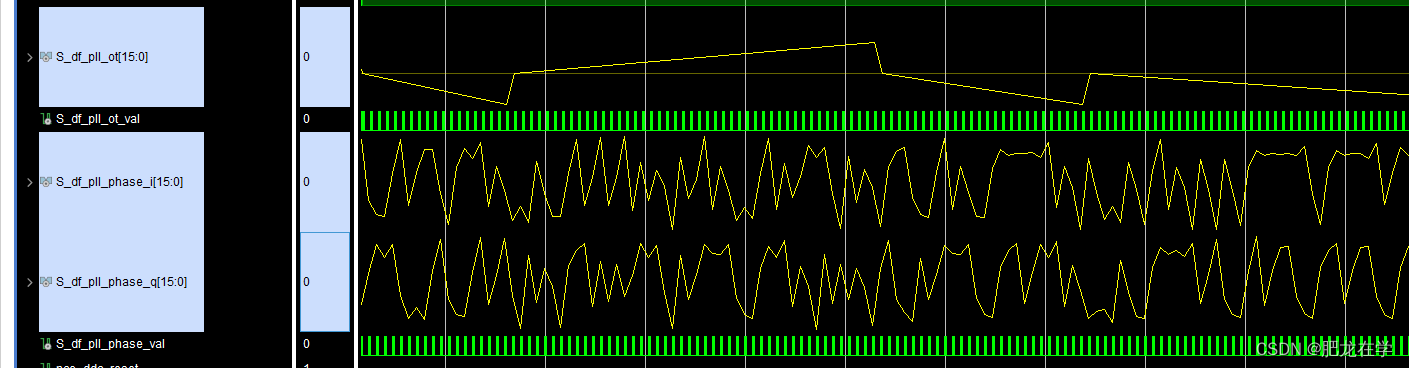

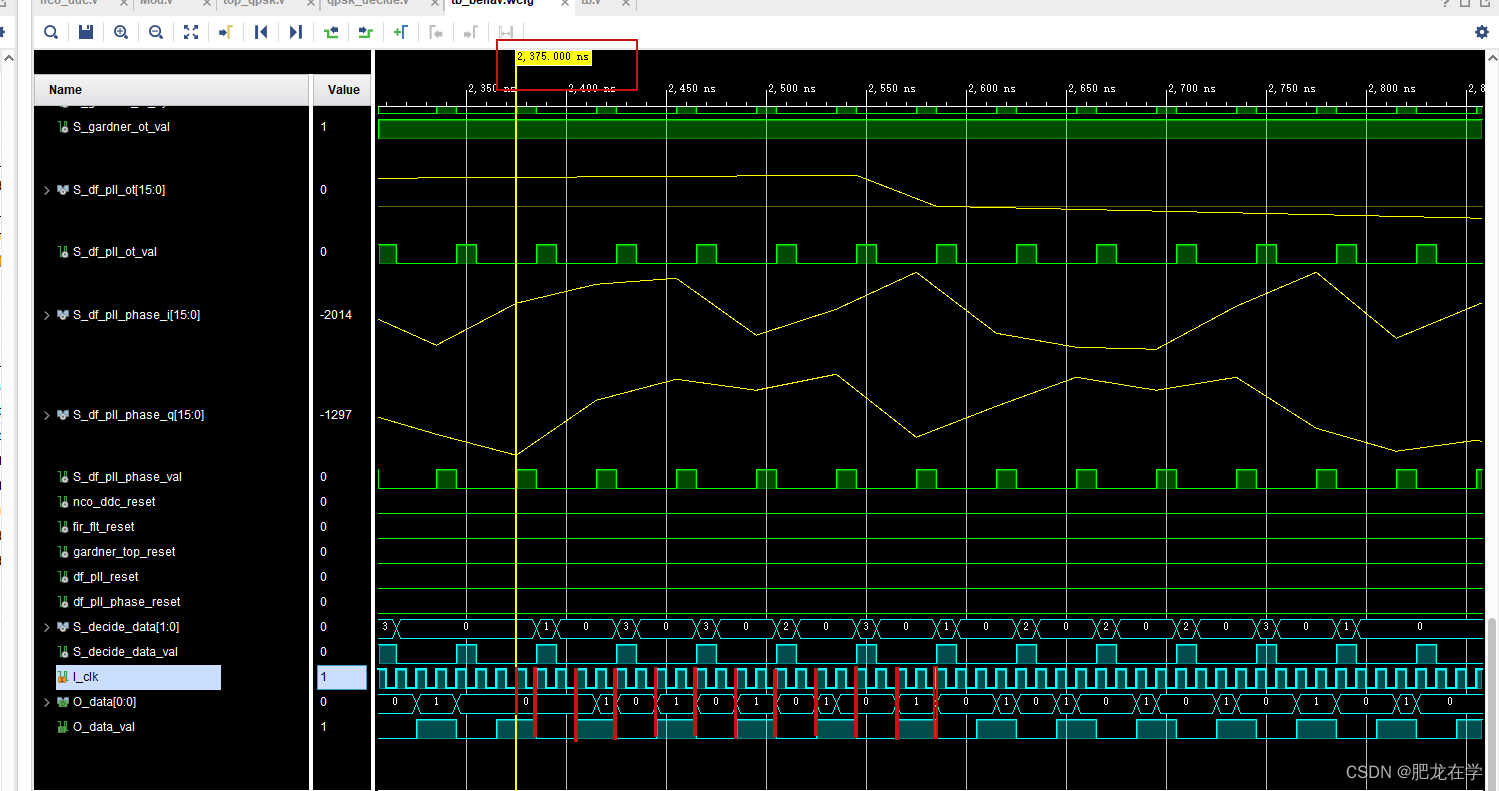

再经过载波同步以及相差恢复处理

最后经过硬判决得到解调后码元:

MATLAB星座图展示: