经历了无数的笔试面试之后,不知道大家有没有发现数字IC的笔试面试还是有很多共通之处和规律可循的。所以一定要掌握笔试面试常考的问题。

数字IC笔试面试常考问题及答案汇总(文末可领全部哦~)

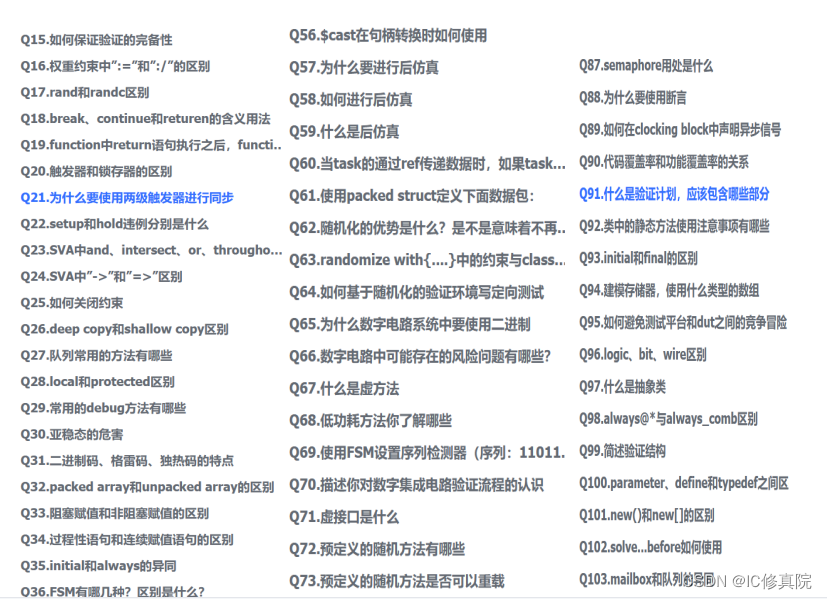

验证方向(部分题目)

Q1.定宽数组、动态数组、关联数组、队列各自的特点和使用方式。

队列:队列结合了链表和数组的优点,可以在一个队列的任何位置进行增加或者删除元素。其通过[

]

这样的符号进行申明

:

i

n

t

q

[

]这样的符号进行申明: int q[

]这样的符号进行申明:intq[],使用广泛,多应用与scoreboard;

定宽数组:属于静态数组,编译时便已经确定大小。其可以分为压缩定宽数组和非压缩定宽数组:压缩数组是定义在类型后面,名字前面;非压缩数组定义在名字后面。Bit [7:0][3:0] name压缩数组(存储空间连续); bit[7:0] name [3:0]非压缩数组(存储空间非连续);

动态数组:其内存空间在运行时才能够确定,使用前需要用new[]进行空间分配。

关联数组:其主要针对需要超大空间但又不是全部需要所有数据的时候使用,类似于hash,通过一个索引值和一个数据组成: bit [63:0] name[bit[63:0]];索引值必须是唯一的,该部分的重点要学习关联数组的遍历方法。

Q2.fork…join/fork…join_any/fork…join_none之间的异同

fork…join:内部 begin end块并行运行,直到所有线程运行完毕才会进入下一个阶段。

fork…join_any:内部 begin end块并行运行,任意一个begin end块运行结束就可以进入下一个阶段。

fork…join_none:内部 begin end块并行运行,无需等待可以直接进入下一个阶段。

Q3.mailbox、event、semaphore之间的异同

mailbox:主要用于两个线程之间的数据通信,通过put函数和 get 函数还有peek函数进行数据的发送和获取。

event:事件主要用于两个线程之间的一个同步运行,通过事件触发和事件等待进行两个线程间的运行同步。使用@(event)或者 wait(event.trigger)进行等待,->进行触发。

semaphore:旗语主要是用于对资源访问的一个交互,通过key的获取和返回实现一个线程对资源的一个访问。使用put和 get函数获取返回key。一次可以多个。

Q4.@(event_handle)和wait(event_handle.triggered)区别

@(event_handle):边沿触发,事件会一直等待,直到触发为止,阻塞型;

wait(event_handle.triggered):电平触发,如果事件在当前已经被触发,则不会引起阻塞,非阻塞型,当event被多次触发时,避免使用wait.

Q5.task和function异同区别

function:至少要有一个输入变量,一个返回值,只能运用于纯粹的数字或者逻辑运算 ;

task:可以内置常用的耗时语句,可能会被运用于需要耗时的信号采样或者驱动场景。

如果要调用function,则使用function和task均可对其调用;而如果要调用task,建议使用task来调用,这是因为如果被调用的task内置有耗时语句,则外部调用它的方法类型必须为task.

Q6.使用clocking block的好处

Interface:是一组接口,用于对信号进行一个封装,捆扎起来。如果像 verilog中对各个信号进行连接,每一层我们都需要对接口信号进行定义,若信号过多,很容易出现人为错误,而且后期的可重用性不高。因此使用interface接口进行连接,不仅可以简化代码,而且提高可重用性,除此之外,interface内部提供了其他一些功能,用于测试平台与DUT之间的同步和避免竞争。

Clocking block:在interface内部我们可以定义clocking块,可以使得信号保持同步,对于接口的采样和驱动有详细的设置操作,从而避免TB与 DUT的接口竞争,减少我们由于信号竞争导致的错误。采样提前,驱动落后,保证信号不会出现竞争。

Q7.同步FIFO和异步FIFO的作用和区别

FIFO在硬件上是一种地址依次自增的Simple Dual Port RAM,按读数据和写数据工作的时钟域是否相同分为同步FIFO和异步FIFO,其中同步FIFO是指读时钟和写时钟为同步时钟,常用于数据缓存和数据位宽转换;异步FIFO通常情况下是指读时钟和写时钟频率有差异,即由两个异步时钟驱动的FIFO,由于读写操作是独立的,故常用于多比特数据跨时钟域处理。

Q8.SystemVerilog中OOP的三大特性

类主要有三个特性:封装、继承、多态。

封装:通过将一些数据和使用这些数据的方法封装在一个集合里,成为一个类。

继承:允许通过现有类去得到一个新的类,且其可以共享现有类的属性和方法。现有类叫做基类,新类叫做派生类或扩展类。

多态:得到扩展类后,有时我们会使用基类句柄去调用扩展类对象,这时候调用的方法如何准确去判断是想要调用的方法呢?通过对类中方法进行virtual声明,这样当调用基类句柄指向扩展类时,方法会根据对象去识别,调用扩展类的方法,而不是基类中的。而基类和扩展类中方法有着同样的名字,但能够准确调用,叫做多态。

Q9.详述对于ref类型的理解

ref参数类型是引用。向子程序传递数组时应尽量使用ref获取最佳性能,如果不希望子程序改变数组的值,可以使用const ref类型。在任务里可以修改变量而且修改结果对调用它的函数随时可见。

Q10.外部约束如何使用,有哪几种方式

使用方法例示:

class Packet; rand bit [7:0] length; rand bit [7:0] payload[];

constraint c_valid {length > 0;payload.size() == length;} constraint

c_external; endclass constraint Packet::c_external {length == 1;}

//外部约束

随机化是SV中极其重要的一个知识点,通过设定随机化和相关约束,我们可以自动随机想要的数据。

权重约束 dist: 有两种操作符::=n :/n 第一种表示每一个取值权重都是n,第二种表示每一个取值权重为n/num。

条件约束 if else 和->(case): if else 就是和正常使用一样;->通过前面条件满足后可以触发后面事件的发生。

范围约束inside:inside{[min:max]};范围操作符,也可以直接使用大于小于符号进行,不可以连续使用,如 min<wxm<max 这是错误的。

前端设计方向(部分题目)

1.什么是同步逻辑和异步逻辑?

同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。

改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入 x 有无变化,状态表中的每个状态都是稳定的。异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件,电路中没有统一的时钟,电路状态的改变由外部输入的变化直接引起。

2.同步电路和异步电路的区别:

同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。

3.时序设计的实质:

时序设计的实质就是满足每一个触发器的建立/保持时间的要求。

4.建立时间与保持时间的概念?

建立时间:触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。保持时间:触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变的最小时间。

5.为什么触发器要满足建立时间和保持时间?

因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在 0 和 1 之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。

这就是为什么要用两级触发器来同步异步输入信号。这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。(比较容易理解的方式)

换个方式理解:需要建立时间是因为触发器的 D 端像一个锁存器在接受数据,为了稳定的设置前级门的状态需要一段稳定时间;需要保持时间是因为在时钟沿到来之后,触发器要通过反馈来锁存状态,从后级门传到前级门需要时间。

6.什么是亚稳态?为什么两级触发器可以防止亚稳态传播?

这也是一个异步电路同步化的问题。亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。使用两级触发器来使异步电路同步化的电路其实叫做“一位同步器”,他只能用来对一位异步信号进行同步。

两级触发器可防止亚稳态传播的原理:假 设第一级触发器的输入不满足其建立保持时间,它在第一个脉冲沿到来后输出的数据就为亚稳态,那么在下一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时 间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到来时,第二级触发器将不会出现亚稳态,因为其输入端的 数据满足其建立保持时间。同步器有效的条件:第一级触发器进入亚稳态后的恢复时间 + 第二级触发器的建立时间 < = 时钟周期。

更确切地说,输入脉冲宽度必须大于同步时钟周期与第一级触发器所需的保持时间之和。最保险的脉冲宽度是两倍同步时钟周期。所以,这样的同步电路对于从较慢的时钟域来的异步信号进入较快的时钟域比较有效,对于进入一个较慢的时钟域,则没有作用。

7.时序约束的概念和基本策略?

时序约束主要包括周期约束,偏移约束,静态时序路径约束三种。通过附加时序约束可以综合布线工具调整映射和布局布线,使设计达到时序要求。附加时序约束的一般策略是先附加全局约束,然后对快速和慢速例外路径附加专门约束。

附加全局约束时,首先定义设计的所有时钟,对各时钟域内的同步元件进行分组,对分组附加周期约束,然后对 FPGA/CPLD 输入输出 PAD 附加偏移约束、对全组合逻辑的 PAD TO PAD 路径附加约束。附加专门约束时,首先约束分组之间的路径,然后约束快、慢速例外路径和多周期路径,以及其他特殊路径。

8.锁存器(latch)和触发器(flip-flop)区别?

电平敏感的存储器件称为锁存器。可分为高电平锁存器和低电平锁存器,用于不同时钟之间的信号同步。有交叉耦合的门构成的双稳态的存储原件称为触发器。分为上升沿触发和下降沿触发。可以认为是两个不同电平敏感的锁存器串连而成。前一个锁存器决定了触发器的建立时间,后一个锁存器则决定了保持时间。

9.FPGA 芯片内有哪两种存储器资源?

FPGA 芯片内有两种存储器资源:一种叫 BLOCK RAM,另一种是由 LUT 配置成的内部存储器(也就是分布式 RAM)。BLOCK RAM 由一定数量固定大小的存储块构成的,使用 BLOCK RAM 资源不占用额外的逻辑资源,并且速度快。但是使用的时候消耗的 BLOCK RAM 资源是其块大小的整数倍。

10.什么是时钟抖动?

时钟抖动是指芯片的某一个给定点上时钟周期发生暂时性变化,也就是说时钟周期在不同的周期上可能加长或缩短。它是一个平均值为 0 的平均变量。

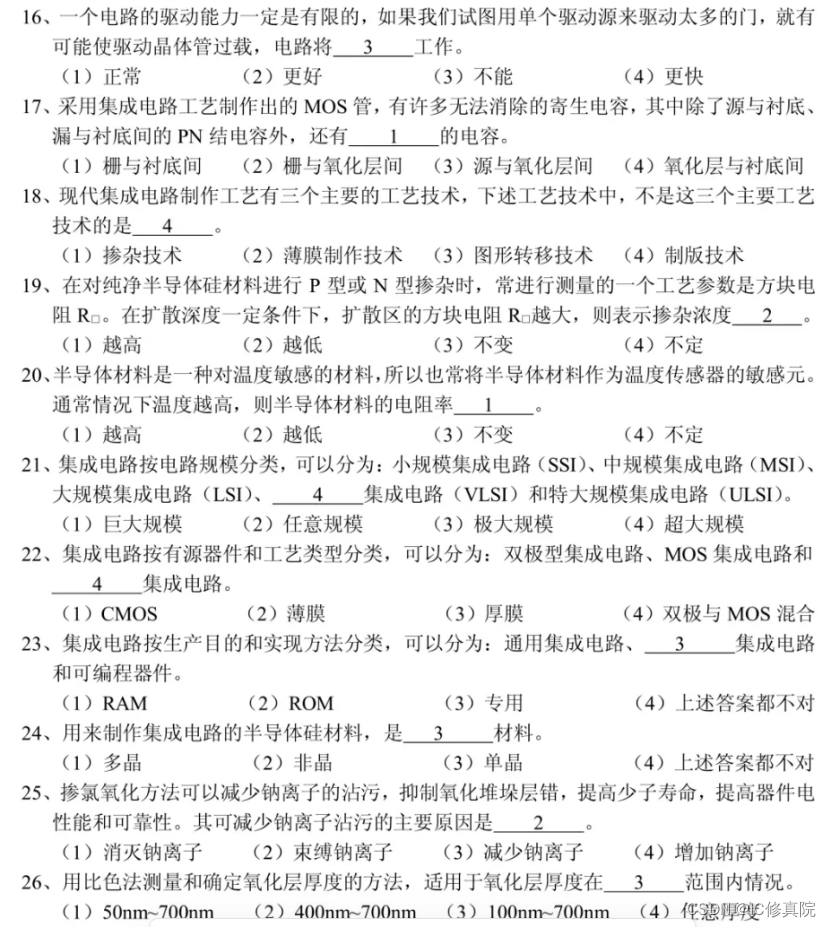

后端方向(部分题目)

• 1) Chip utilization depends on ___.

a.Only on standard cells

b.Standard cells and macros

c.Only on macros

d.Standard cells macros and IO pads

• 2) In Soft blockages ____ cells are placed.

a.Only sequential cells

b.No cells

c.Only Buffers and Inverters

d.Any cells

• 3) Why we have to remove scan chains before placement?

a.Because scan chains are group of flip flop

b.It does not have timing critical path

c.It is series of flip flop connected in FIFO

d.None

• 4) Delay between shortest path and longest path in the clock is called ____.

a.Useful skew

b.Local skew

c.Global skew

d.Slack

• 5) Cross talk can be avoided by ___.

a.Decreasing the spacing between the metal layers

b.Shielding the nets

c.Using lower metal layers

d.Using long nets

请列举一下导入后端设计需要哪些文件?

此题经常容易被作为笔试题,考察学生的时序基础理解能力 本质上,standard cell delay 由 cell 的 input transition 和 output load 决定 PVT作为外部条件,也会影响到 cell 的 delay。应该理解到 PVT 与 delay 的关 系是怎么样? 建议: 比较全面的回答是在同一种 PVT 条件下,cell delay 由 inputtransition 和 output load 决定

请列举几个你知道的sdc命令,并说出它的用途?

回顾常见的sdc命令:描述芯片的工作速度,即时钟的频率,包括 create_clock,create_generated_clock 等

描述芯片的边界约束,包括 set_input_delay,set_output_delay 等描述芯片的一些设计违反 rule(DRV),包括 set_max_fanout,set_max_capacitance, set_max_transition 等

描述设计中一些特殊的路径,包括 set_false_path, set_multicycle_path 等

描述设计中一些需要禁止的timing arc,例如 set_disable_timing

请说一下 drv 的概念,主要包含哪些内容?

Max transition, max capacitance, max fanout 为什么优先修复,课上提过多次,需要记牢 可以特意和面试官指出:max fanout 不需要修复

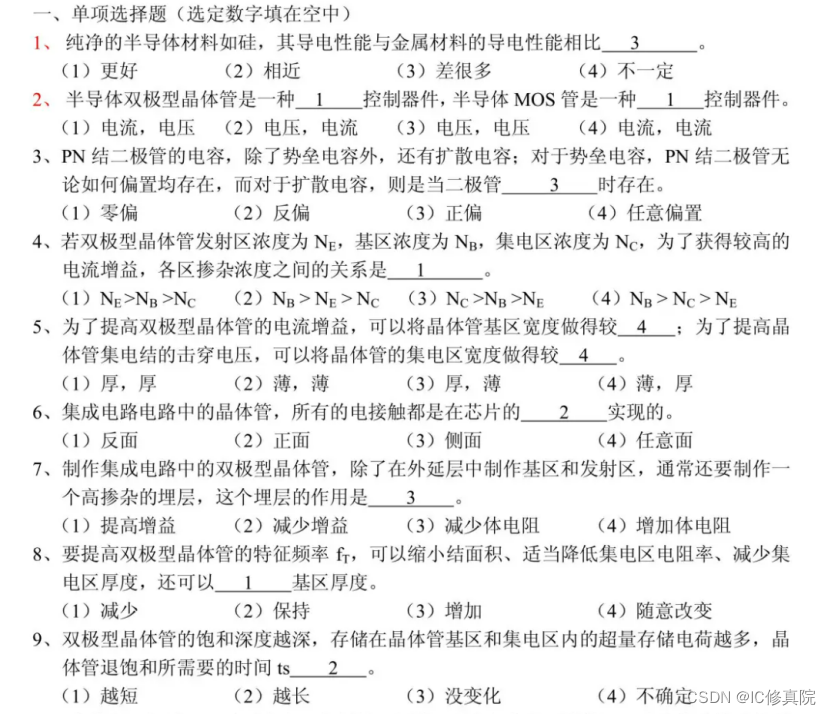

版图方向(部分题目)

IC笔试面试经验(26家大厂)

由于篇幅限制,就不一一更新所有题目了,以上都可以分享大家。如果需要那个方向的笔面试题目,可按需领~

这里放一个口:IC笔面试题目

![[NOIP2000 提高组] 进制转换](https://img-blog.csdnimg.cn/a6f2e458ea224d3fa9990dec5727f95d.png)